# MARINE CORPS TECHNICAL MANUAL

# RADIO RECEIVING SET AN/GRR-17

OPERATION AND MAINTENANCE

# TM-05866A-15

# U.S. MARINE CORPS TECHNICAL MANUAL

# RADIO RECEIVING SET AN/GRR-17

OPERATION AND MAINTENANCE

### DEPARTMENT OF THE NAVY Headquarters U.S. Marine Corps Washington, D. C. 20380

30 September 1968

- 1. This Manual is effective upon receipt and contains information on the operation and maintenance of the Radio Receiving Set, AN/GRR-17.

- 2. Notice of discrepancies and suggested changes to this Manual should be forwarded to the Commandant of the Marine Corps (Code CSY).

BY DIRECTION OF THE COMMANDANT OF THE MARINE CORPS

OFFICIAL

N. J. DENNIS

Colonel, U.S. Marine Corps Director, Technical Division

Supply Department

DISTRIBUTION: 6900-02/7230-01 (8)

7800-06 (5)

5138-01, -02, -03, -14 (4)

5138-05, -06, -12, -13/5139/5145/5514/5551/6025/

7000-46, -161 (3)

2030/2108/2112/2116/2157-12, -13, -14/2297/3700-04/4106/5040/5138-09, -10, -11/5275/5280/5290/5308/5453/5480/5485/5486/5515/5521/5523/6600/7950 (2) 4033/4045/4047/4065/4070/4090/4135/4145/4150/4155/4160/4180/4185/4225/5029/5045/5506/5509/

5512/6900-01, -04 (1)

### LIST OF EFFECTIVE PAGES

| PAGE<br>NUMBER                               | ISSUE                                        | PAGE<br>NUMBER                                    | ISSUE                            |

|----------------------------------------------|----------------------------------------------|---------------------------------------------------|----------------------------------|

| Title i thru xiii 1-0 thru 1-6 2-1 thru 2-12 | Original<br>Original<br>Original<br>Original | 3-1 thru 3-16<br>4-1 thru 4-170<br>5-1 thru 5-150 | Original<br>Original<br>Original |

# RECORD OF CHANGES

| CHANGE<br>NO. | DATE<br>ENTERED | TITLE OR BRIEF<br>DESCRIPTION | ENTERED BY<br>(SIG - RANK) |

|---------------|-----------------|-------------------------------|----------------------------|

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               | ·               |                               |                            |

|               |                 |                               |                            |

|               |                 |                               |                            |

|               |                 |                               | ·                          |

|               |                 |                               |                            |

|               |                 |                               |                            |

#### SAFETY SUMMARY

LISTED BELOW IS EVERY "WARNING" CONTAINED IN THIS MANUAL AND THE PAGE ON WHICH THE "WARNING" IS LOCATED. ALL PERSONNEL INVOLVED IN THE OPERATION AND MAINTENANCE OF THIS EQUIPMENT MUST FULLY UNDERSTAND THE "WARNING" AND THE PROCEDURE BY WHICH THE HAZARD IS TO BE REDUCED OR ELIMINATED. PERSONNEL SHALL BECOME THOROUGHLY FAMILIAR WITH ALL ASPECTS OF SAFETY OF PERSONNEL AND EQUIPMENT PRIOR TO THE OPERATION AND MAINTENANCE OF THE EQUIPMENT.

- 1. Potentials as high as 125 volts are present in the power supply circuits. Avoid contact. (Pages 4-15, 4-22, 4-141, and 4-144.)

- 2. Remove primary power from equipment before attempting module removal, replacement, or any repair technique. (Page 5-22.)

- 3. Transit Case C43611-Gl is equipped with a pressure relief valve to permit safe transportation by aircraft. Valve MUST be opened (turned fully counterclockwise) prior to shipment, whether set is packed or unpacked. (Pages 1-5 and 2-11.)

ii

#### TABLE OF CONTENTS

| SECTION 1. | GENERAL     | SECTION 2. | INSTALLATION |

|------------|-------------|------------|--------------|

|            | INFORMATION |            | CONT'D       |

| PARA                                                                    | PAGE  | PARA                                                                                      | PAGE |

|-------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------|------|

| 1-1 Introduction                                                        | 1-1   | a. General                                                                                | 2-7  |

| 1-2 Functional Description                                              | 1-1   | b. Initially Energizing Receiver                                                          | 2-7  |

| 1-3 Quick Reference Data                                                | 1-2   | c. Tuning Performance                                                                     | 2-8  |

| a. General                                                              | 1-2   | d. AM Mode Operation                                                                      | 2-9  |

| b. Functional Characteristics                                           | 1-2   | e. CW Mode Operation                                                                      | 2-9  |

| 1-4 Equipment Lists                                                     | 1-4   | f. FSK Mode Operation                                                                     | 2-9  |

| a. Equipment Supplied                                                   | 1-4   | g. Monitoring with Headphones                                                             | 2-10 |

| <ul><li>b. Equipment Required but<br/>Not Supplied</li></ul>            | 1-4   | <ul><li>h. Operation of Special Circuits</li><li>i. Operation with Other Equip-</li></ul> | 2-10 |

| c. Shipping Data                                                        | 1-4   | ment with other Equip-                                                                    | 2-11 |

| SECTION 2. INSTALLATION                                                 |       | 2-6 Preparation for Reshipment                                                            | 2-11 |

|                                                                         |       | a. Equipment Disassembly                                                                  | 2-11 |

| 2-1 Unpacking and Handling                                              | 2-1   | b. Repackaging                                                                            | 2-11 |

| <ul> <li>a. Description of Packaging<br/>and Packing Methods</li> </ul> | 2-1   | SECTION 3. OPERATION                                                                      |      |

| b. Unpacking Instructions                                               | 2-1   | 3-1 Functional Operation                                                                  | 3-1  |

| c. Handling                                                             | 2-1   | 3-2 Operating Procedures                                                                  | 3-1  |

| d. Transit Case Valve                                                   | 2-1   | a. Description of Controls                                                                | 3-1  |

| e. Mechanical Inspection                                                | 2-2   | b. Modes of Operation                                                                     | 3-1  |

| 2-2 Power Requirements and<br>Distribution                              | 2-2   | c. Sequence of Operation                                                                  | 3-1  |

| a. Requirements                                                         | 2-2   | d. Indicator Presentations                                                                | 3-8  |

| b. Primary Power Connections                                            | 2-2   | e. Nonoperating Controls                                                                  | 3-9  |

| c. Distribution                                                         | 2-2   | 3-3 Summary of Operation                                                                  | 3-9  |

| 2-3 Installation Layout                                                 | 2-3   | 3-4 Emergency Operation                                                                   | 3-9  |

| a. Power Source                                                         | 2-3   | a. Partial Failure                                                                        | 3-9  |

| b. Cable Lengths                                                        | 2-3   | b. Other Than Normal                                                                      | 3-11 |

| c. Service Access                                                       | 2-3   | c. Jamming                                                                                | 3-12 |

| d. Temperature and Ventilation                                          | n 2-3 | 3-5 Operator's Maintenance                                                                | 3-13 |

| e. Interaction with Other                                               |       | a. General                                                                                | 3-13 |

| Equipment                                                               | 2-3   | b. Operating Checks                                                                       | 3-13 |

| f. Operation with Auxiliary Equipment                                   | 2-3   | c. Preventive Maintenance                                                                 | 3-14 |

| 2-4 Installation Requirements                                           | 2-3   | d. Emergency Maintenance                                                                  | 3-14 |

| a. Removing and Replacing                                               | 2-3   | SECTION 4. TROUBLE SHOOTING                                                               |      |

| the Transit Case                                                        | 2-5   | 4-1 Introduction                                                                          | 4-1  |

| b. Relay Rack Installation                                              | 2-5   | 4-2 Logical Trouble Shooting                                                              | 4-1  |

| c. External Cables                                                      | 2-5   | a. Symptom Recognition                                                                    | 4-1  |

| d. Making External Connection                                           |       | b. Symptom Investigation                                                                  | 4-1  |

| 2-5 Initial Operating Tests                                             | 2-7   | -                                                                                         |      |

ORIGINAL

SECTION 4. TROUBLE SHOOTING CONT'D SECTION 4. TROUBLE SHOOTING CONT'D

|     | OOM D                                           |      | CONTD                                   |      |

|-----|-------------------------------------------------|------|-----------------------------------------|------|

| PA. | RA                                              | PAGE | PARA                                    | PAGE |

|     | c. Probable Faulty Section                      | 4-1  | 4-9 Noise Blanker AlA2A4                | 4-29 |

|     | d. Localizing the Faulty Section                | 4-2  | a. Description                          | 4-29 |

|     | e. Isolating the Faulty Com-                    |      | b. Preliminary Check                    | 4-30 |

|     | ponent                                          | 4-2  | c. Test Equipment                       | 4-30 |

|     | f. Faulty Analysis                              | 4-2  | d. Control Settings                     | 4-30 |

|     | g. Use of Card Extension                        | 4-3  | e. Test Data                            | 4-30 |

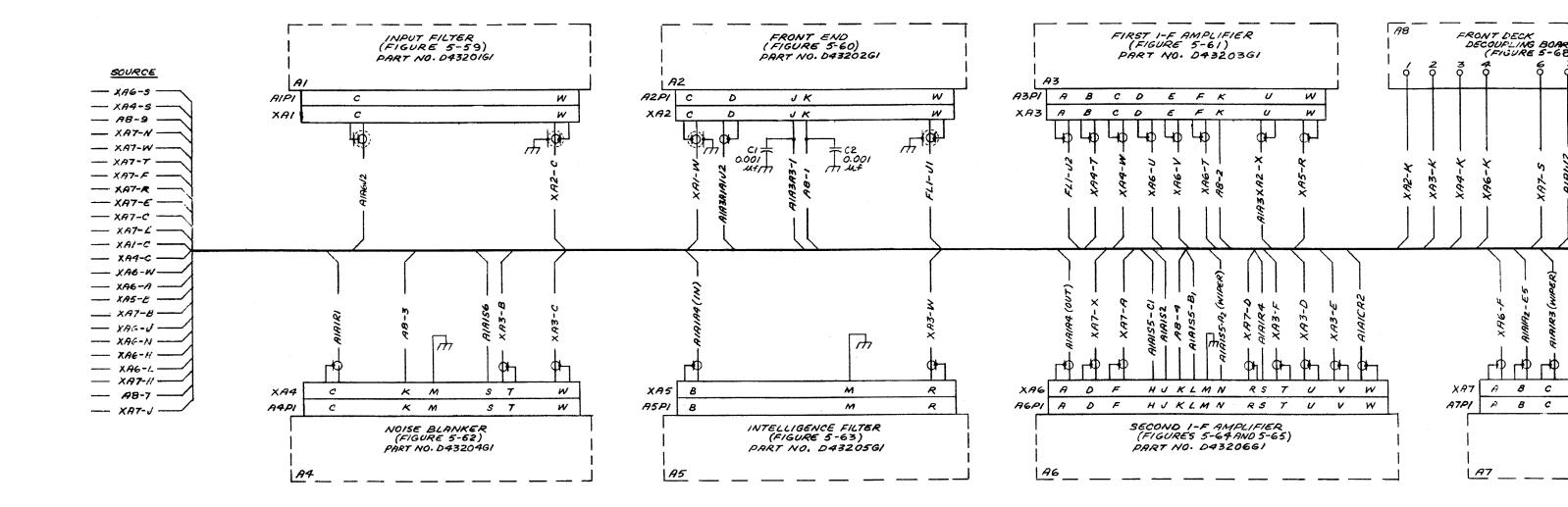

| 4-3 | Over-All Functional Description                 | 4-3  | 4-10 Intelligence Filter AlA2A5         | 4-35 |

|     | a. General                                      | 4-3  | a. Description                          | 4-35 |

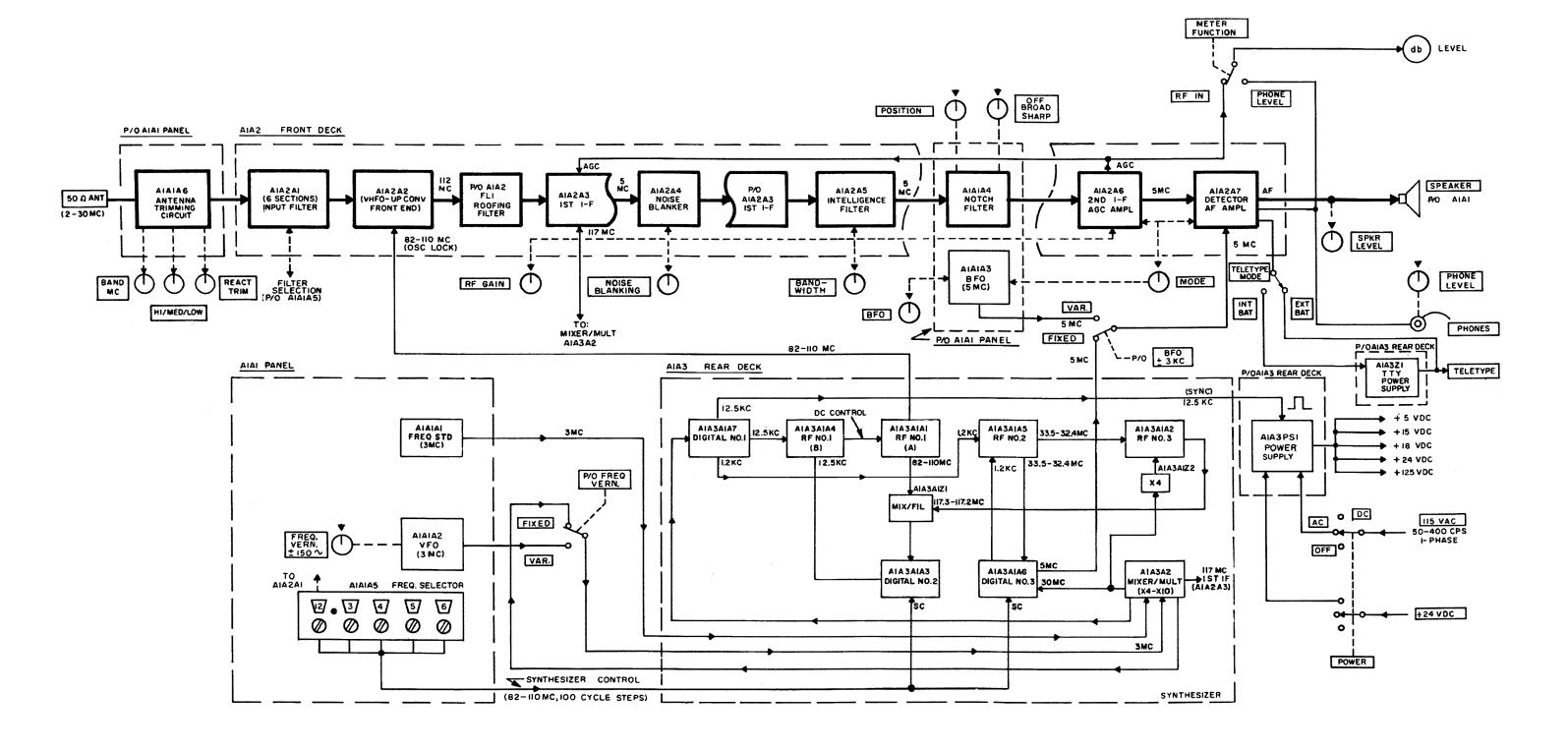

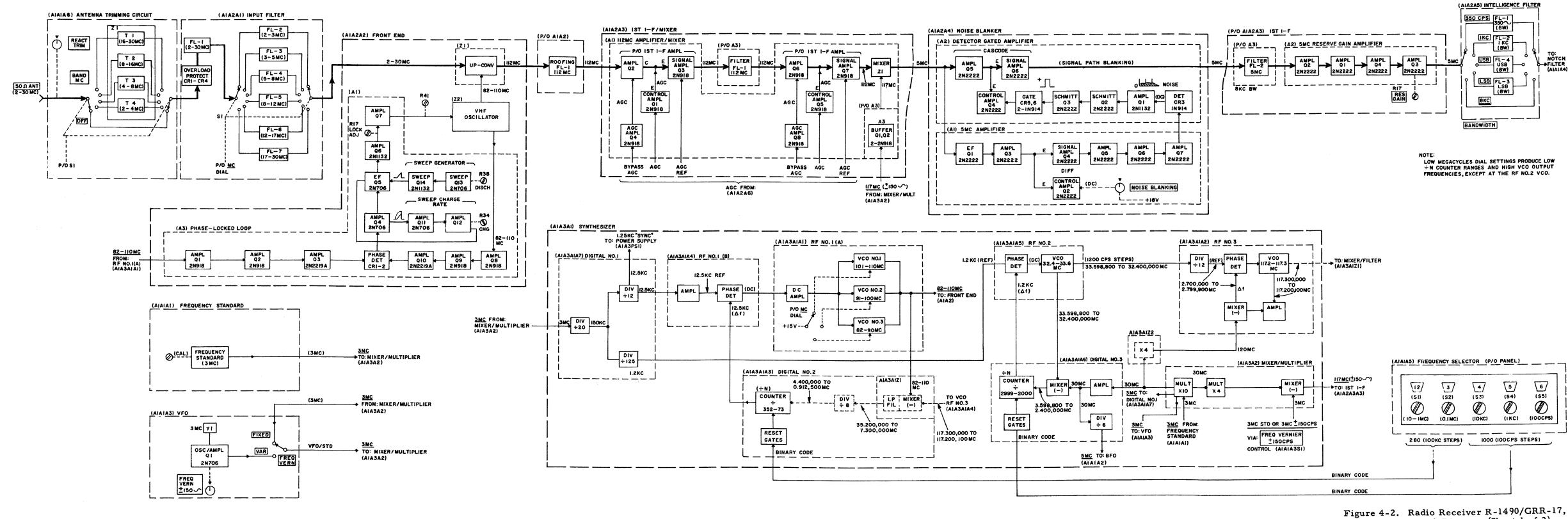

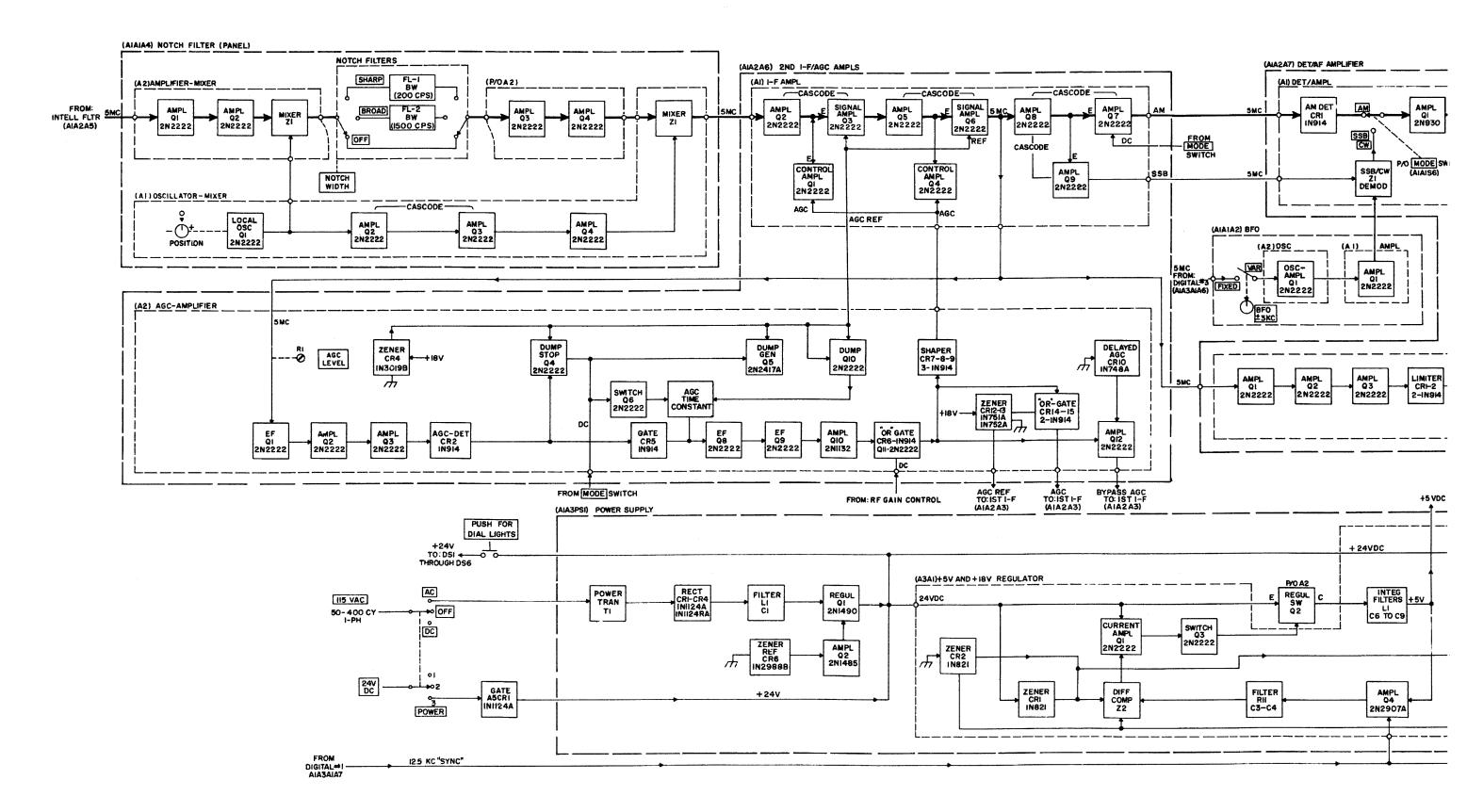

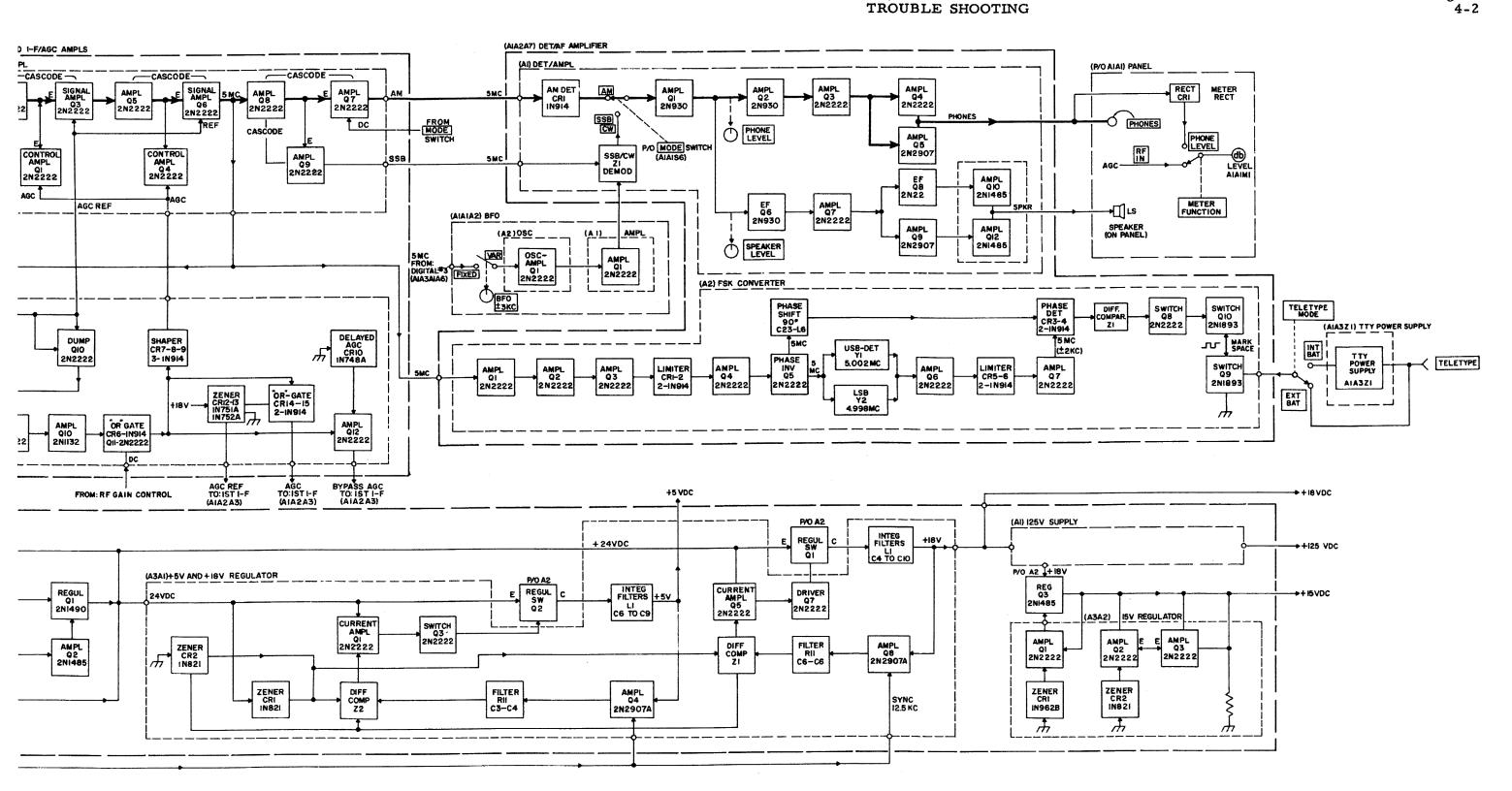

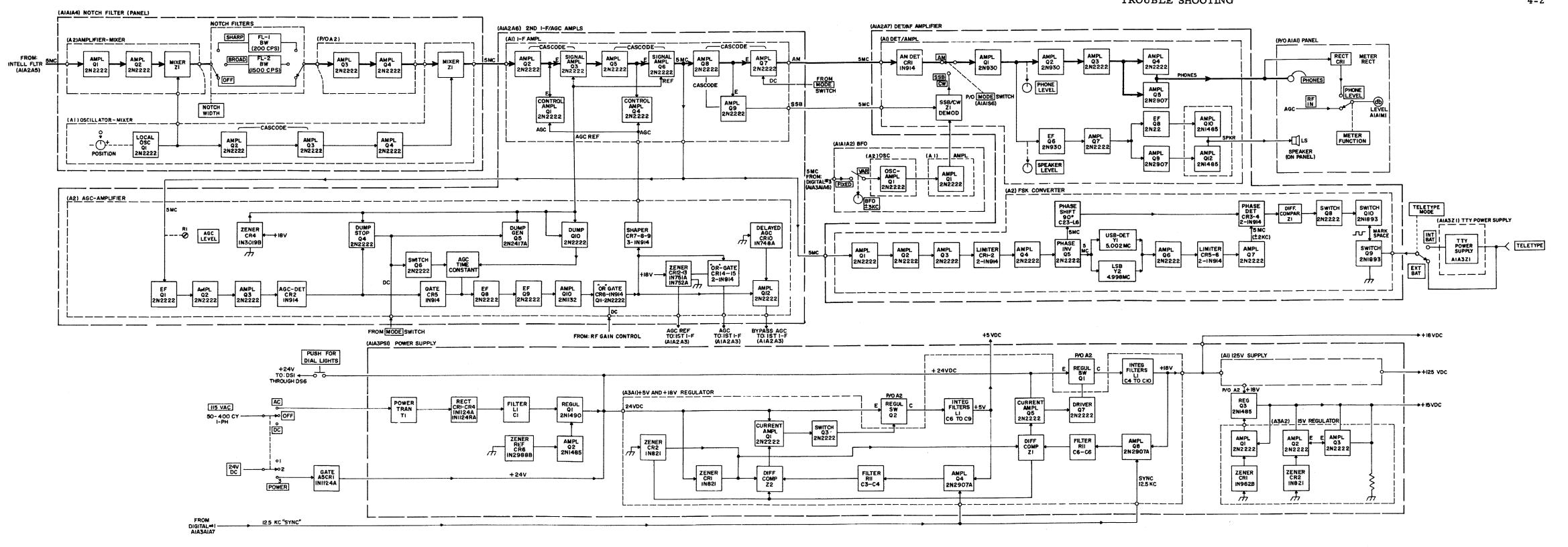

|     | b. Basic Block Diagram                          | 4-4  | b. Preliminary Check                    | 4-35 |

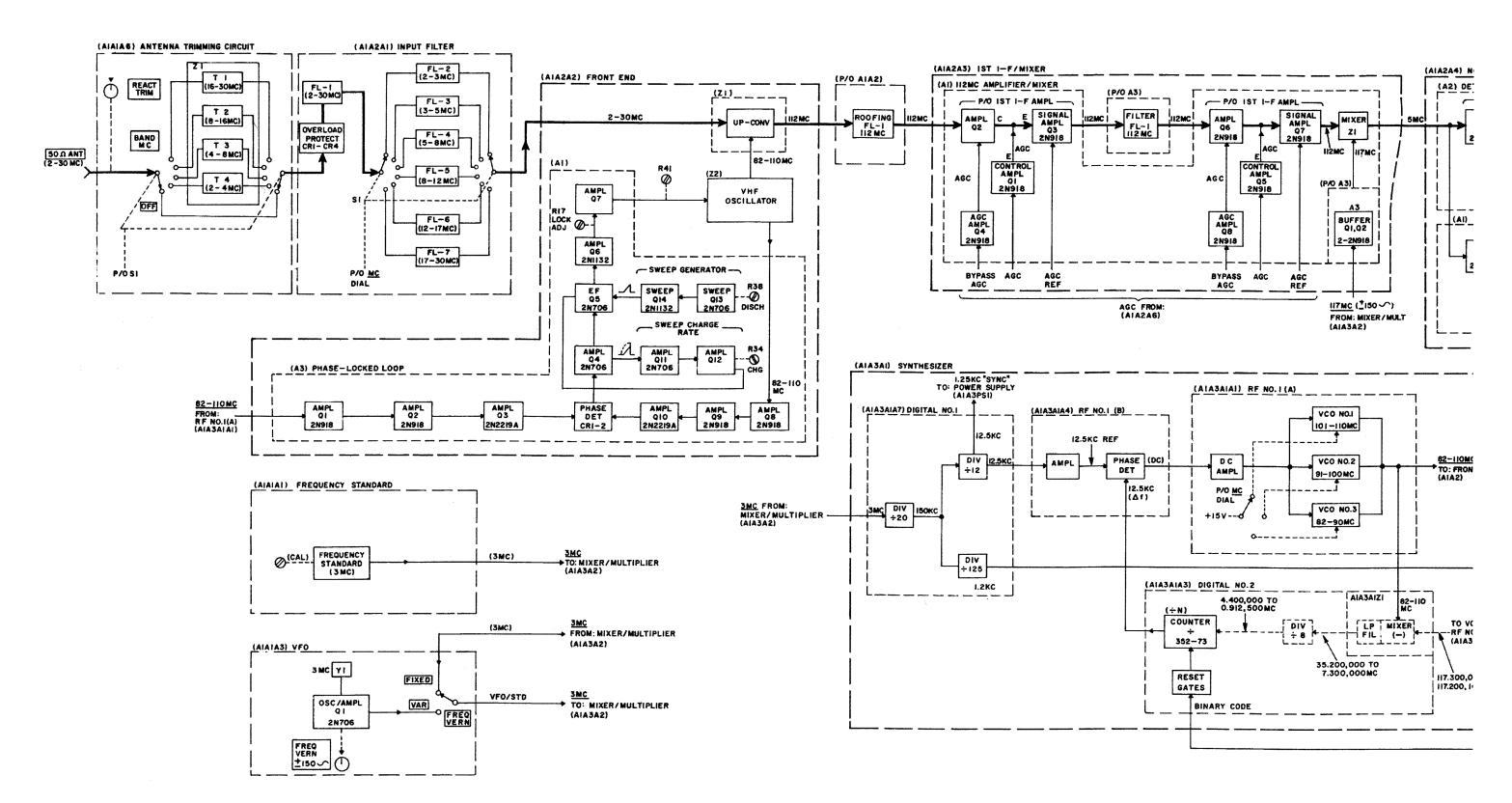

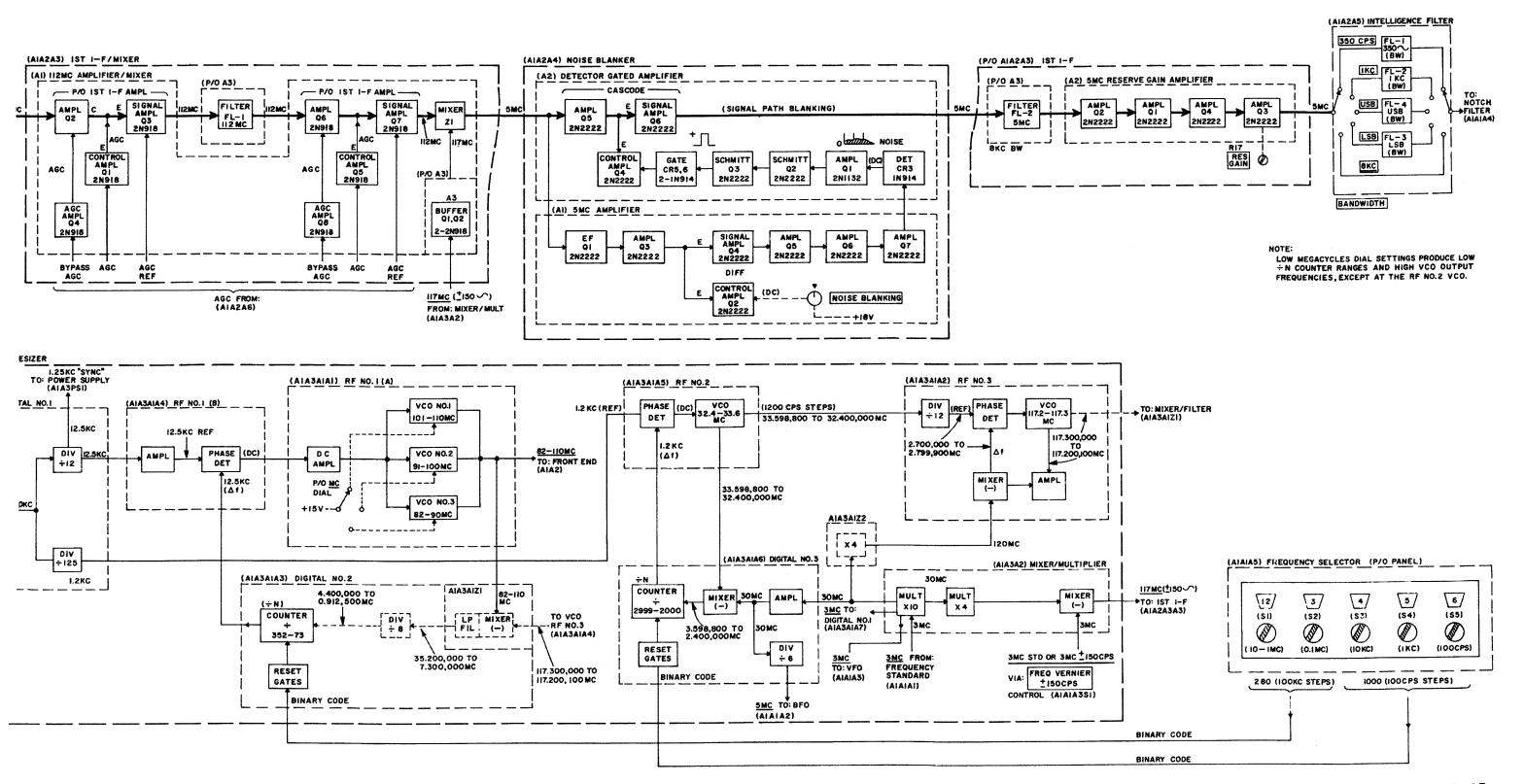

|     | c. Functional Block Diagram                     | 4-7  | c. Test Equipment                       | 4-35 |

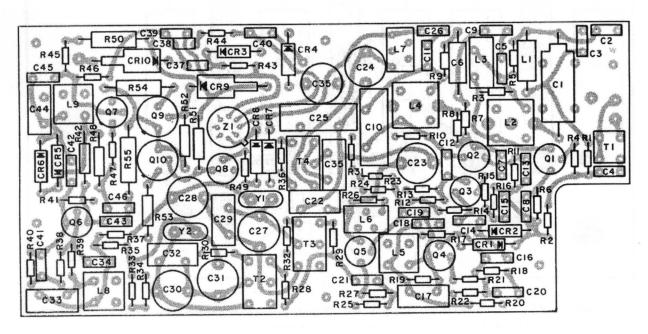

| 4-4 | Module Circuit Description and Trouble Shooting | 4-14 | d. Control Settings                     | 4-35 |

|     | a. Circuit Description                          | 4-14 | e. Test Data                            | 4-35 |

|     | b. Trouble Shooting                             | 4-14 | 4-11 Notch Filter AlAlA4                | 4-37 |

|     | c. References                                   | 4-14 | a. Description                          | 4-37 |

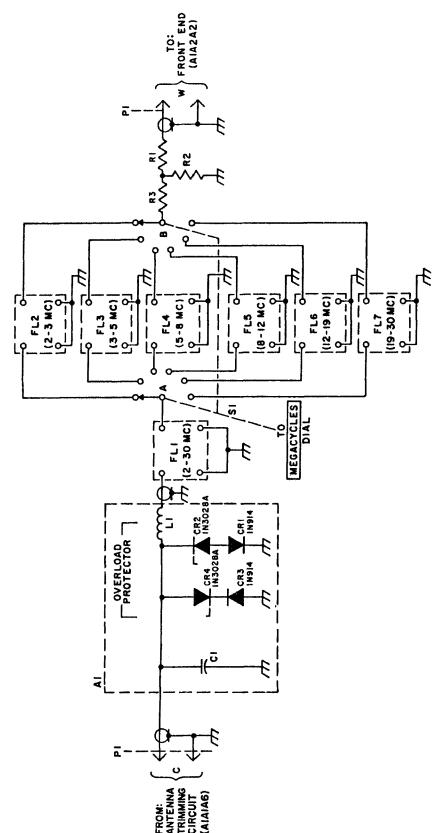

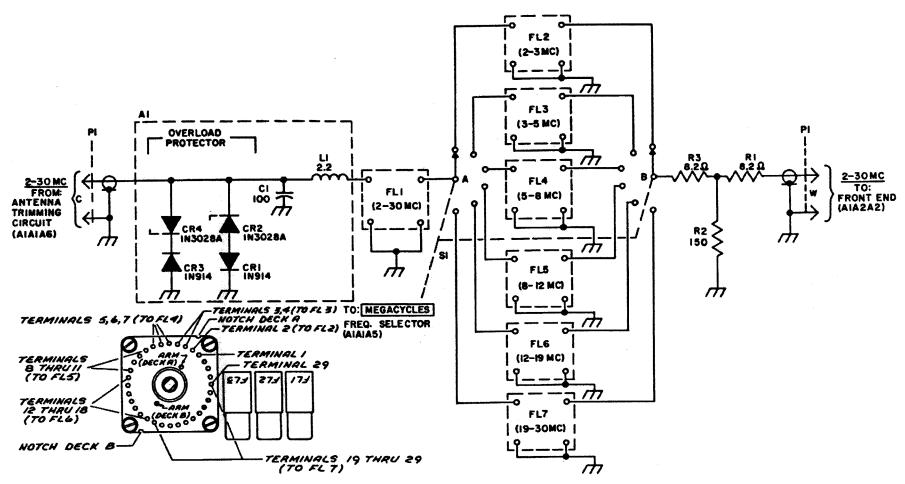

| 4-5 | Input Filter AlA2Al                             | 4-14 | b. Preliminary Check                    | 4-43 |

|     | a. Description                                  | 4-15 | c. Test Equipment                       | 4-43 |

|     | b. Preliminary Check                            | 4-15 | d. Control Settings                     | 4-43 |

|     | c. Test Equipment                               | 4-15 | e. Test Data                            | 4-43 |

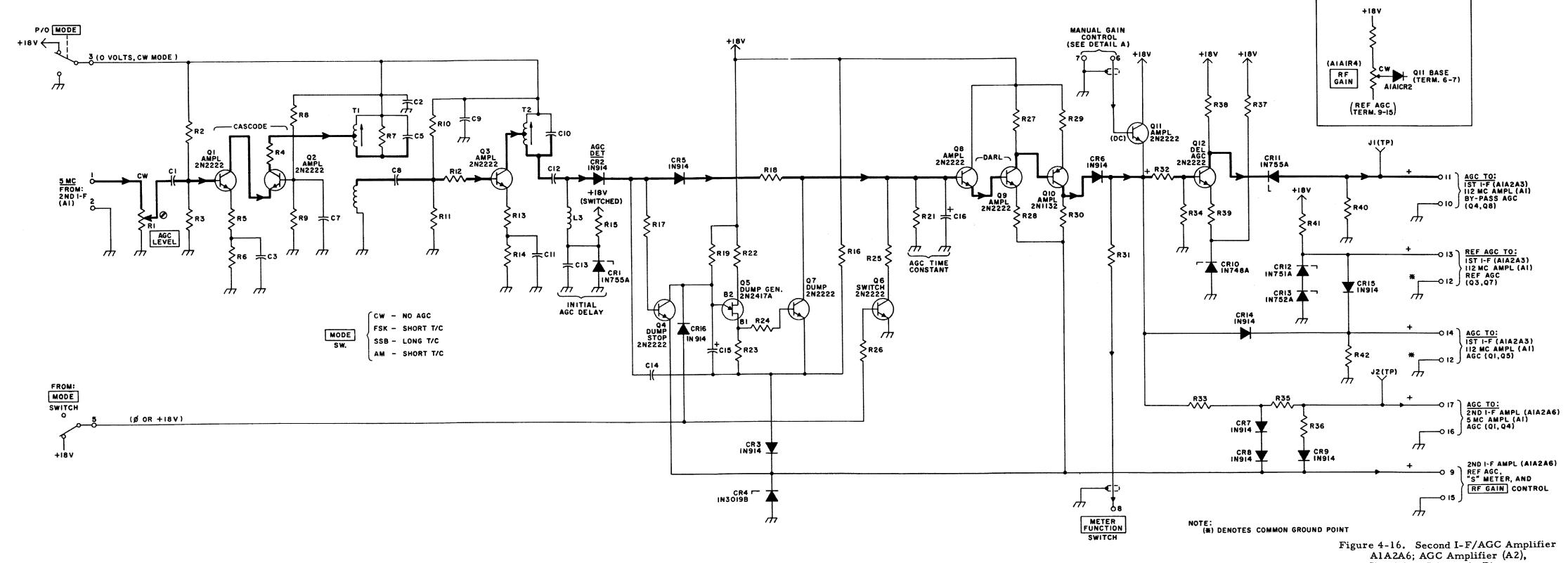

|     | d. Control Settings                             | 4-15 | 4-12 Second I-F/AGC Amplifier<br>AlA2A6 | 4-44 |

|     | e. Test Data                                    | 4-15 | a. Description                          | 4-44 |

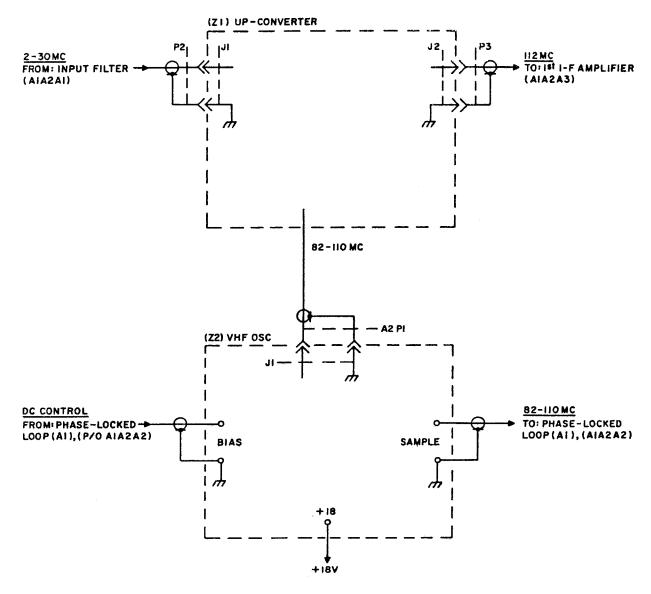

| 4-6 | Front End AlA2A2                                | 4-17 | b. Preliminary Check                    | 4-51 |

|     | a. Description                                  | 4-17 | c. Test Equipment                       | 4-51 |

|     | b. Preliminary Check                            | 4-22 | d. Control Settings                     | 4-51 |

|     | c. Test Equipment                               | 4-22 | e. Test Data                            | 4-52 |

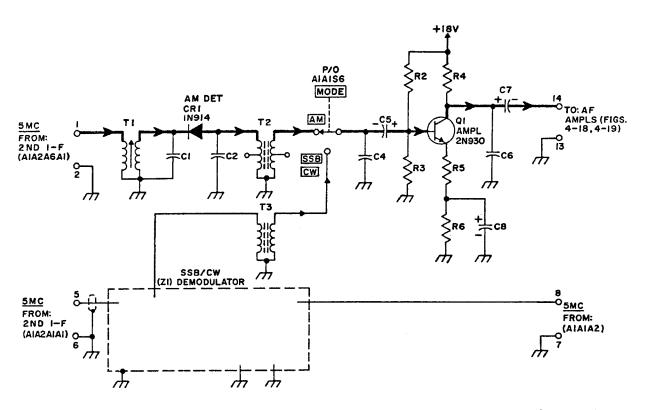

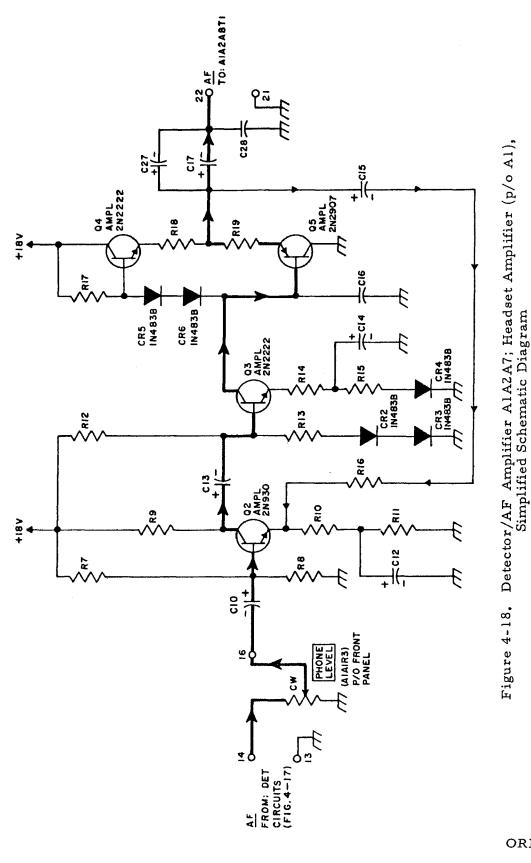

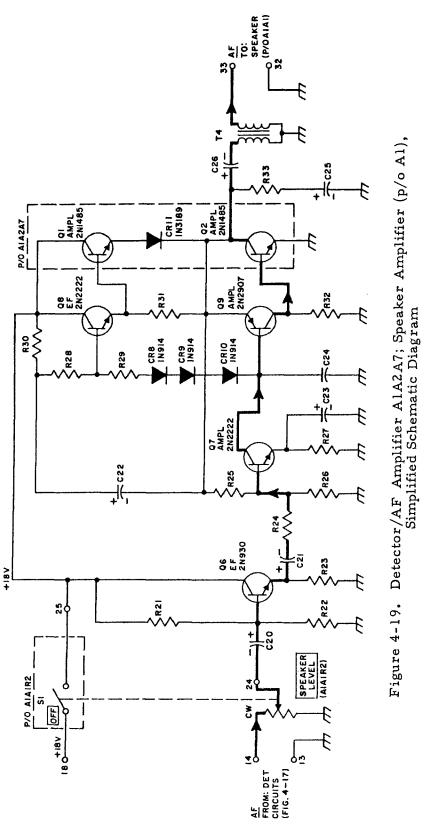

|     | d. Control Settings                             | 4-22 | 4-13 Detector/AF Amplifier A1A2A7       | 4-52 |

|     | e. Test Data                                    | 4-22 | a. Description                          | 4-52 |

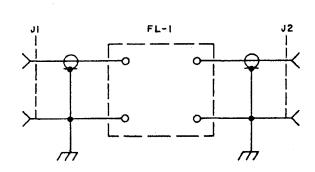

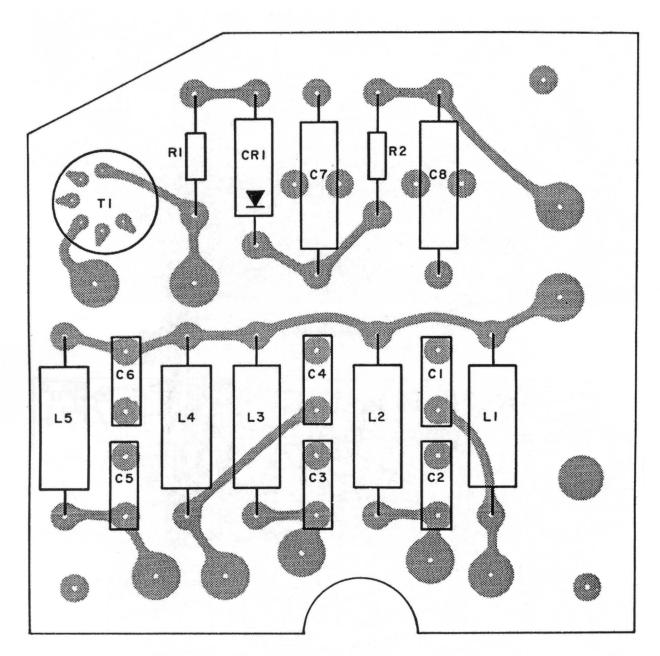

| 4-7 | Roofing Filter AlA2FL1                          | 4-23 | b. Preliminary Check                    | 4-62 |

|     | a. Description                                  | 4-23 | c. Test Equipment                       | 4-62 |

|     | b. Preliminary Check                            | 4-23 | d. Control Settings                     | 4-62 |

|     | c. Test Data                                    | 4-23 | e. Test Data                            | 4-62 |

| 4-8 | First I-F Module A1A2A3                         | 4-23 | 4-14 BFO Module AlAlA2                  | 4-63 |

|     | a. Description                                  | 4-23 | a. Description                          | 4-63 |

|     | b. Preliminary Check                            | 4-28 | b. Preliminary Check                    | 4-65 |

|     | c. Test Equipment                               | 4-28 | c. Test Equipment                       | 4-65 |

|     | d. Control Settings                             | 4-28 | d. Control Settings                     | 4-65 |

|     | e. Test Data                                    | 4-28 | e. Test Data                            | 4-65 |

|     |                                                 |      |                                         |      |

iv ORIGINAL

| SECTION 4. TROUBLE SHOOTING CONT'D           |       | SECTION 4. IROUBLE SHOOTING CONT'D |       |

|----------------------------------------------|-------|------------------------------------|-------|

| PARA                                         | PAGE  | PARA                               | PAGE  |

| 4-15 Frequency Standard AlAlAl               | 4-65  | d. Control Settings                | 4-95  |

| a. Description                               | 4-65  | e. Test Data                       | 4-95  |

| b. Preliminary Check                         | 4-65  | 4-21 Digital #2, A1A3A1A3          | 4-95  |

| c. Test Equipment                            | 4-65  | a. Description                     | 4-95  |

| d. Test Data                                 | 4-66  | b. Preliminary Check               | 4-105 |

| 4-16 VFO Module AlAlA3                       | 4-66  | c. Test Equipment                  | 4-106 |

| a. Description                               | 4-66  | d. Control Settings                | 4-106 |

| b. Preliminary Check                         | 4-67  | e. Test Data                       | 4-106 |

| c. Test Equipment                            | 4-67  | 4-22 RF #3, A1A3A1A2               | 4-106 |

| d. Control Settings                          | 4-67  | a. Description                     | 4-106 |

| e. Test Data                                 | 4-67  | b. Preliminary Check               | 4-111 |

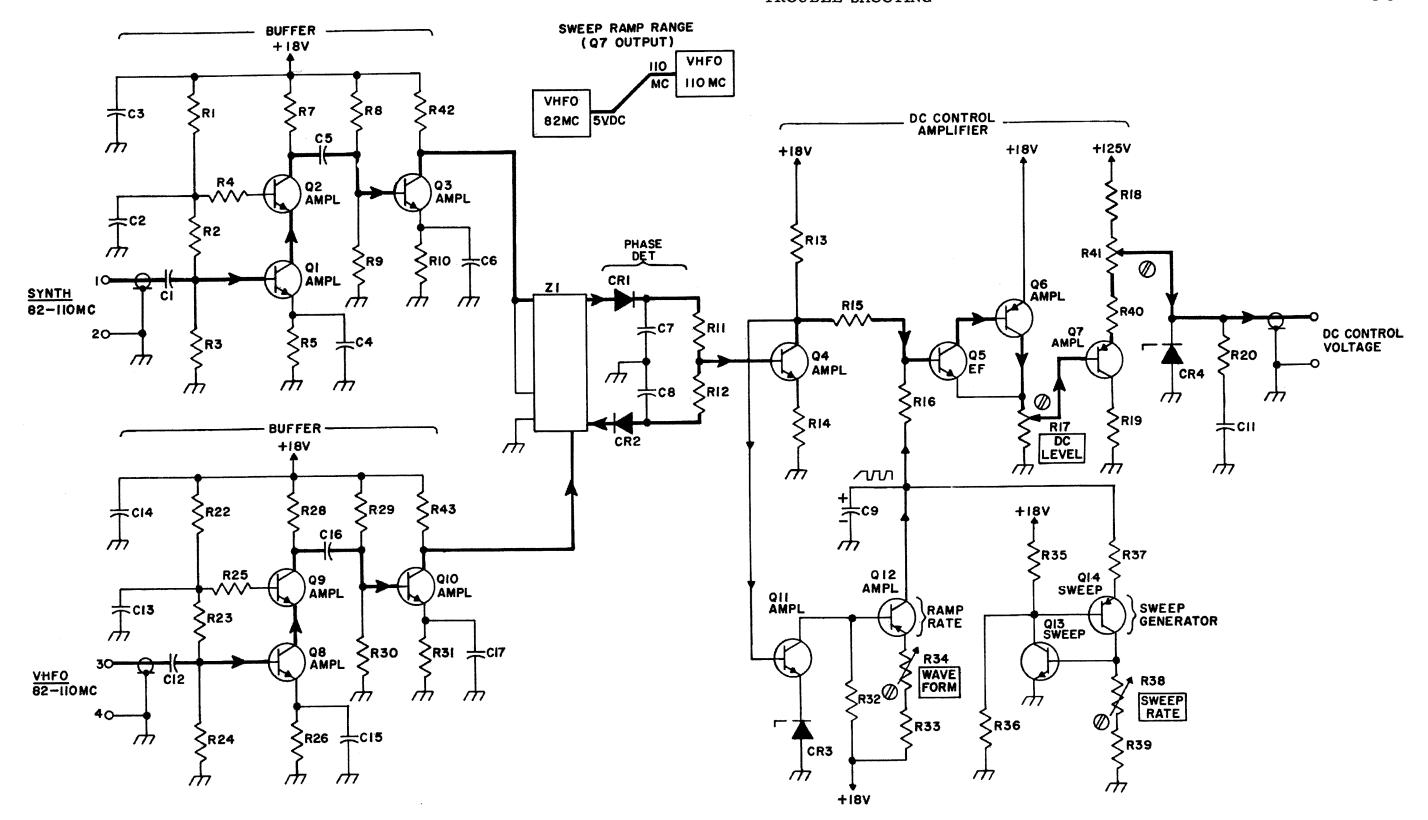

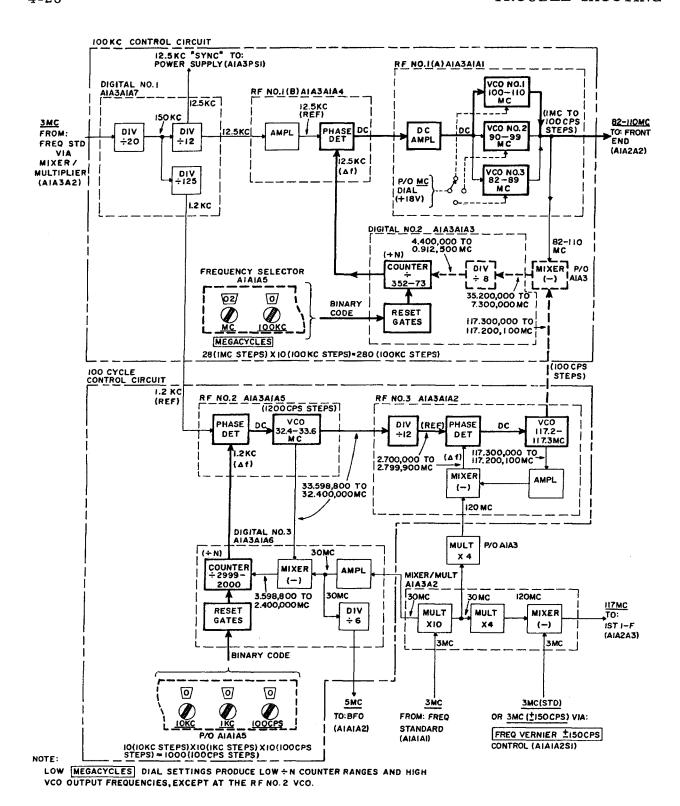

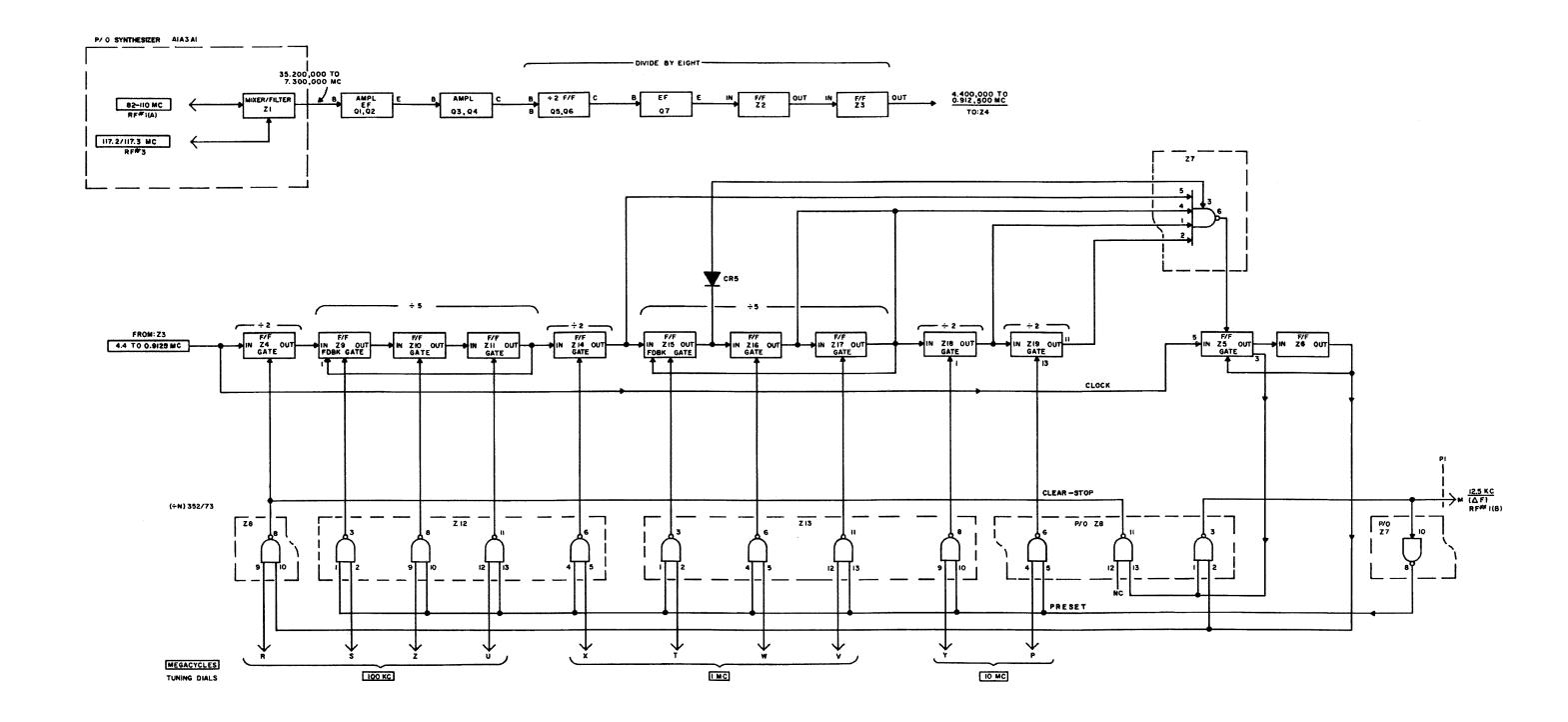

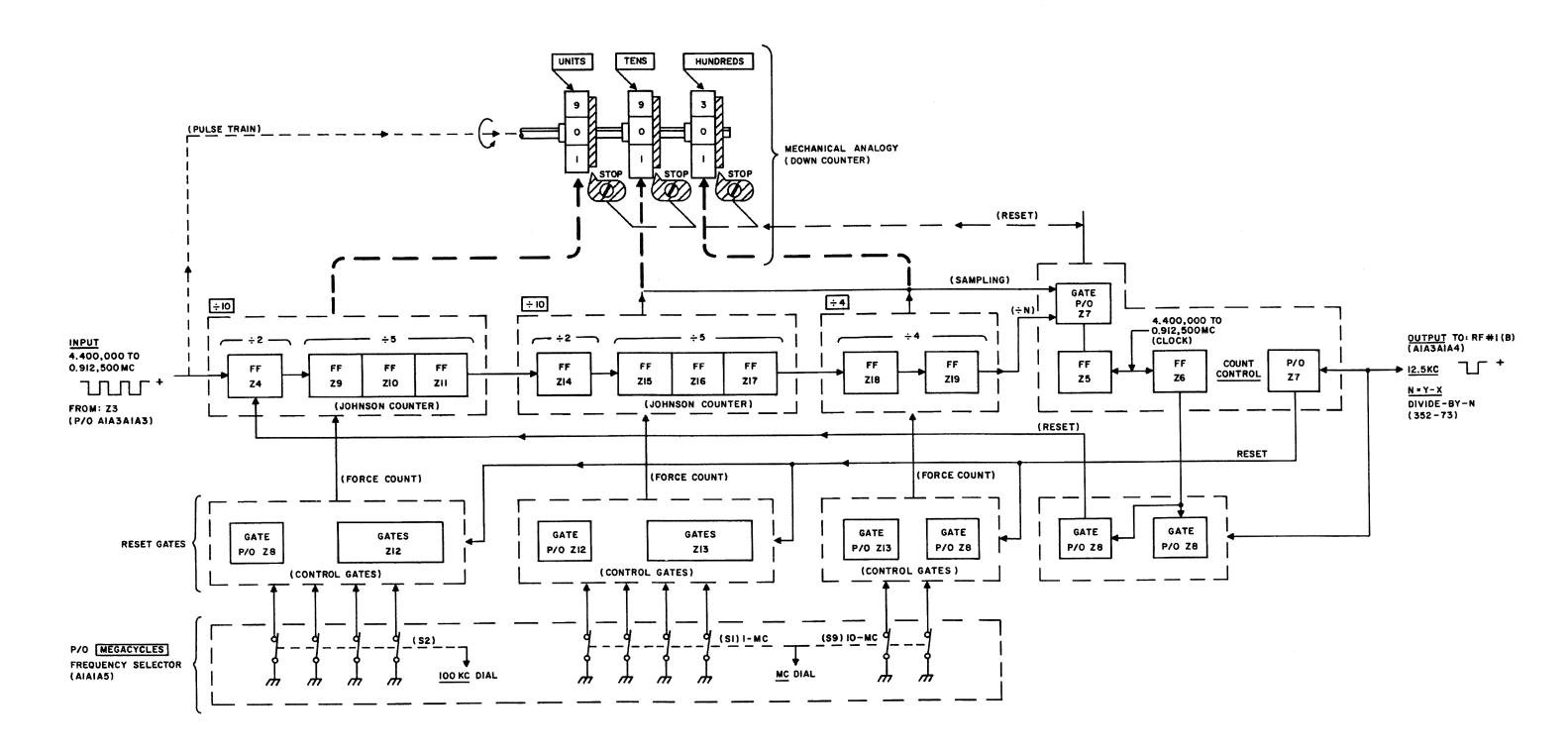

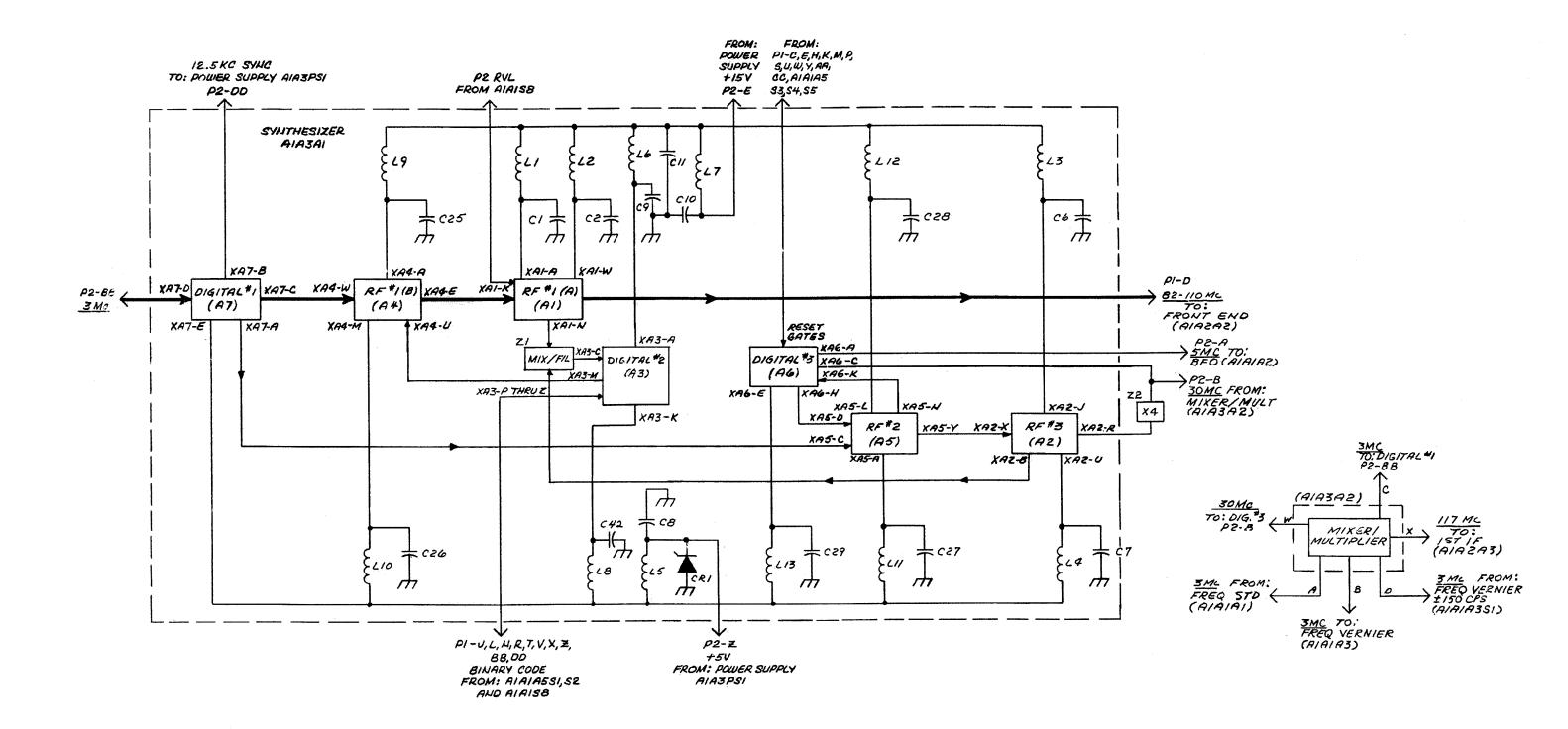

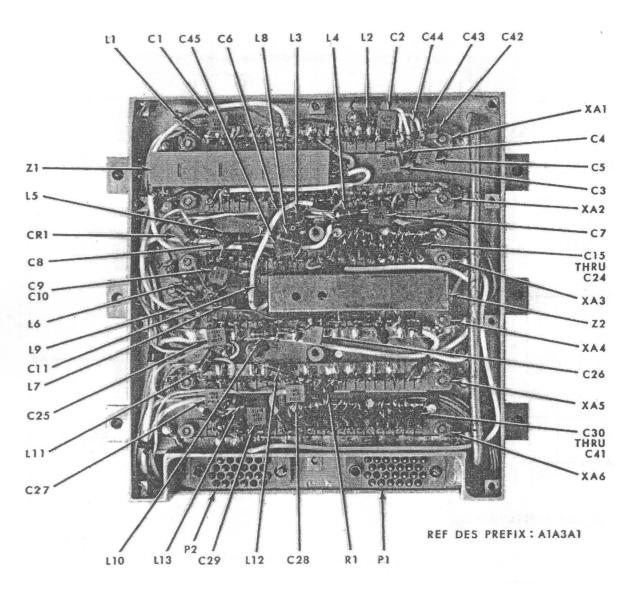

| 4-17 Synthesizer Circuits AlA3Al             | 4-67  | c. Test Equipment                  | 4-111 |

| a. Synthesizer Output                        | 4-69  | d. Control Setting                 | 4-111 |

| b. Synthesizer Components                    | 4-69  | e. Test Data                       | 4-111 |

| c. Synthesizer Control                       | 4-70  | 4-23 RF #2, A1A3A1A5               | 4-112 |

| d. Standard-Frequency Dividers               | 4 50  | a. Description                     | 4-112 |

| and Multipliers                              | 4-73. | b. Preliminary Check               | 4-117 |

| e. Preliminary Check                         | 4-73  | c. Test Equipment                  | 4-117 |

| f. Test Equipment                            | 4-73  | d. Control Settings                | 4-117 |

| g. Control Settings                          | 4-73  | e. Test Data                       | 4-117 |

| h. Test Data                                 | 4-73  | 4-24 Digital #3, A1A3A1A6          | 4-117 |

| i. Trouble Shooting Suggestions              | 4-74  | a. Description                     | 4-117 |

| 4-18 Megacycles Frequency<br>Selector AlAlA5 | 4-75  | b. Preliminary Check               | 4-124 |

| a. Description                               | 4-75  | c. Test Equipment                  | 4-124 |

| b. Preliminary Check                         | 4-80  | d. Control Settings                | 4-124 |

| c. Test Equipment                            | 4-80  | e. Test Data                       | 4-124 |

| d. Test Data                                 | 4-80  | 4-25 Digital #1, AlA3AlA7          | 4-124 |

| 4-19 RF #1(A), A1A3A1A1                      | 4-82  | a. Description                     | 4-124 |

| a. Description                               | 4-82  | b. Preliminary Check               | 4-128 |

| b. Preliminary Check                         | 4-83  | c. Test Equipment                  | 4-128 |

| c. Test Equipment                            | 4-86  | d. Control Settings                | 4-128 |

| d. Control Settings                          | 4-86  | e. Test Data                       | 4-128 |

| e. Test Data                                 | 4-86  | 4-26 Mixer/Multiplier AlA3A2       | 4-128 |

| 4-20 RF #1(B), A1A3A1A4                      | 4-86  | a. Description                     | 4-128 |

| a. Description                               | 4-86  | b. Preliminary Check               | 4-134 |

| b. Preliminary Check                         | 4-93  | c. Test Equipment                  | 4-135 |

| c. Test Equipment                            | 4-93  | d. Control Settings                | 4-135 |

|                                              |       | e. Test Data                       | 4-135 |

e. Test Data 4-135

ORIGINAL

| SECTION 4. TROUBLE SHOOTING CONT'D                       |       | SECTION 5. MAINTENANCE CONT'D            |               |

|----------------------------------------------------------|-------|------------------------------------------|---------------|

| PARA                                                     | PAGE  | PARA                                     | PAGE          |

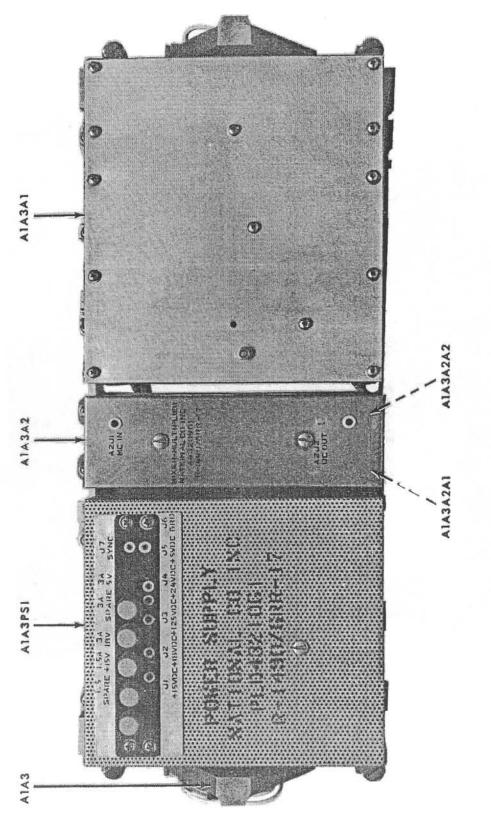

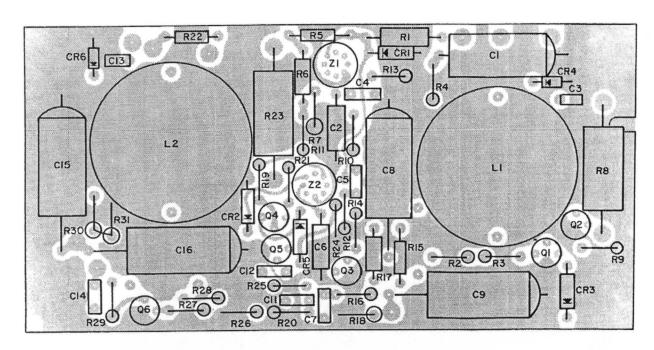

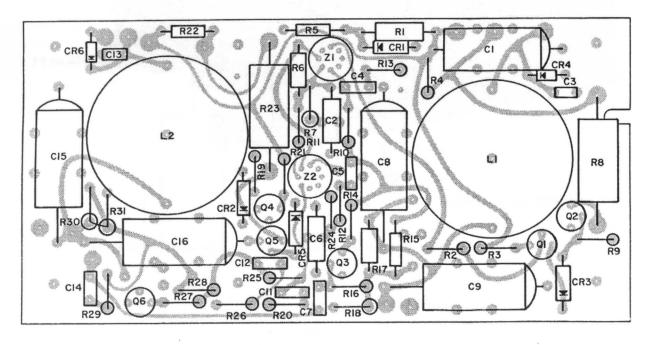

| 4-27 Power Supply A1A3PS1                                | 4-135 | (5) VHF Oscillator Phase-                |               |

| a. Description                                           | 4-135 | Lock Loop (A1A2A2A1)                     | 5-12          |

| b. Preliminary Check                                     | 4-140 | (6) First I-F Module<br>(A1A2A3)         | 5-13          |

| c. Test Equipment                                        | 4-141 | (7) Noise Blanker Module                 |               |

| d. Control Settings                                      | 4-141 | (A1A2A4)                                 | 5-15          |

| e. Test Data                                             | 4-141 | (8) Second I-F/AGC Module                | <b>5</b> 1/   |

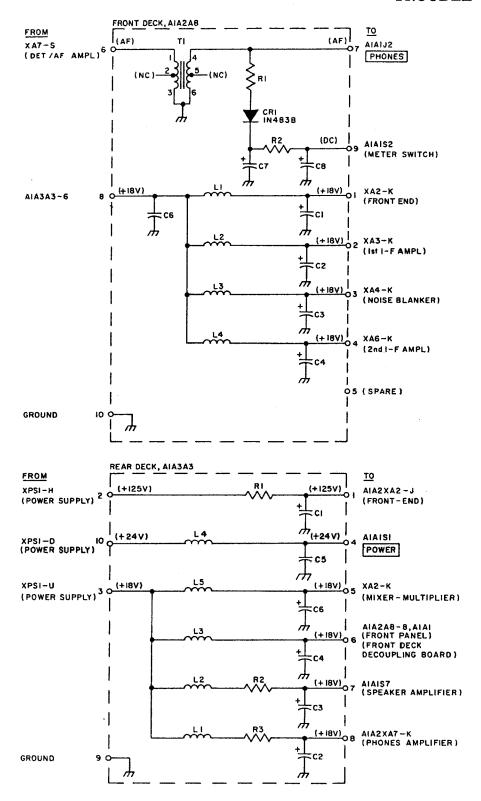

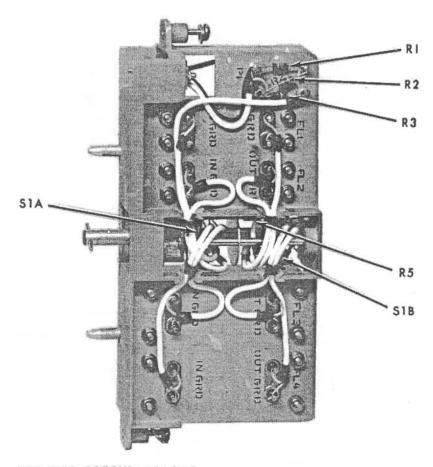

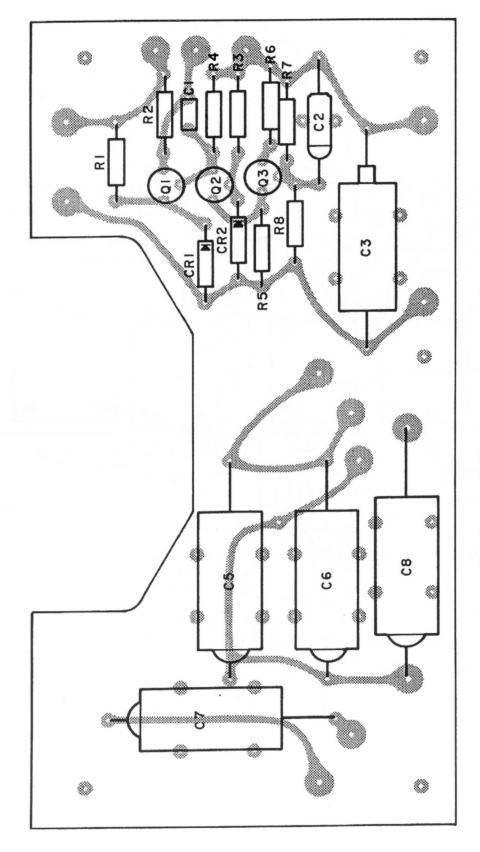

| 4-28 Power-Supply Decoupling<br>Boards AlA2A8 and AlA3A3 | 4-141 | (A1A2A6) (9) Notch Filter (A1A1A4)       | 5-16<br>5-17  |

| a. Description                                           | 4-141 | (10) Beat Frequency Oscil-               |               |

| b. Preliminary Check                                     | 4-143 | lator (AlAlA2)                           | 5-18          |

| c. Test Equipment                                        | 4-143 | (11) Audio Detector/Amplifier (A1A2A7A1) | 5-19          |

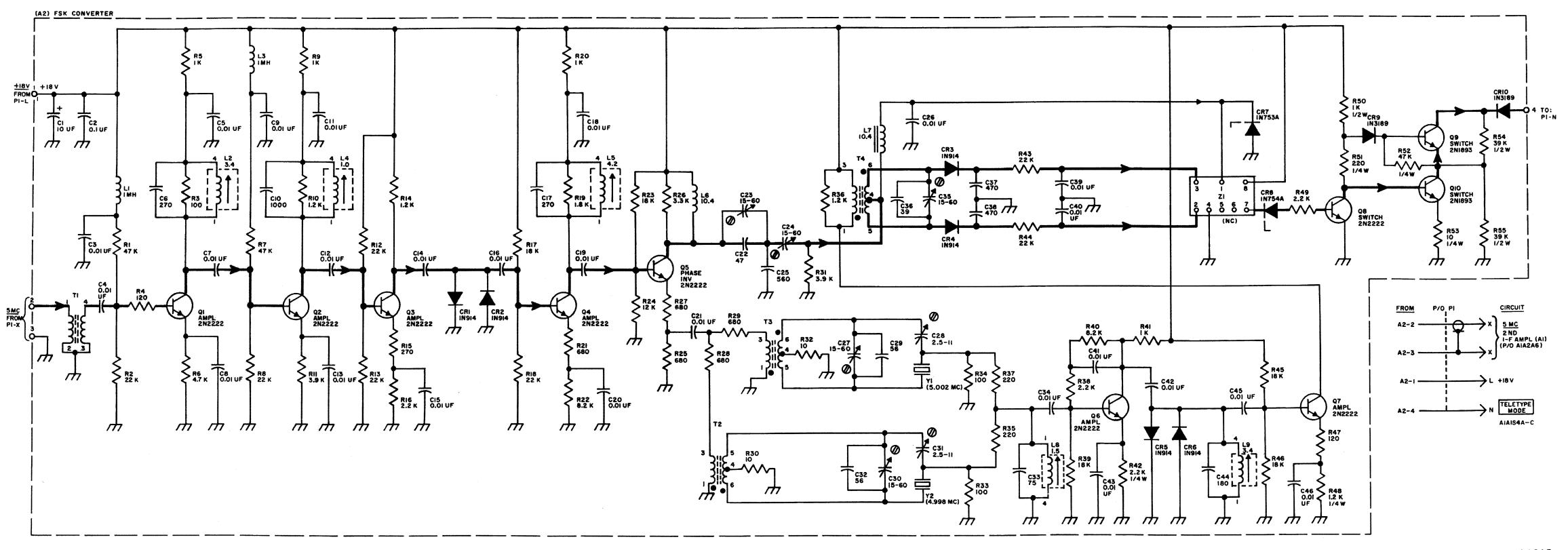

| d. Control Settings                                      | 4-143 | (12) FSK Converter                       | 3 1 ,         |

| e. Test Data                                             | 4-143 | (A1A2A7A2)                               | 5-20          |

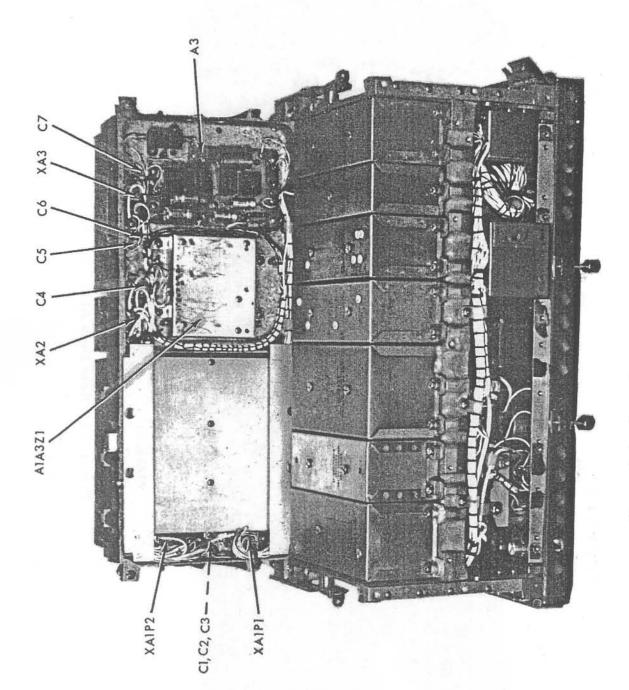

| 4-29 TTY Power Supply AlA3Zl                             | 4-144 | 5-3 Repair                               | 5-22          |

| a. Description                                           | 4-144 | a. General                               | 5-22          |

| b. Preliminary Check                                     | 4-144 | b. Module Repair Techniques              | 5-22          |

| c. Test Equipment                                        | 4-145 | c. Use of Parts Location and             |               |

| d. Control Settings                                      | 4-145 | Schematic Diagrams                       | 5-22          |

| e. Test Data                                             | 4-145 | 5-4 Removal and Replacement              | 5-22          |

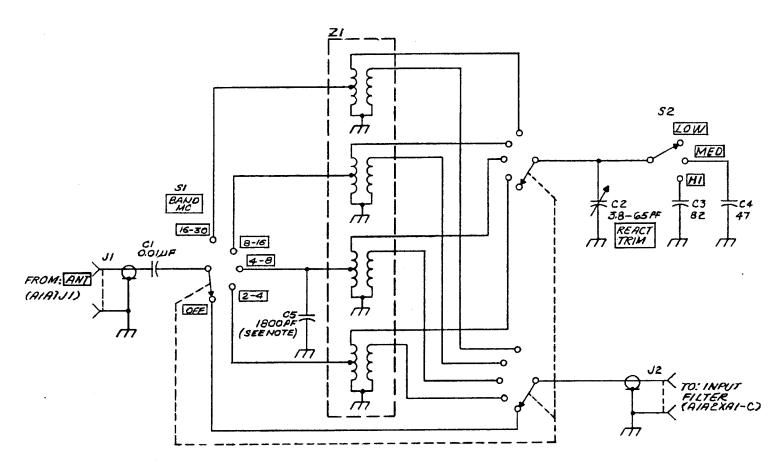

| 4-30 Antenna Trimming Circuit                            |       | a. General                               | 5-22          |

| AlAlA6                                                   | 4-145 | b. Procedures                            | 5-23          |

| a. Description                                           | 4-145 | (1) Radio Receiver R-1490/<br>GRR-17     | 5-23          |

| b. Preliminary Check                                     | 4-145 | (2) Frequency Standard                   | 3 - 3         |

| c. Test Equipment                                        | 4-145 | AlAlAl                                   | 5-24          |

| d. Control Settings                                      | 4-145 | (3) VFO AlAlA3                           | 5-24          |

| e. Test Data                                             | 4-146 | (4) BFO AlAlA2                           | 5-25          |

| SECTION 5. MAINTENANCE                                   |       | (5) Notch Filter AlAlA4                  | 5-26          |

| 5-1 Introduction                                         | 5-1   | (6) Frequency Selector AlAlA5            | 5-27          |

| 5-2 Preventive Maintenance                               | 5-1   | (7) Input Filter AlA2Al                  | 5-28          |

| a. Maintenance Standards                                 | 5-1   | (8) Front End AlA2A2                     | 5-28          |

| b. Tuning and Adjustment                                 | 5-9   | (9) First I-F Amplifier                  |               |

| (1) Introduction                                         | 5-9   | AlA2A3                                   | 5-29          |

| (2) Frequency Standard (AlAlAl)                          | 5-9   | (10) Noise Blanker A1A2A4                | 5-30          |

| (3) Mixer/Multiplier                                     | J- y  | (11) Intelligence Filter A1A2A5          | 5-30          |

| (A1A3A2)                                                 | 5-10  |                                          | 9 <b>- 90</b> |

| (4) Frequency Synthesizer (A1A3A1)                       | 5-12  | (12) Second I-F/AGC Amplifier AlA2A6     | 5-31          |

vi ORIGINAL

| SECTION | 5. MAINTENANCE<br>CONT'D              |      | SECTION 5. MAINTENANCE<br>CONT'D     |      |

|---------|---------------------------------------|------|--------------------------------------|------|

| PARA    |                                       | PAGE | PARA                                 | PAGE |

| (13)    | Detector/AF Amplifier A1A2A7          | 5-31 | (19) TTY Power Supply AlA3Z1         | 5-35 |

| (14)    | Front Deck Decoupling<br>Board A1A2A8 | 5-32 | (20) Antenna Trimming Circuit AlAlA6 | 5-36 |

| (15)    | Synthesizer A1A3A1                    | 5-33 | 5-5 Maintenance Illustrations        | 5-36 |

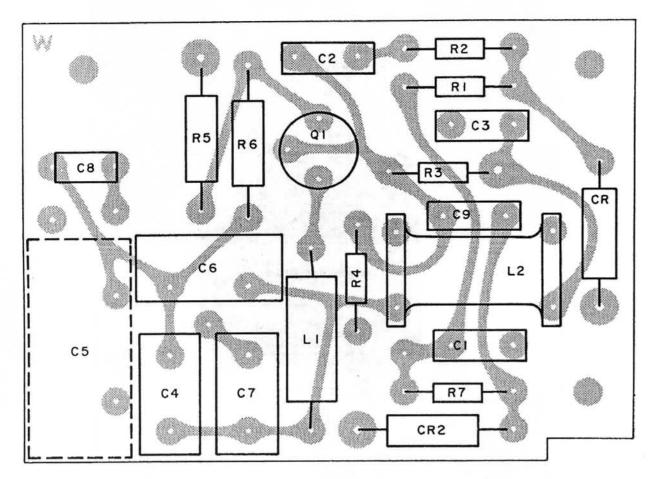

| (16)    | Mixer/Multiplier A1A3A2               | 5-33 | a. Part Location Illustrations       | 5-36 |

| (17)    | Power Supply AlA3PS1                  | 5-34 | b. Primary-Power Distribution        |      |

| (18)    | Rear Deck Decoupling                  |      | Diagram                              | 5-37 |

| (,      | Board AlA3A3                          | 5-35 | c. Schematic Diagrams                | 5-37 |

|         |                                       |      |                                      |      |

#### LIST OF ILLUSTRATIONS

| FIGURE | TITLE                                                                                                             | PAGE |

|--------|-------------------------------------------------------------------------------------------------------------------|------|

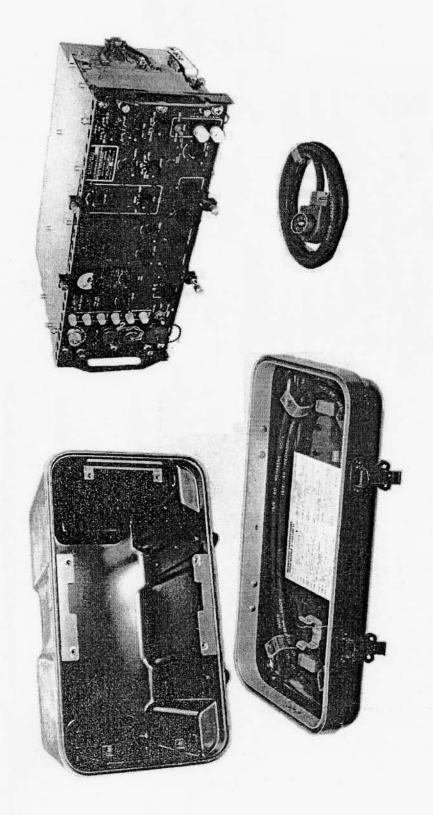

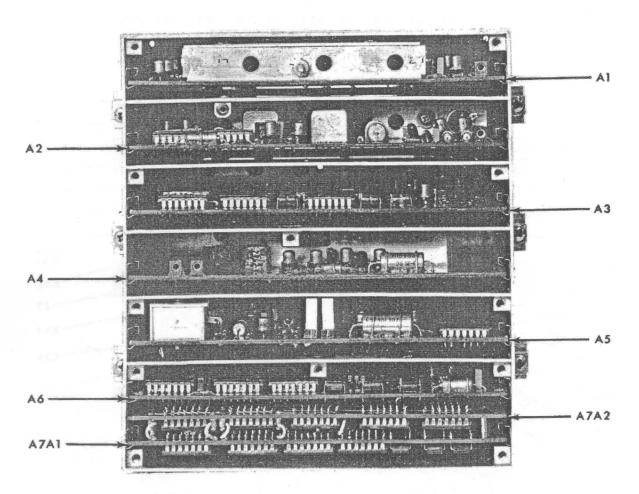

| 1-1    | Radio Receiving Set AN/GRR-17                                                                                     | 10   |

| 2-1    | External Cable Connections                                                                                        | 2-2  |

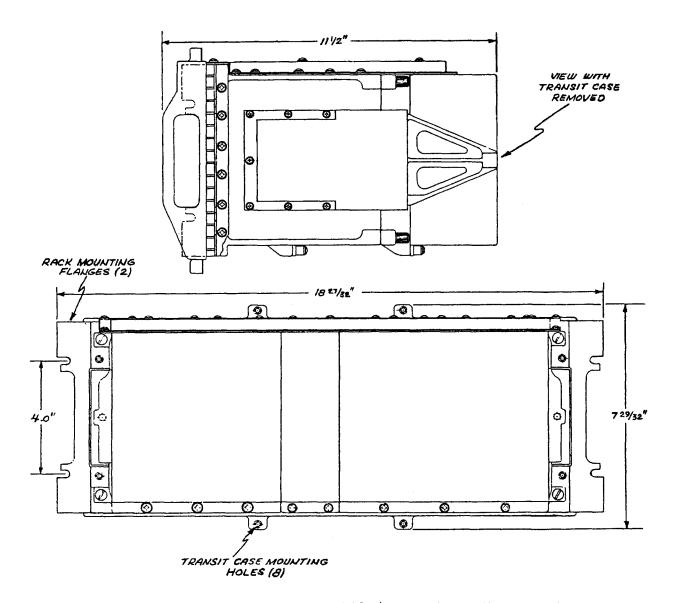

| 2-2    | Radio Receiver R-1490/GRR-17, Outline Drawing                                                                     | 2-4  |

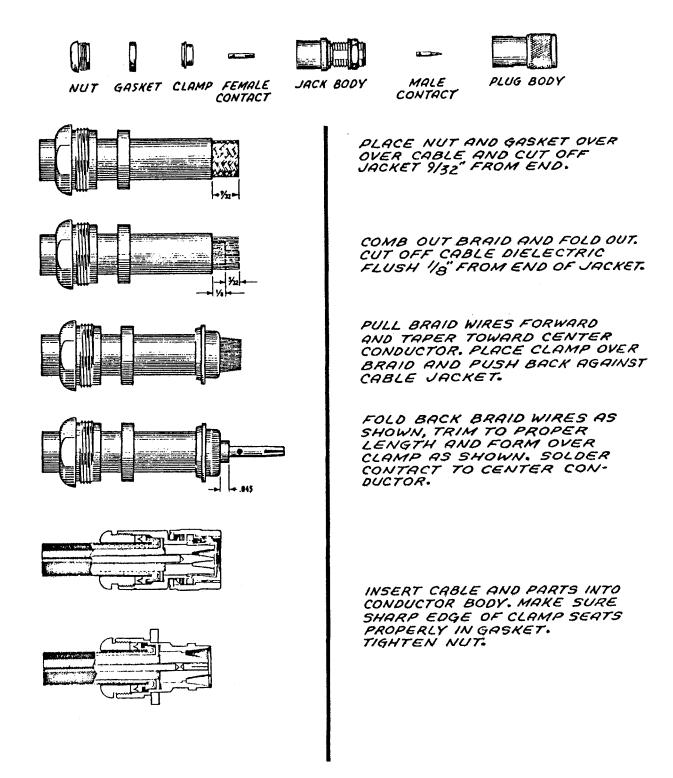

| 2-3    | Antenna Cable, Connector Assembly                                                                                 | 2-6  |

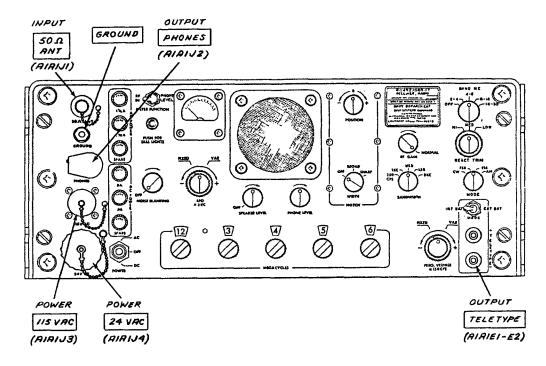

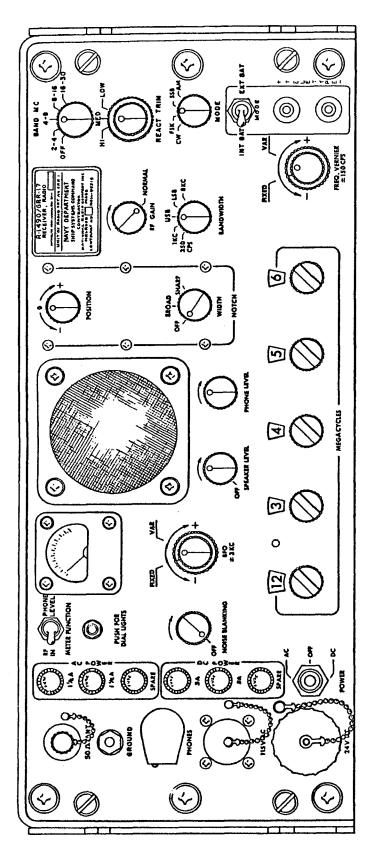

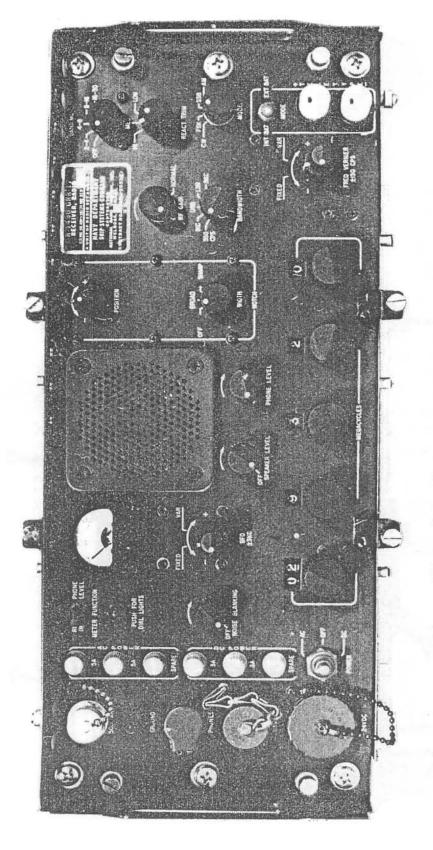

| 3-1    | Radio Receiver R-1490/GRR-17, Front View                                                                          | 3-2  |

| 4-1    | Radio Receiver R-1490/GRR-17, Basic Block Diagram                                                                 | 4-5  |

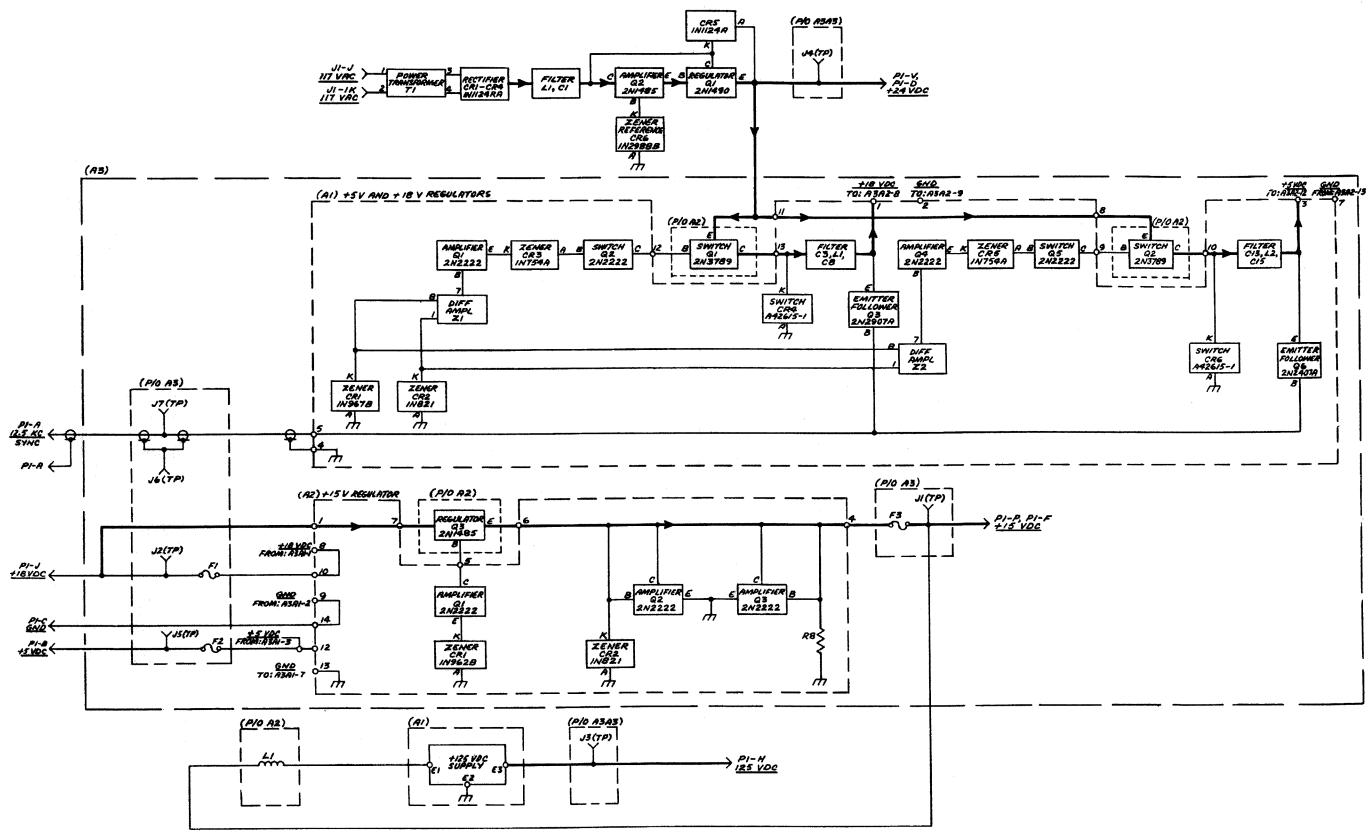

| 4-2    | Radio Receiver R-1490/GRR-17, Functional Block Diagram (Sheet 1 of 2)                                             | 4-9  |

| 4-2    | Radio Receiver R-1490/GRR-17, Functional Block Diagram (Sheet 2 of 2)                                             | 4-11 |

| 4-3    | Input Filter AlA2Al, Simplified Schematic Diagram                                                                 | 4-16 |

| 4-4    | Front-End AlA2A2; VHF Oscillator (Z2) and Up-Converter (Z1), Simplified Block Diagram                             | 4-18 |

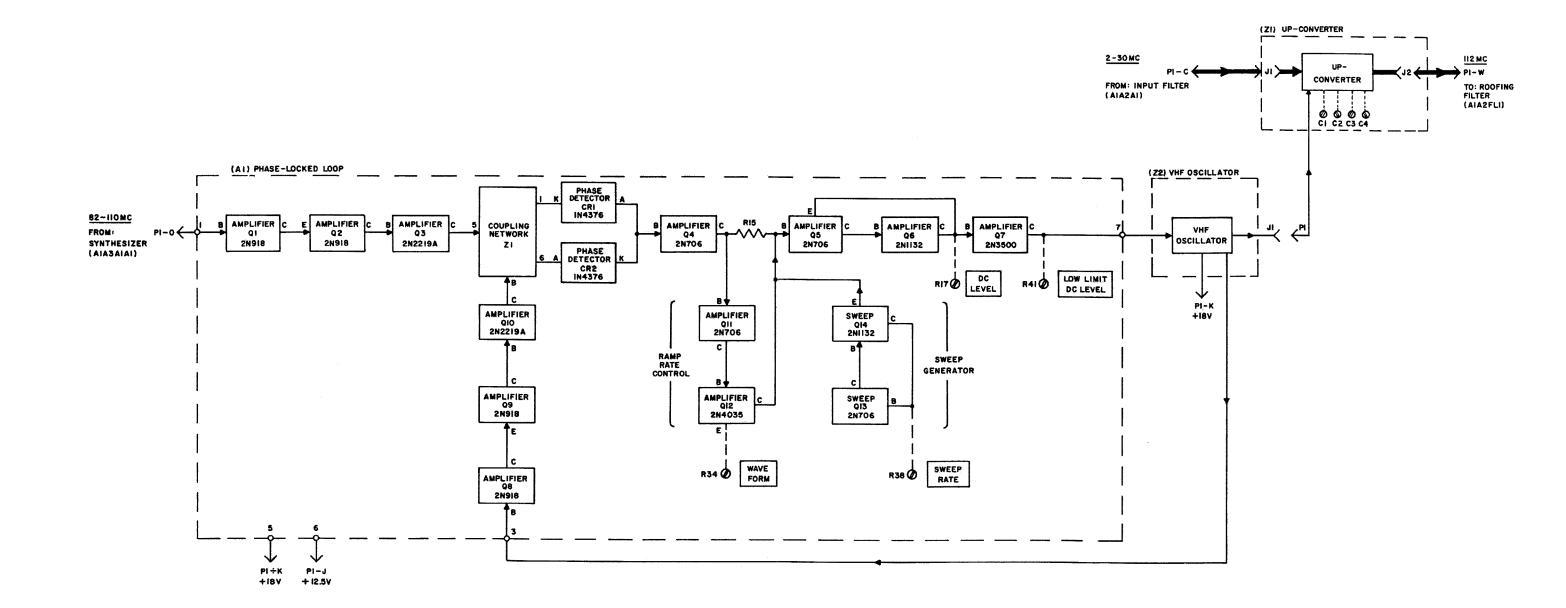

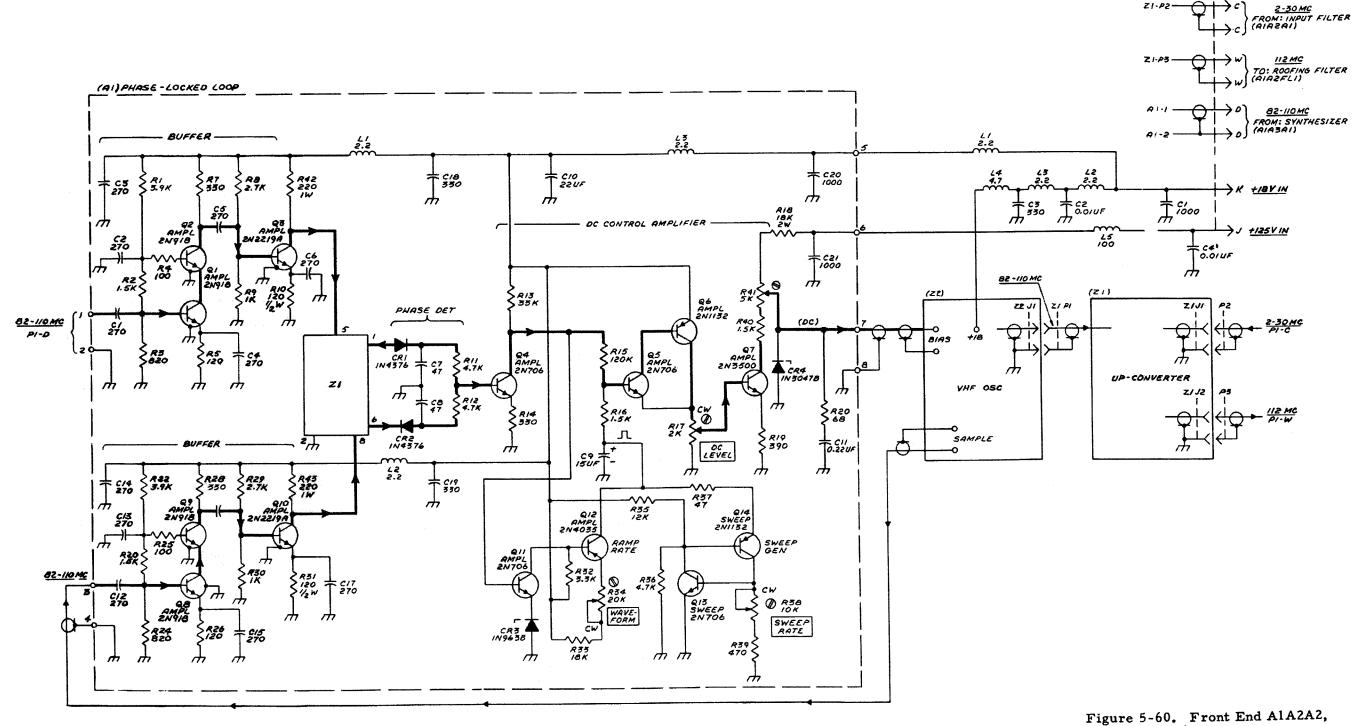

| 4-5    | Front End AlA2A2; Phase-Locked Loop (Al), Simplified Schematic Diagram                                            | 4-19 |

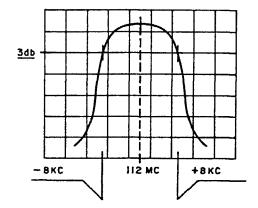

| 4-6    | Roofing Filter AlA2FL1, Functional Diagram                                                                        | 4-23 |

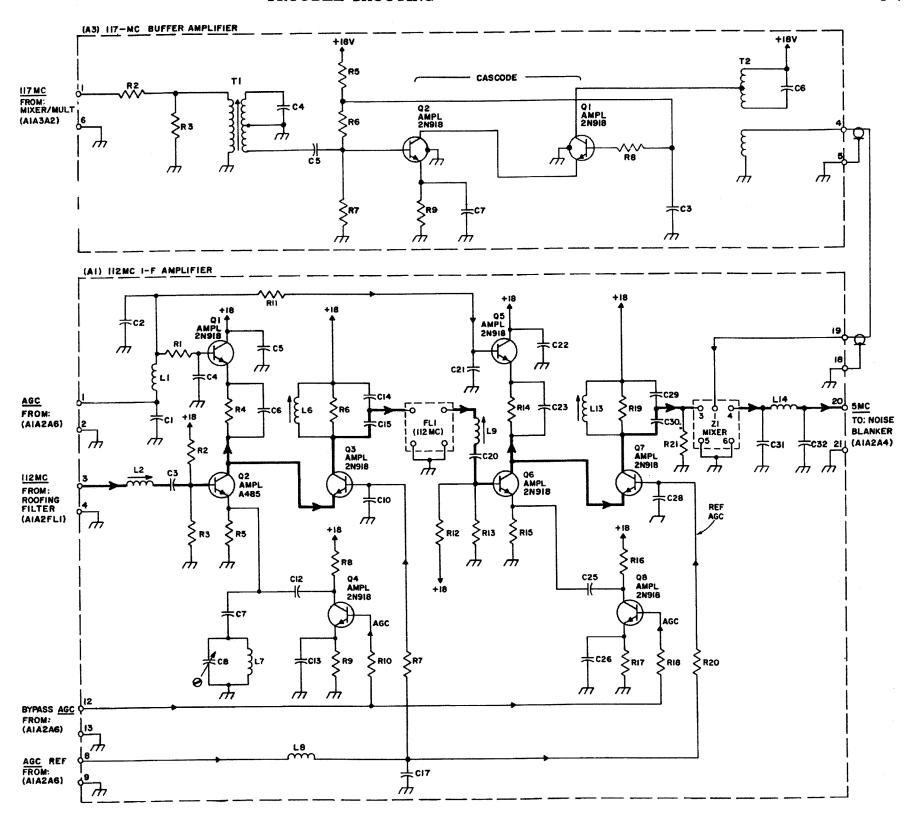

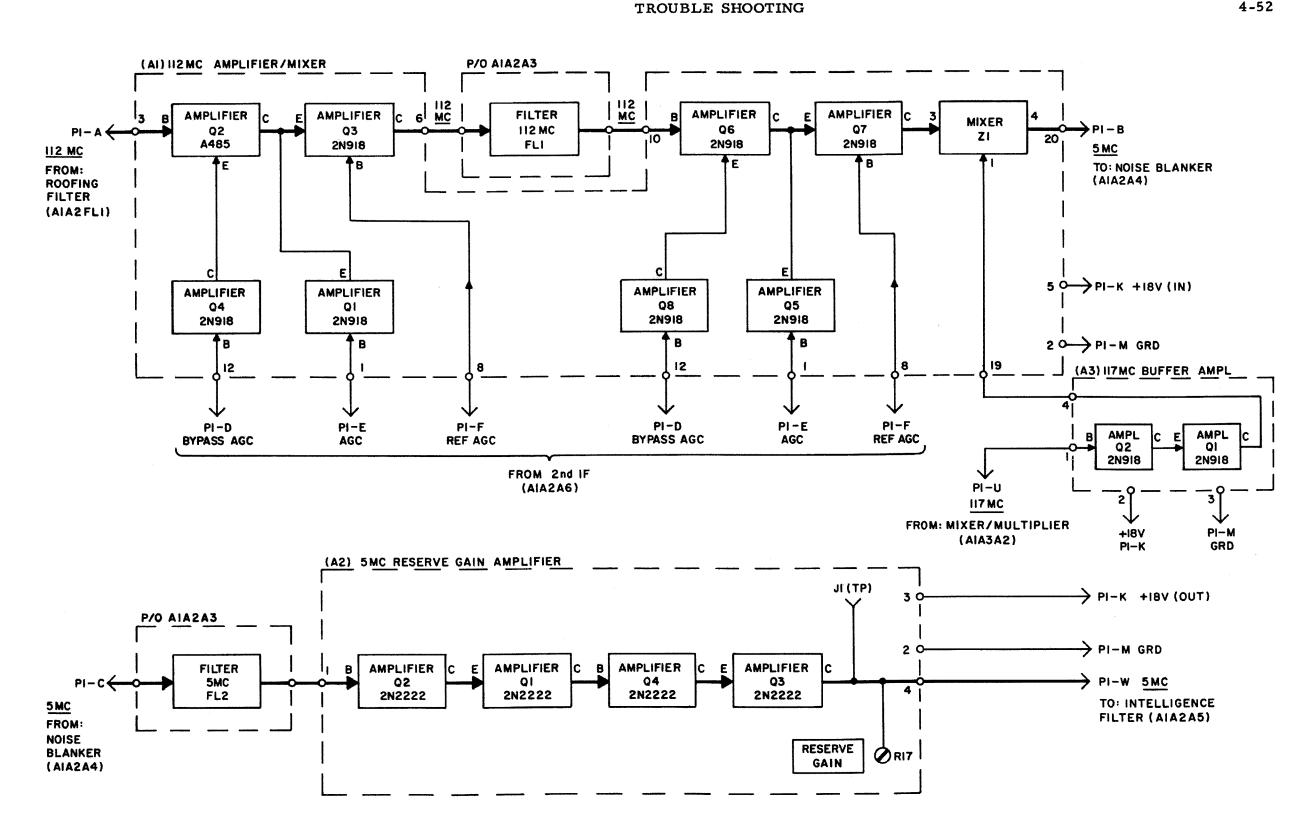

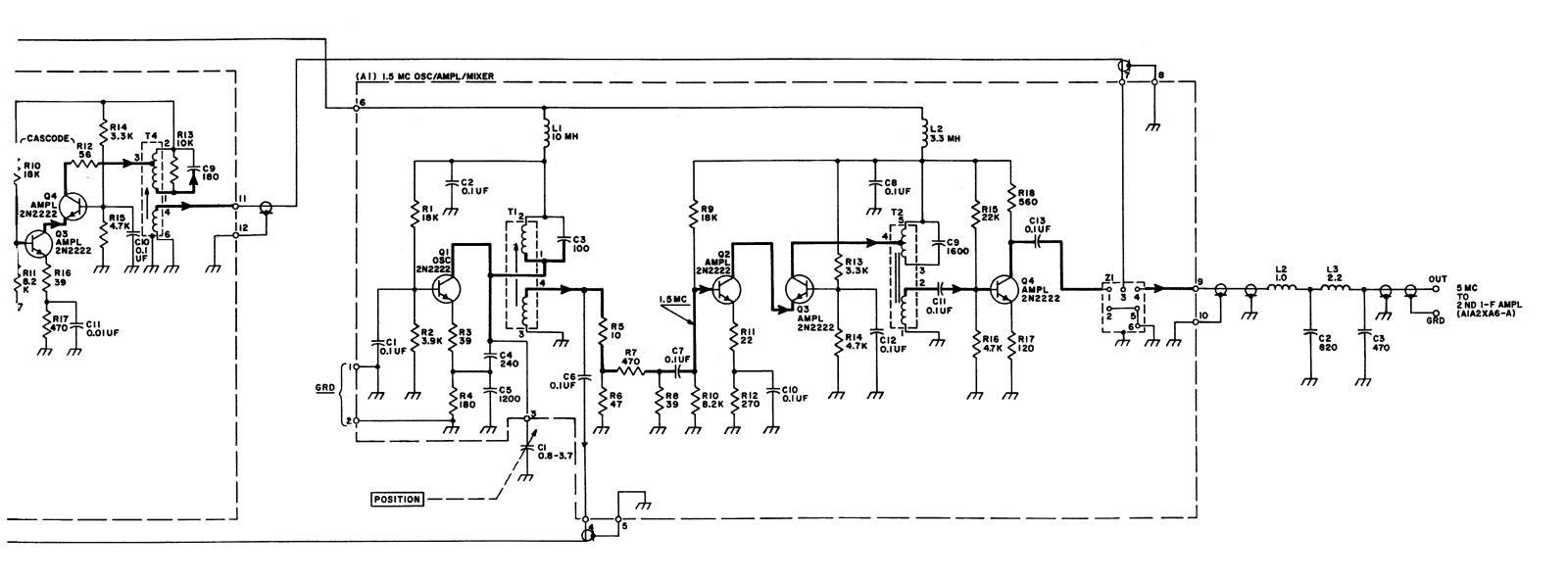

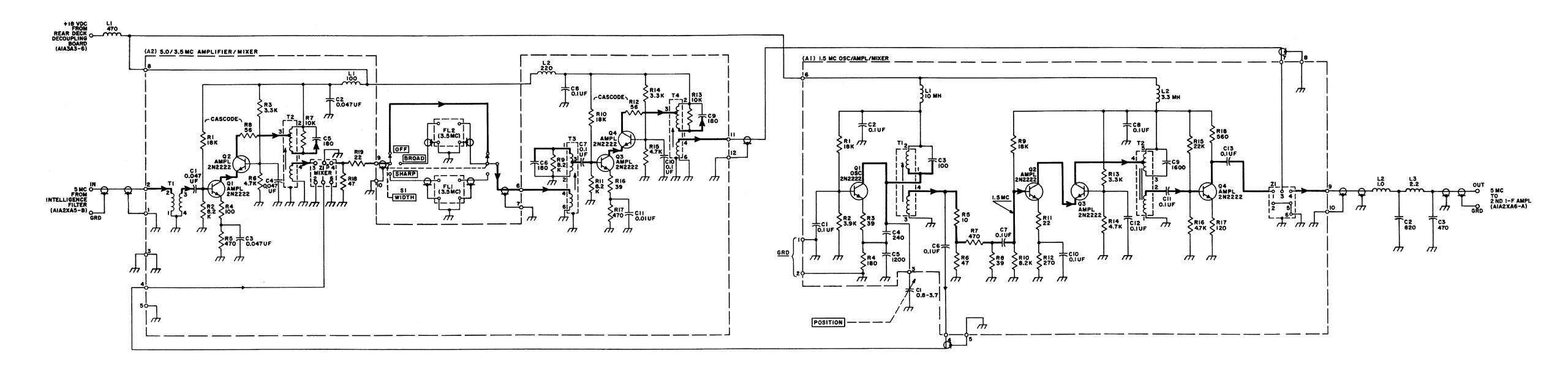

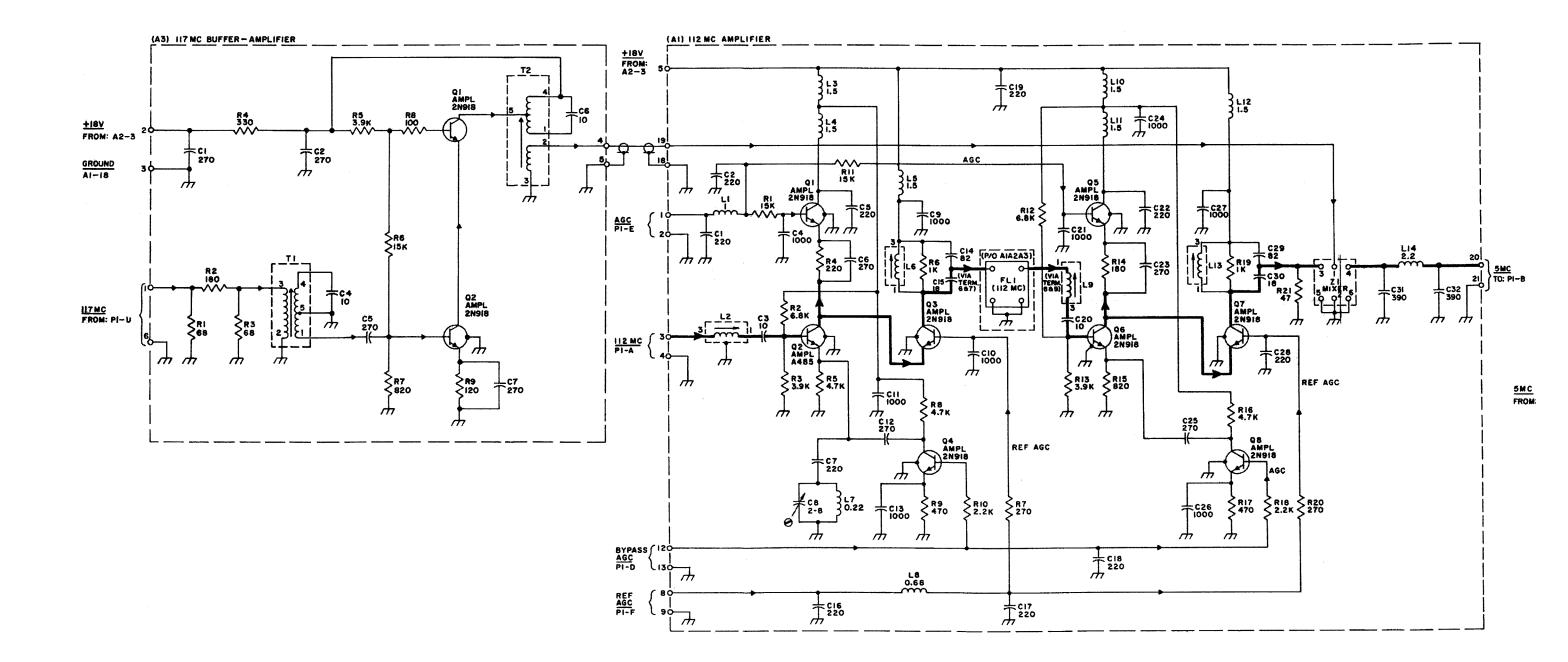

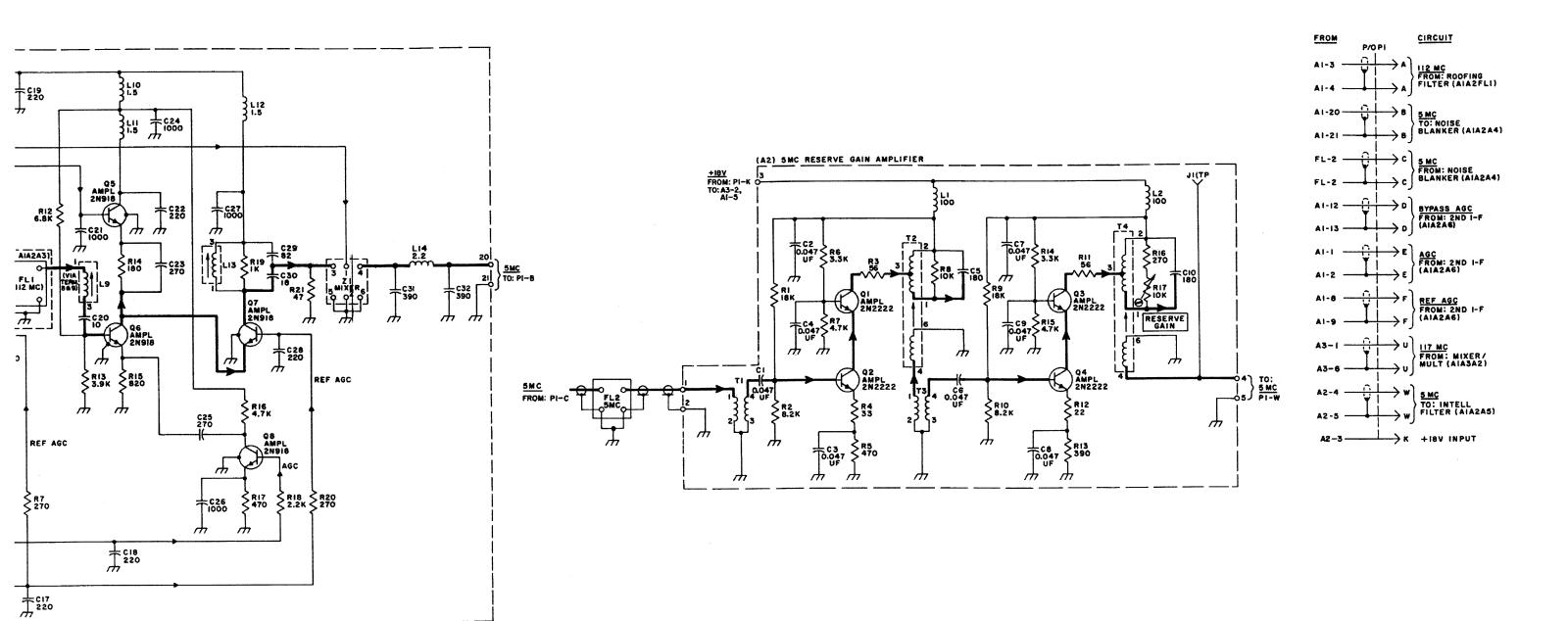

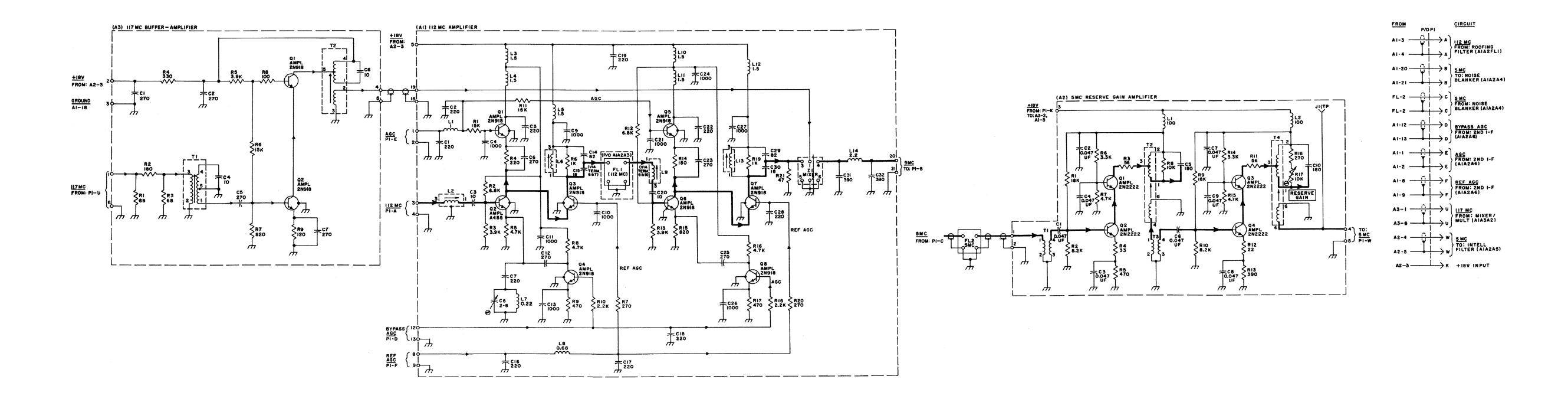

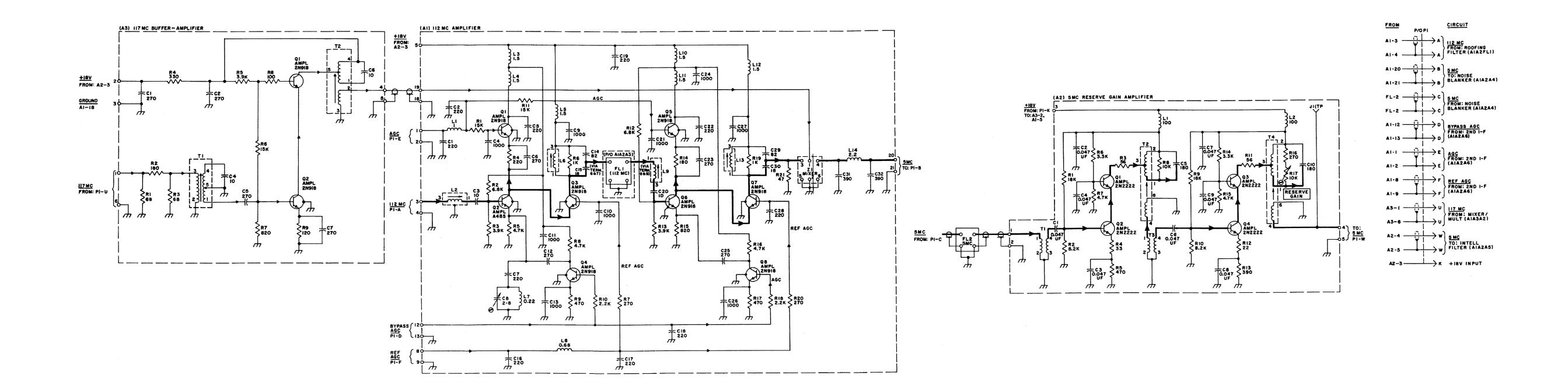

| 4-7    | First I-F Module A1A2A3; 112 MC I-F Amplifier (A1) and 117 MC Buffer Amplifier (A3), Simplified Schematic Diagram | 4-25 |

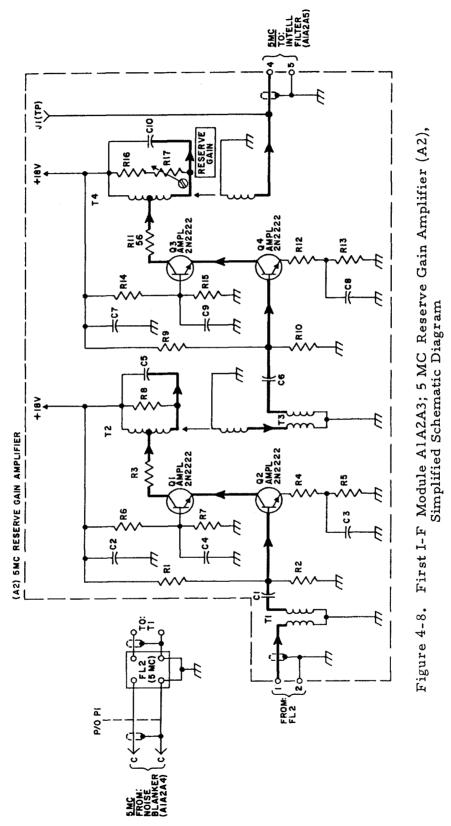

| 4-8    | First I-F Module AlA2A3; 5 MC Reserve Gain Amplifier (A2), Simplified Schematic Diagram                           | 4-27 |

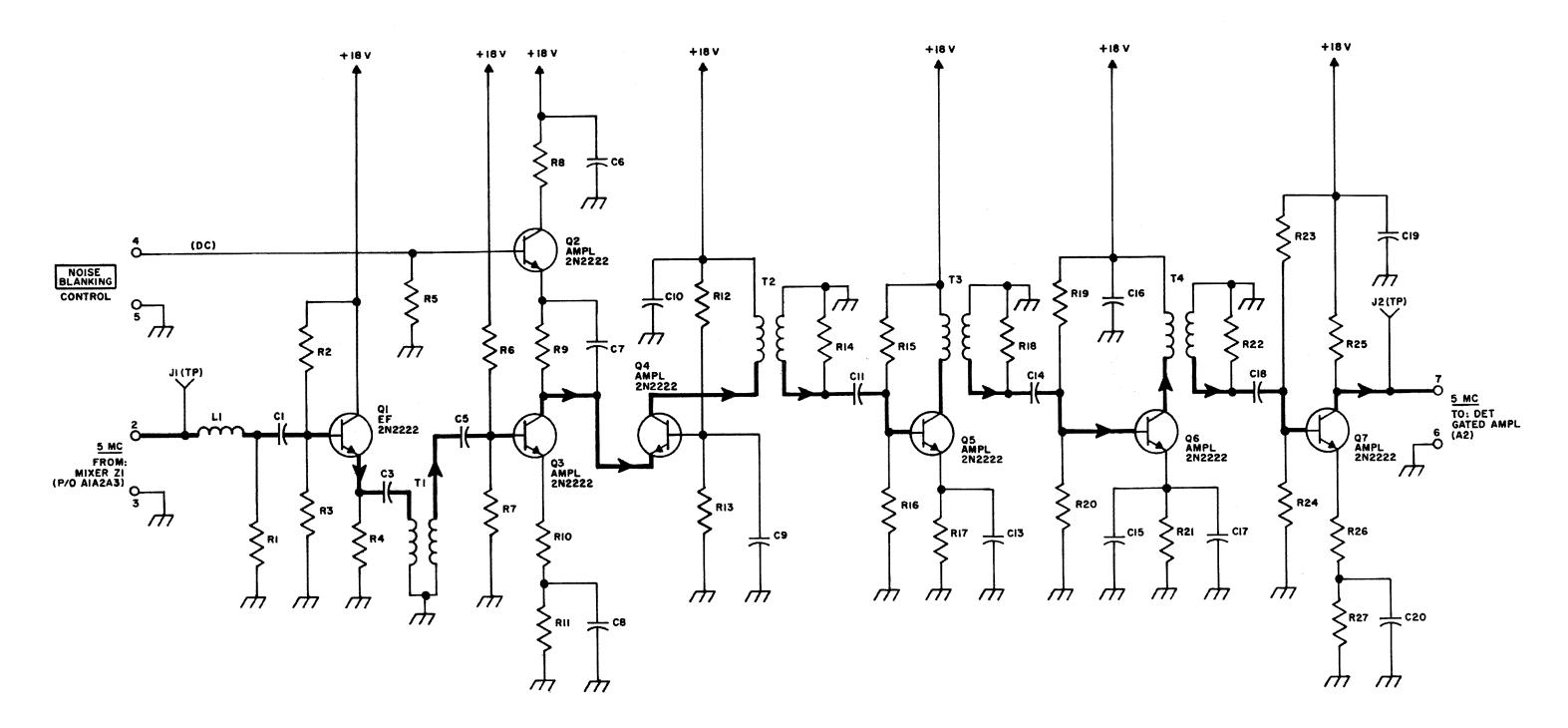

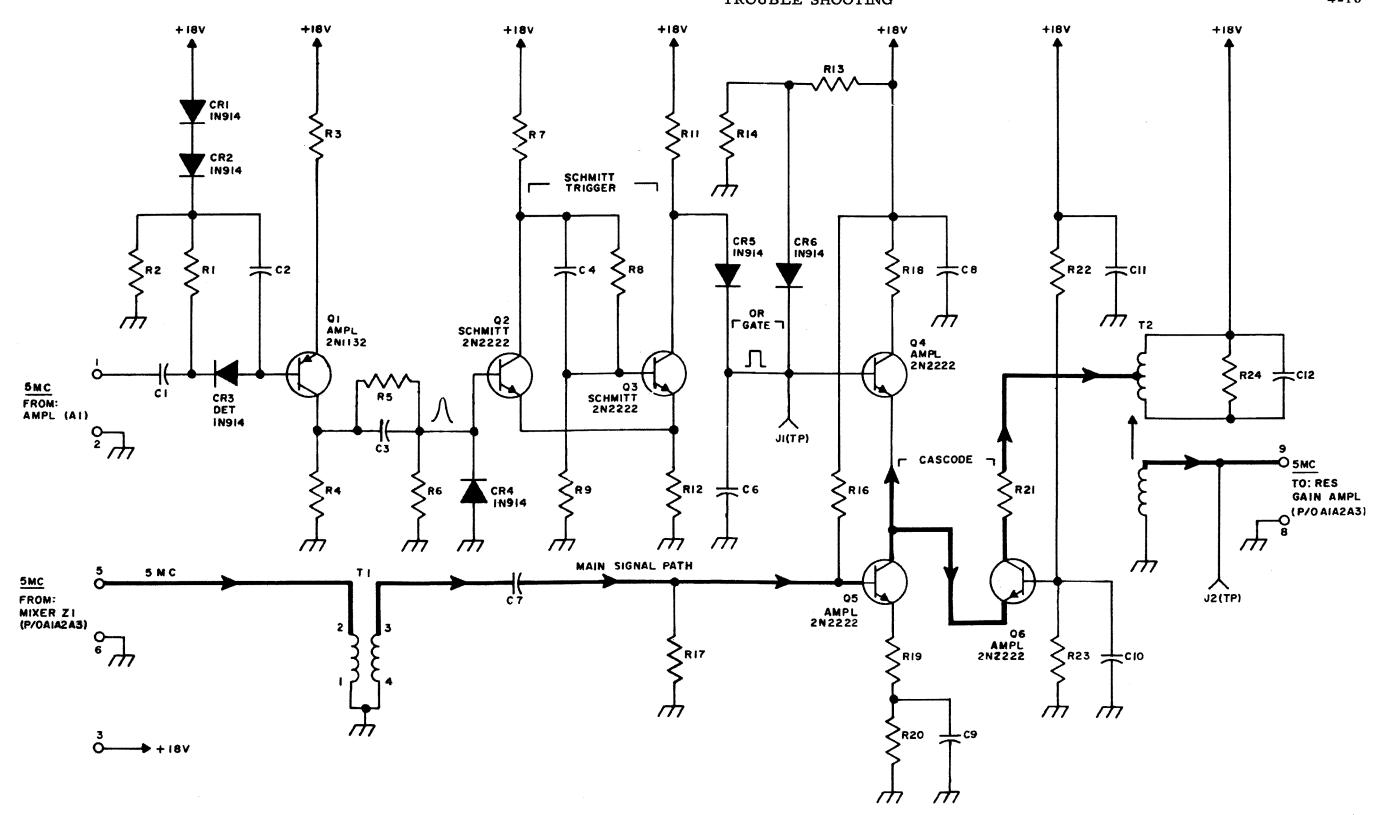

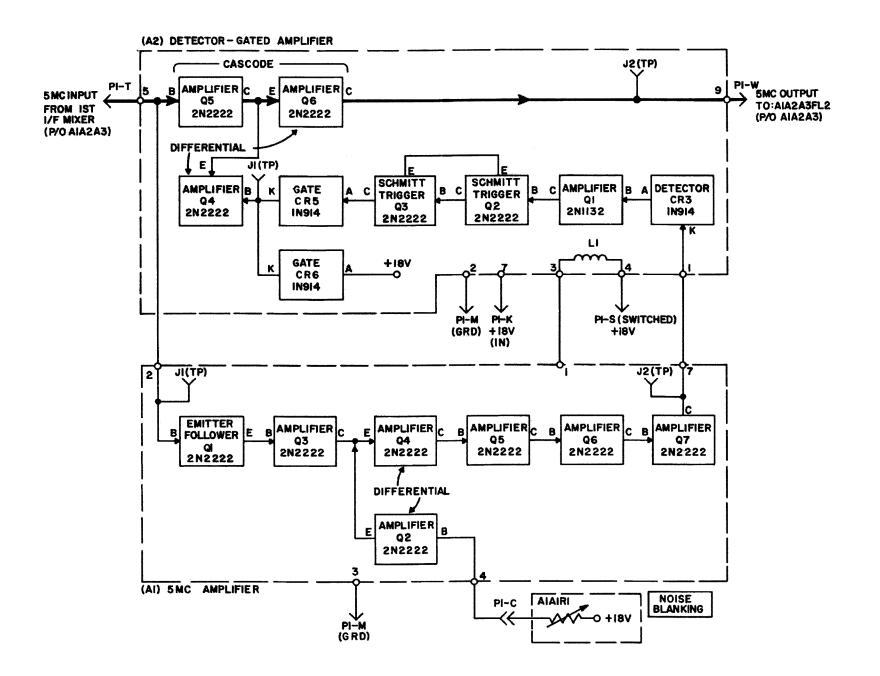

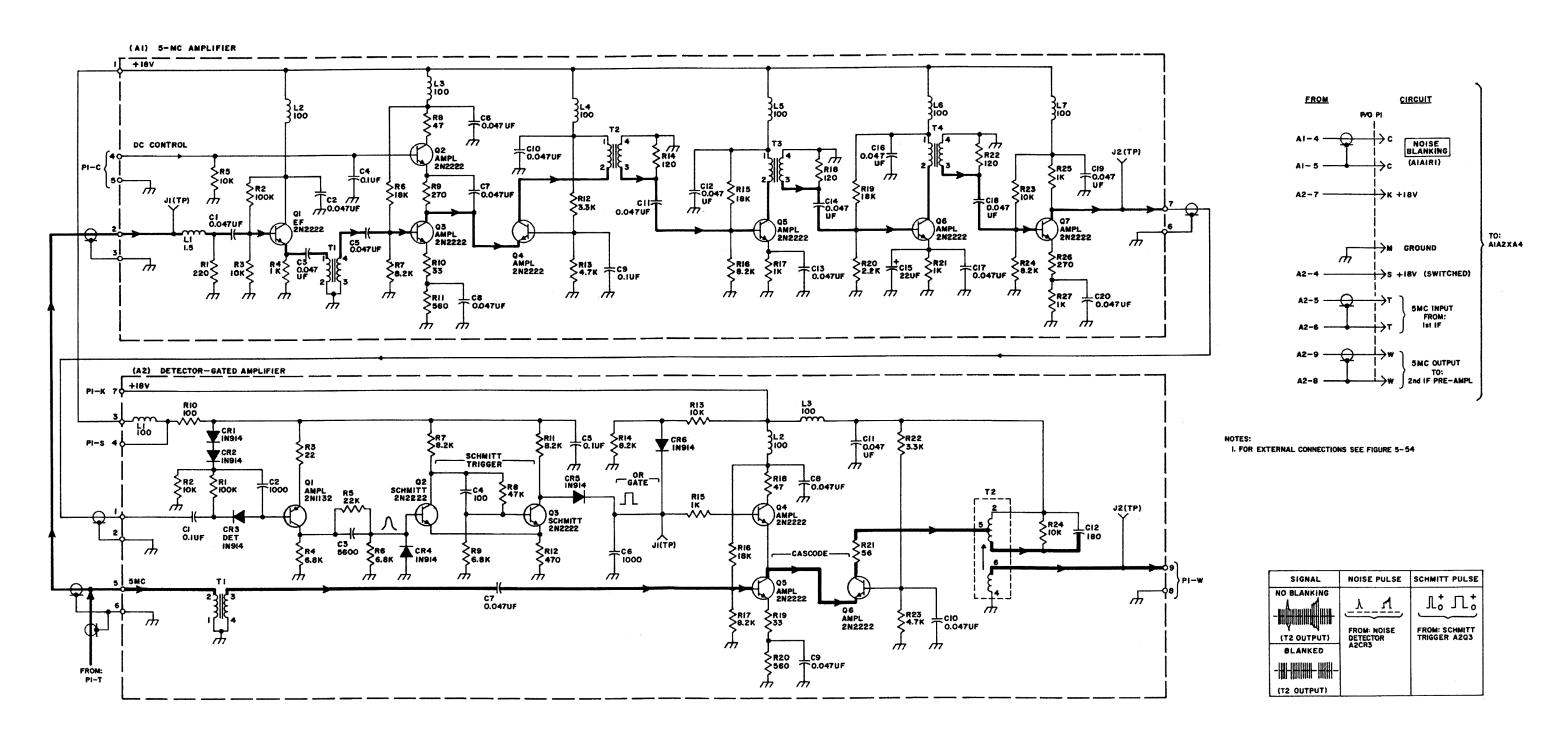

| 4-9    | Noise Blanker A1A2A4; 5 MC Amplifier (A1), Simplified Schematic Diagram                                           | 4-31 |

| 4-10   | Noise Blanker AlA2A4; Detector/Gated Amplifier (A2), Simplified Schematic Diagram                                 | 4-33 |

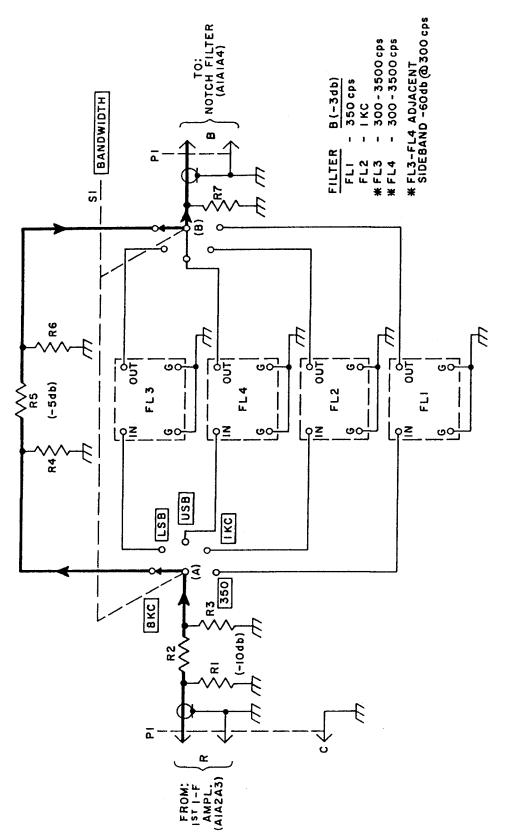

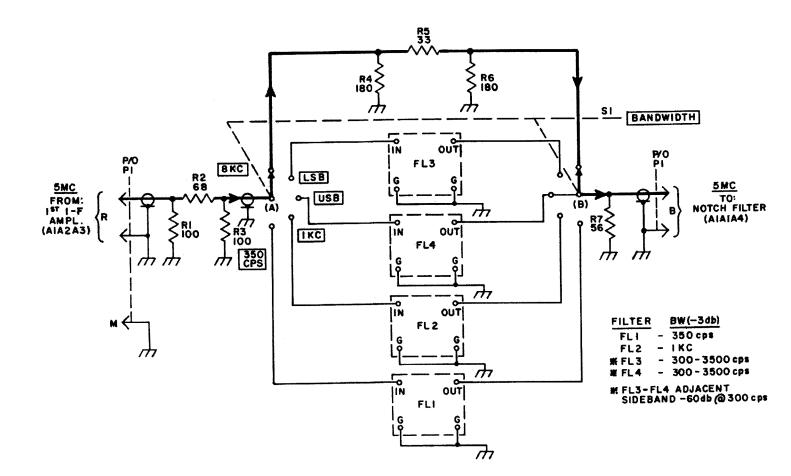

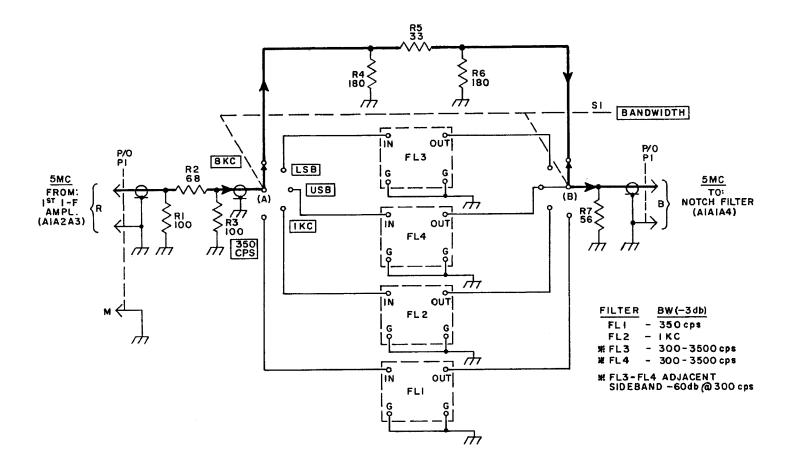

| 4-11   | Intelligence Filter A1A2A5, Simplified Schematic Diagram                                                          | 4-36 |

|        |                                                                                                                   |      |

ORIGINAL

| FIGURE | TITLE                                                                                                              | PAGE  |

|--------|--------------------------------------------------------------------------------------------------------------------|-------|

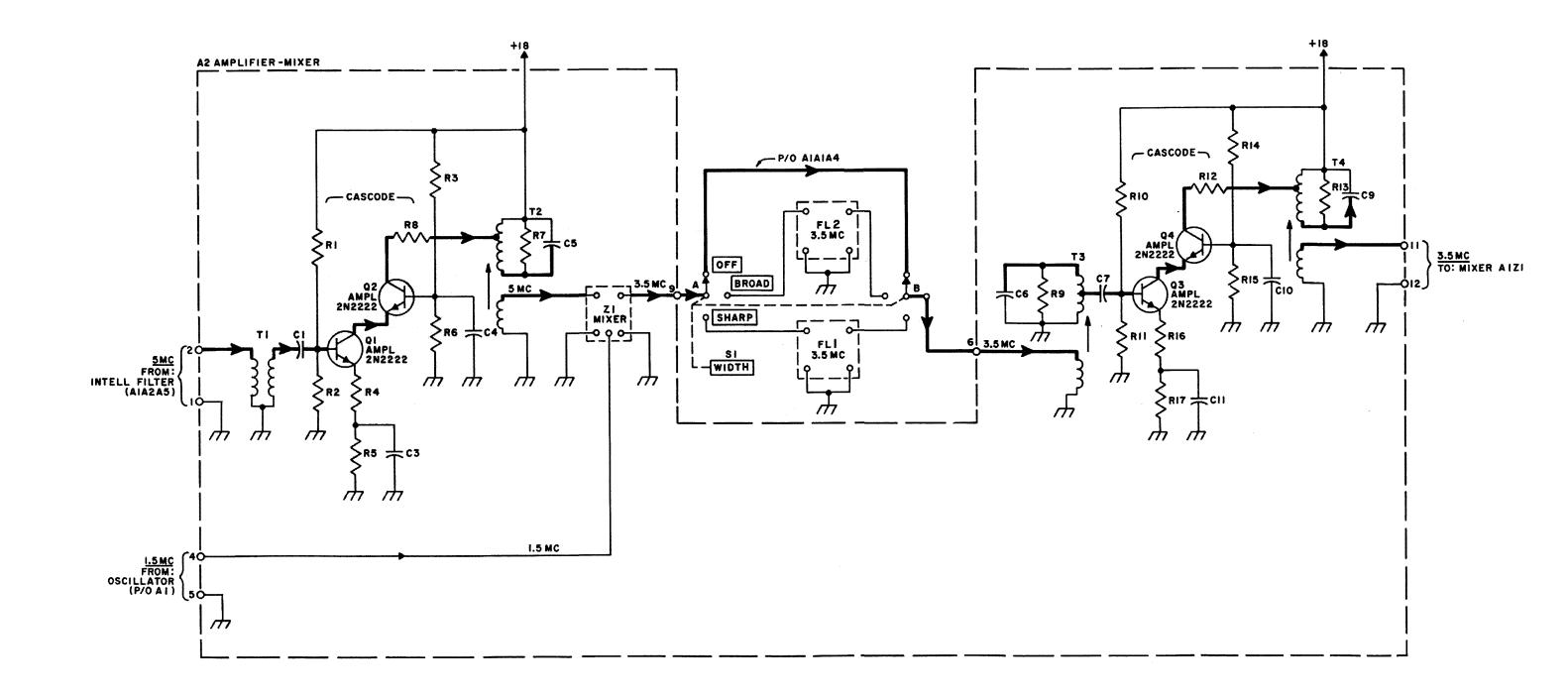

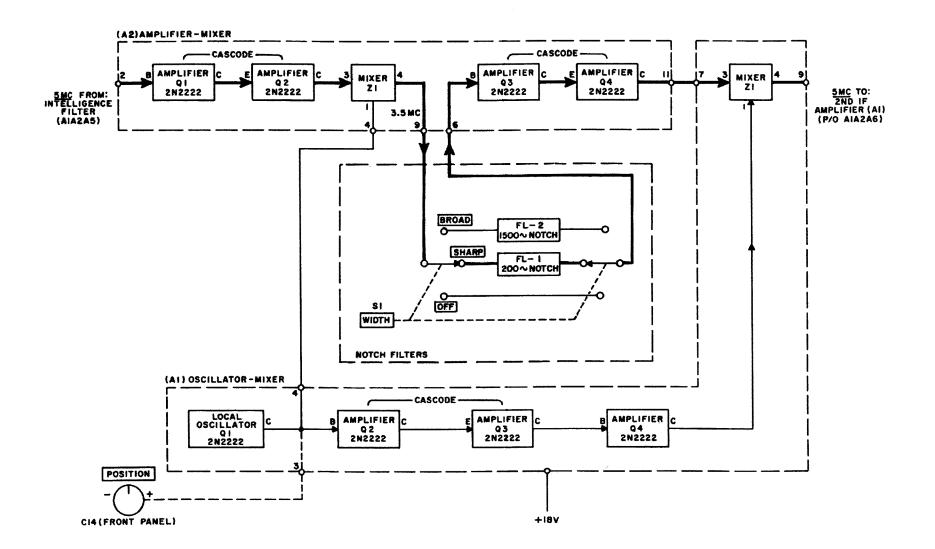

| 4-12   | Notch Filter AlAlA4; Amplifier-Mixer (A2), Simplified Schematic Diagram                                            | 4-39  |

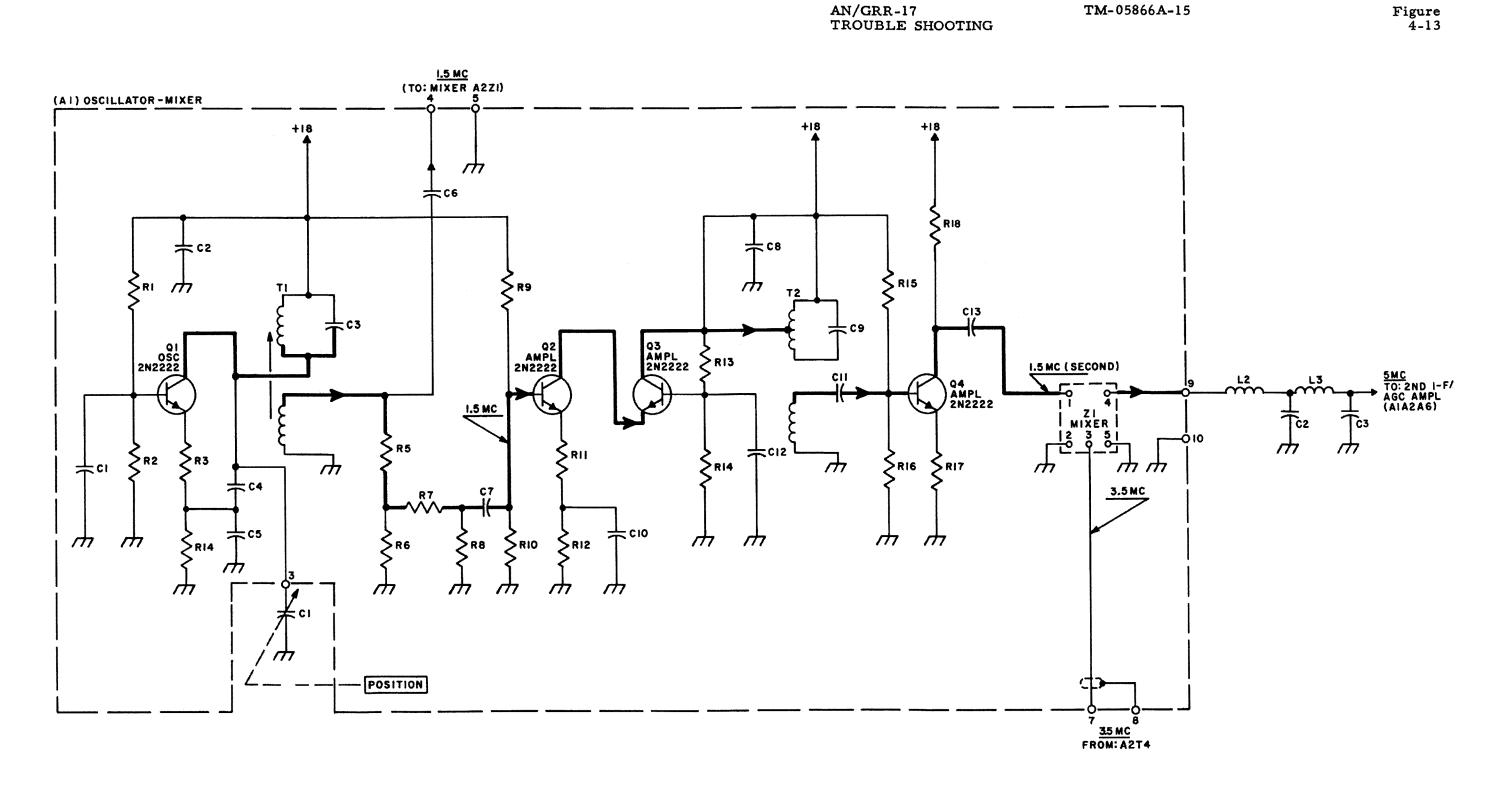

| 4-13   | Notch Filter AlAlA4; Oscillator-Mixer (Al), Simplified Schematic Diagram                                           | 4-41  |

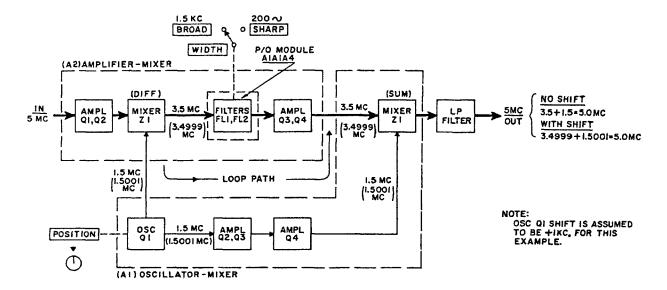

| 4-14   | Notch Filter AlAlA4; Drift-Cancelling Loop, Functional Block Diagram                                               | 4-43  |

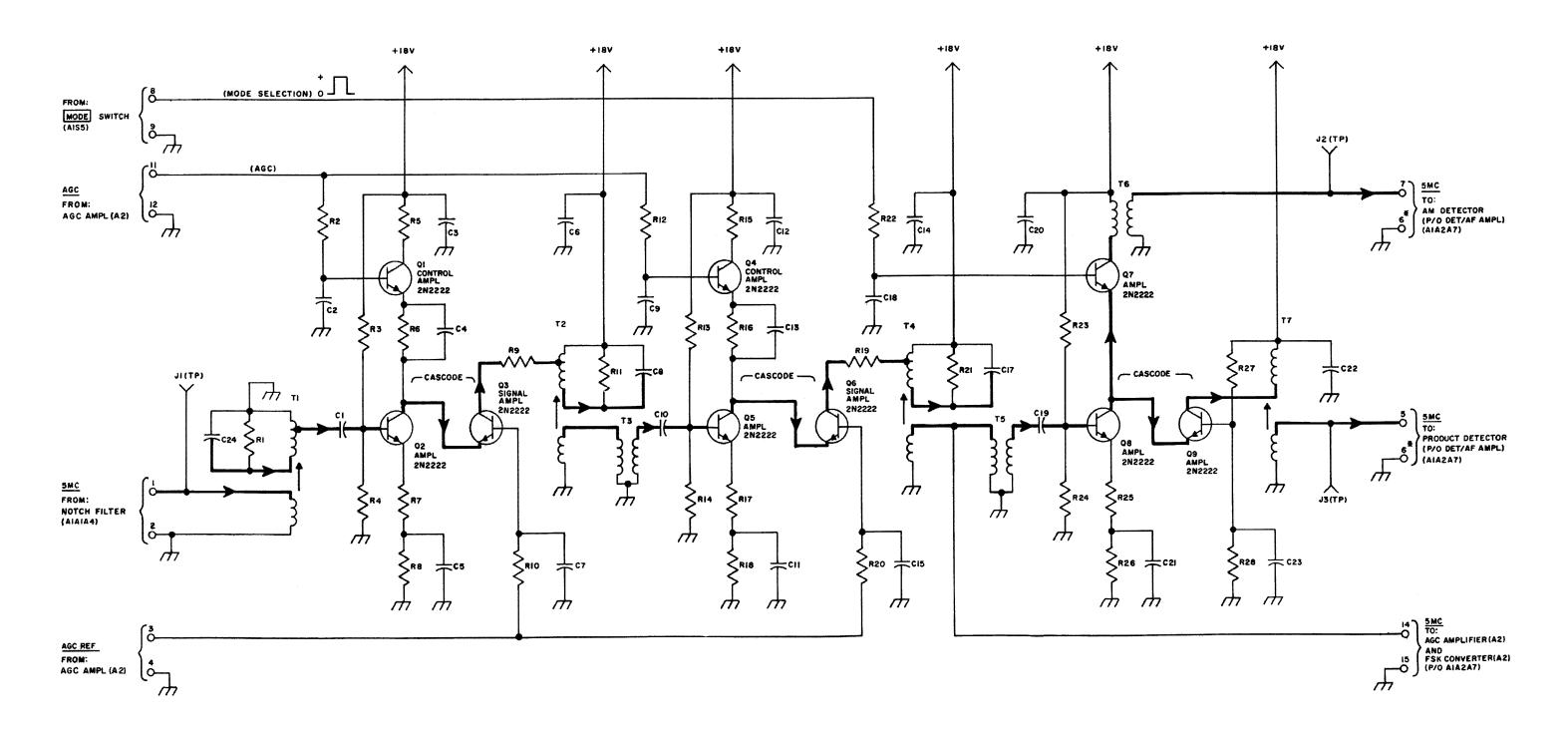

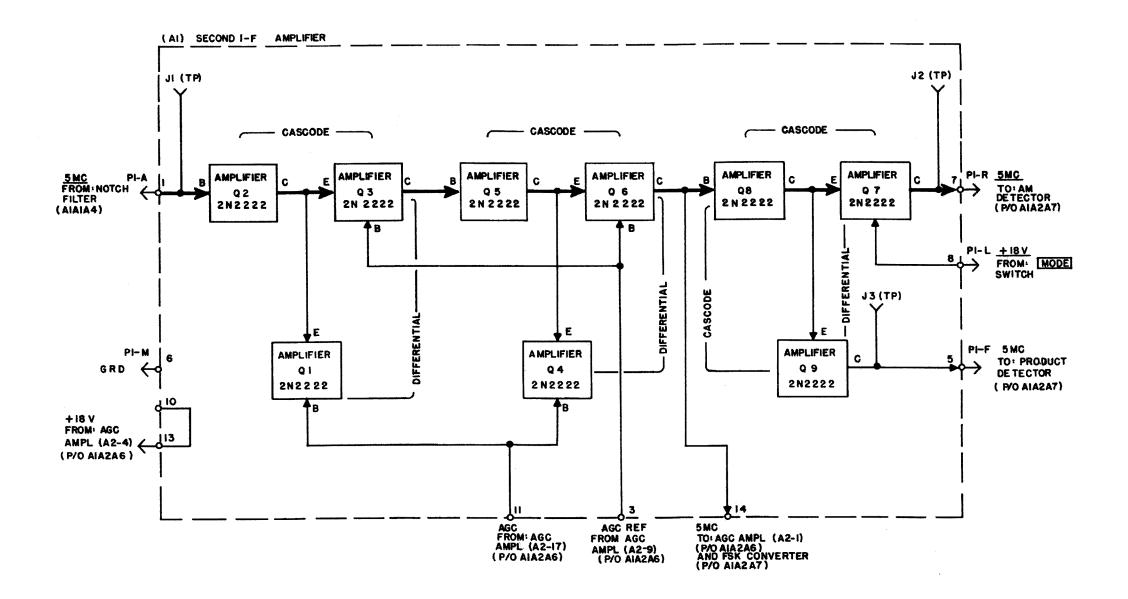

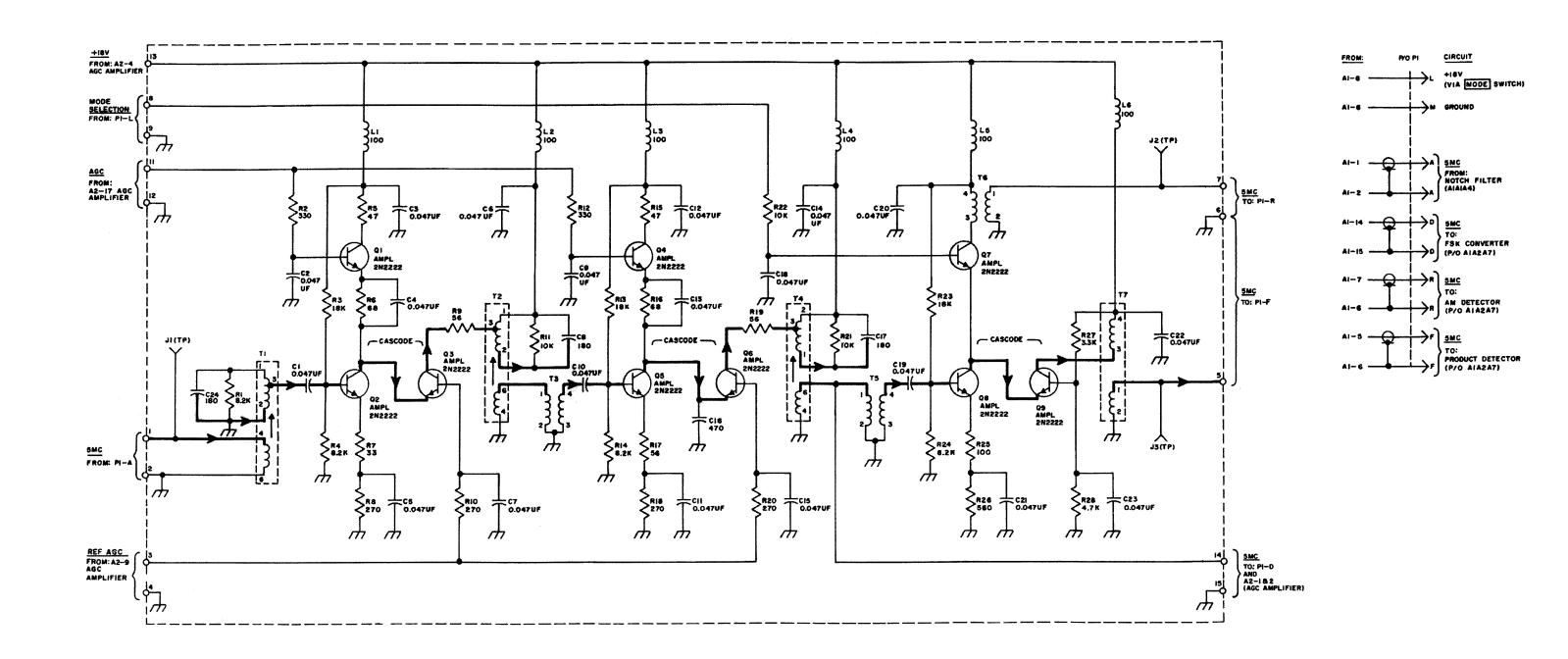

| 4-15   | Second I-F/AGC Amplifier A1A2A6; Second I-F Amplifier (A1), Simplified Schematic Diagram                           | 4-45  |

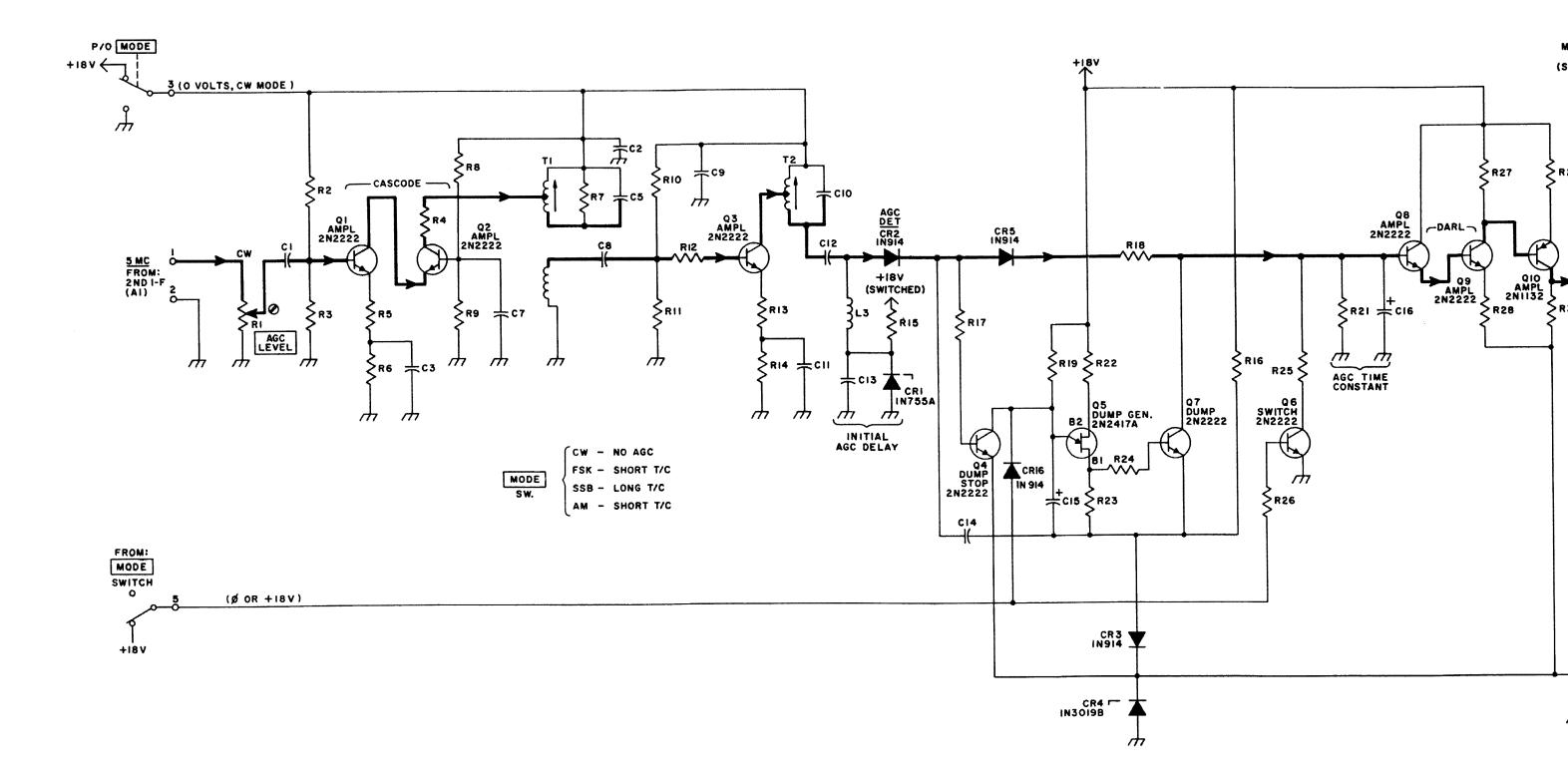

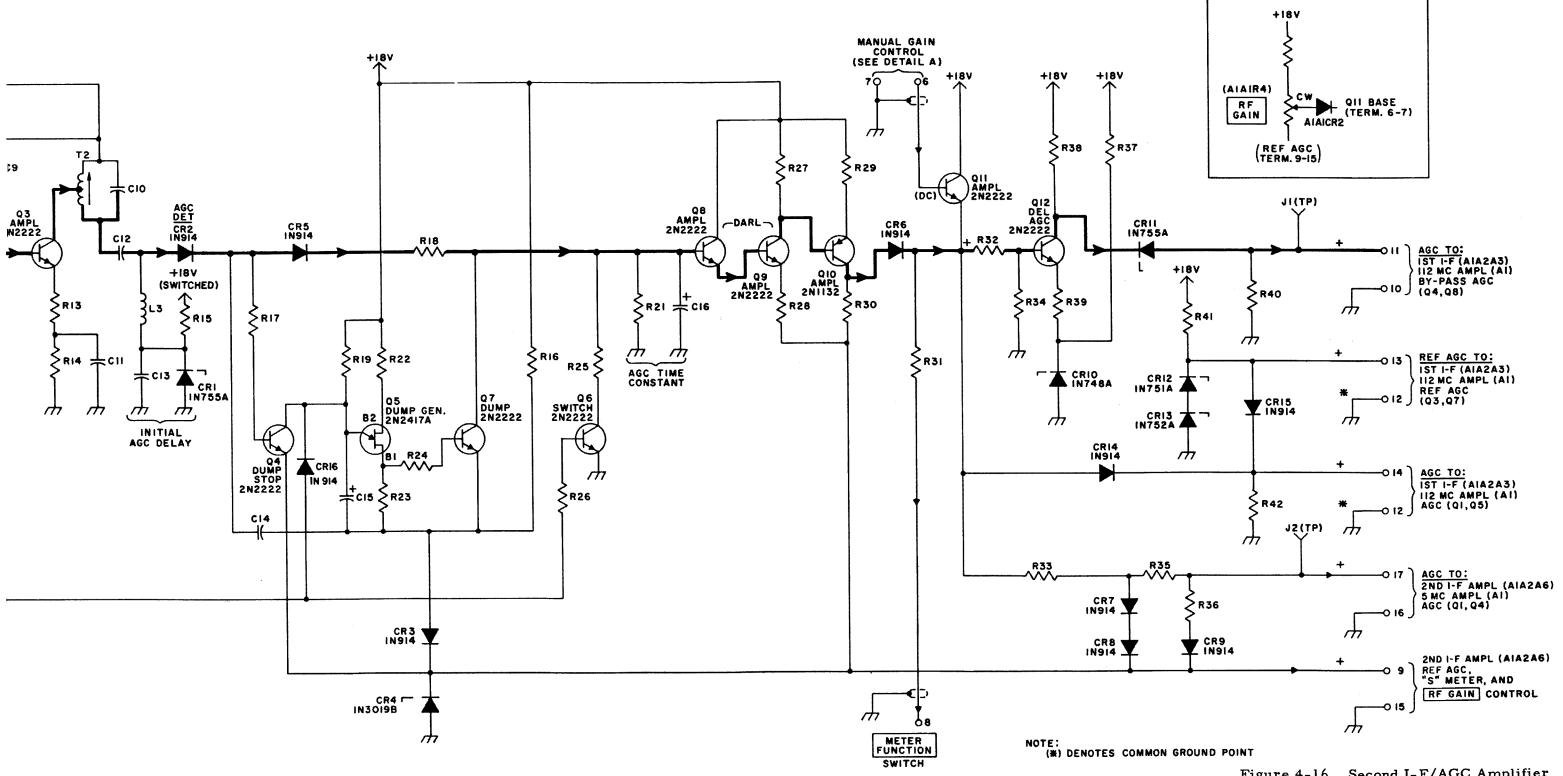

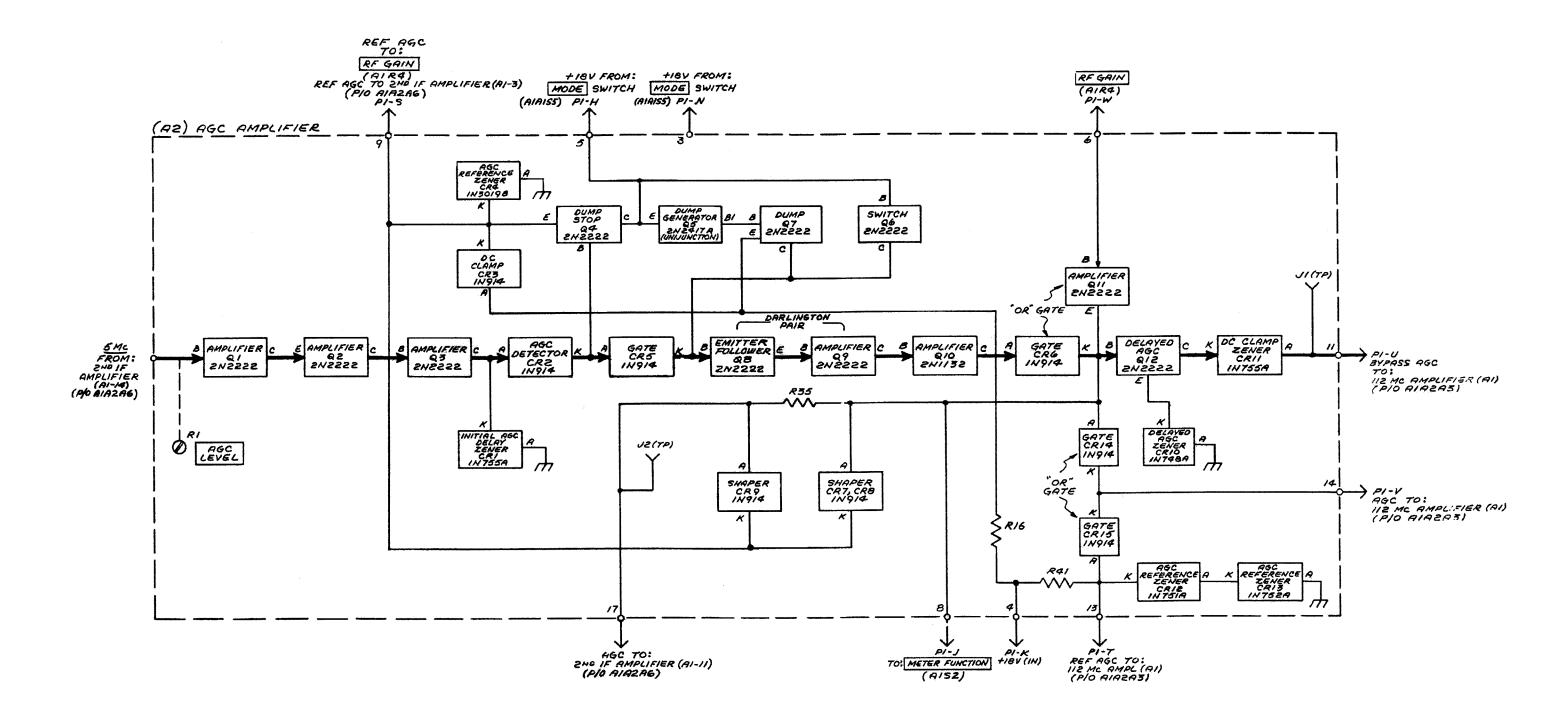

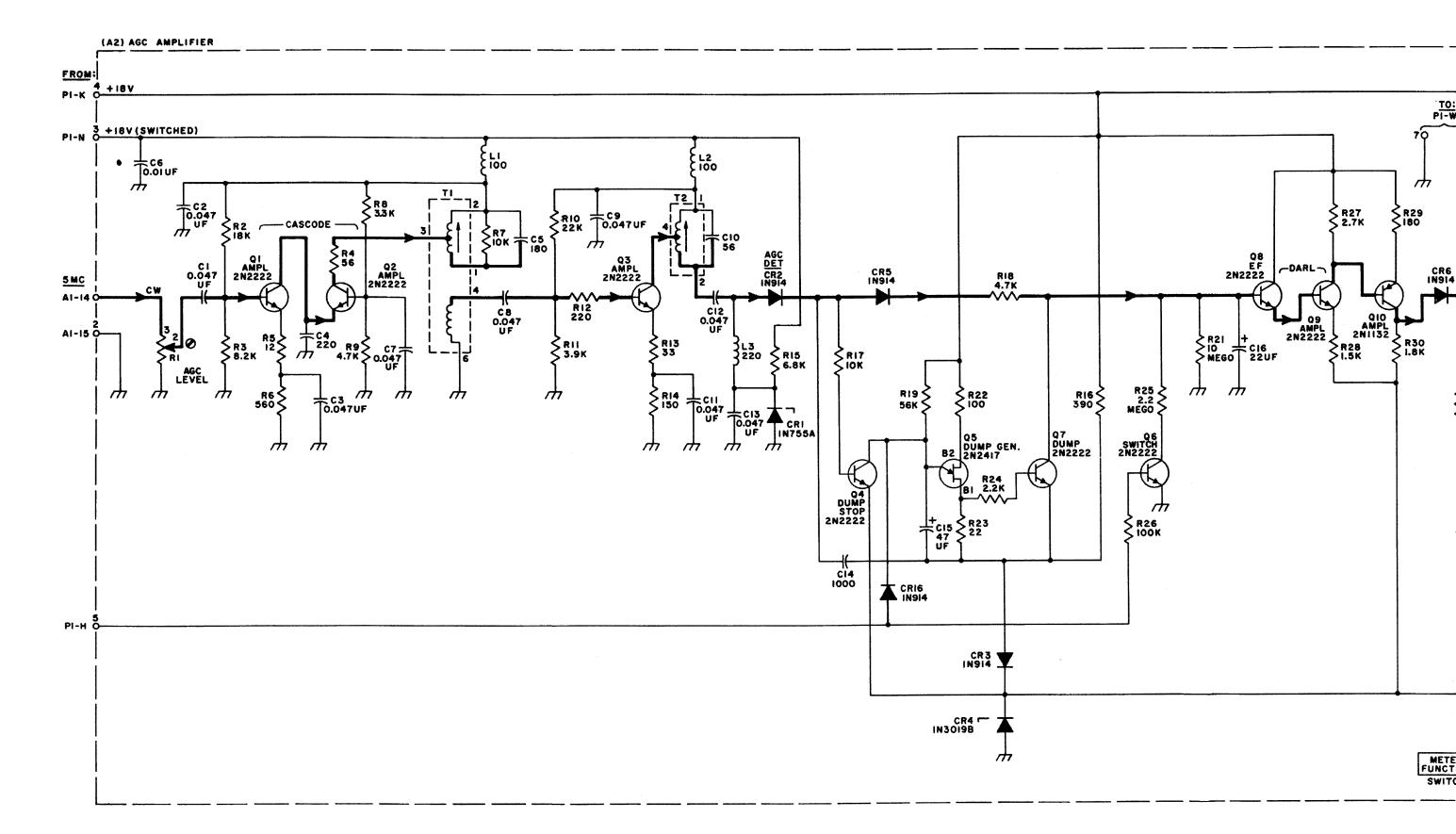

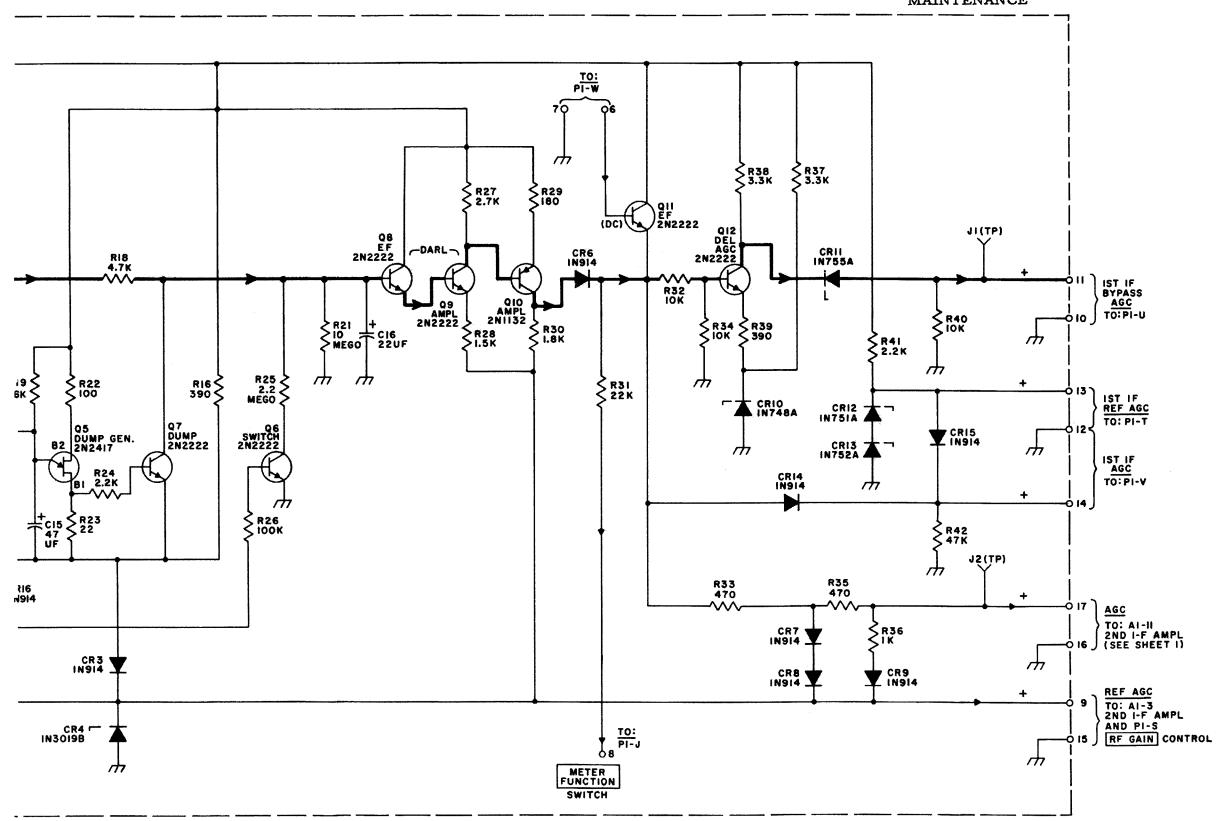

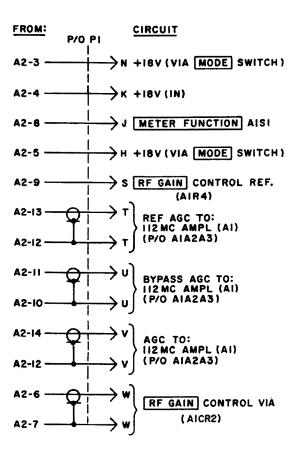

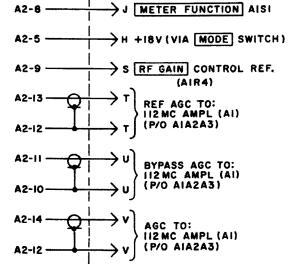

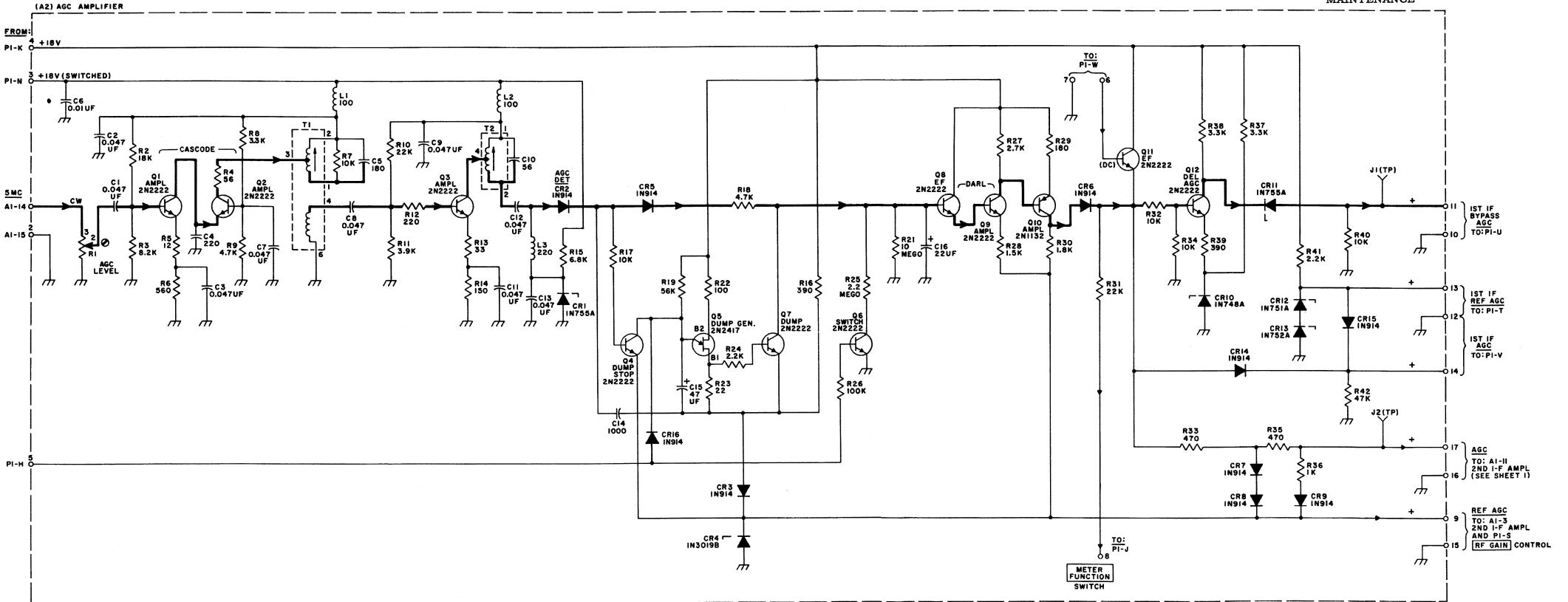

| 4-16   | Second I-F/AGC Amplifier AlA2A6; AGC Amplifier (A2),<br>Simplified Schematic Diagram                               | 4-47  |

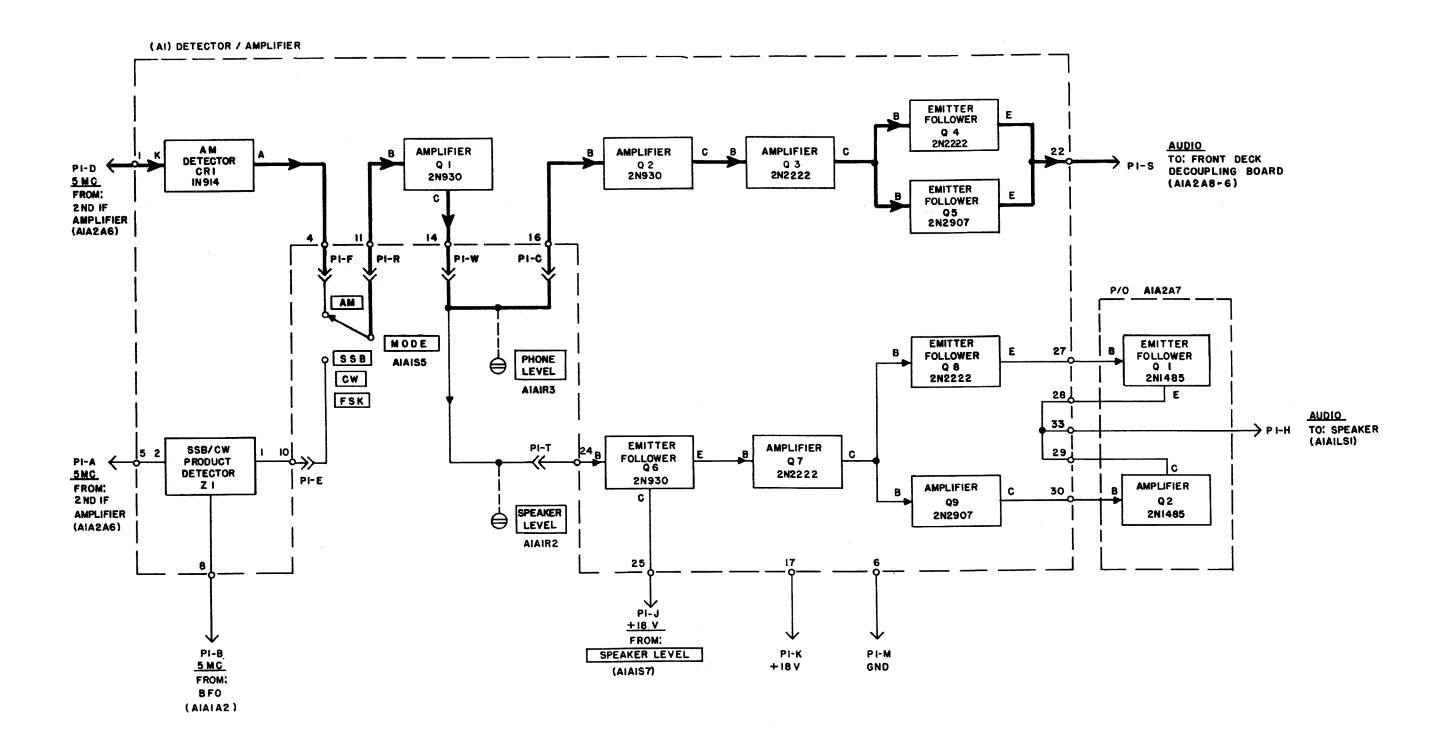

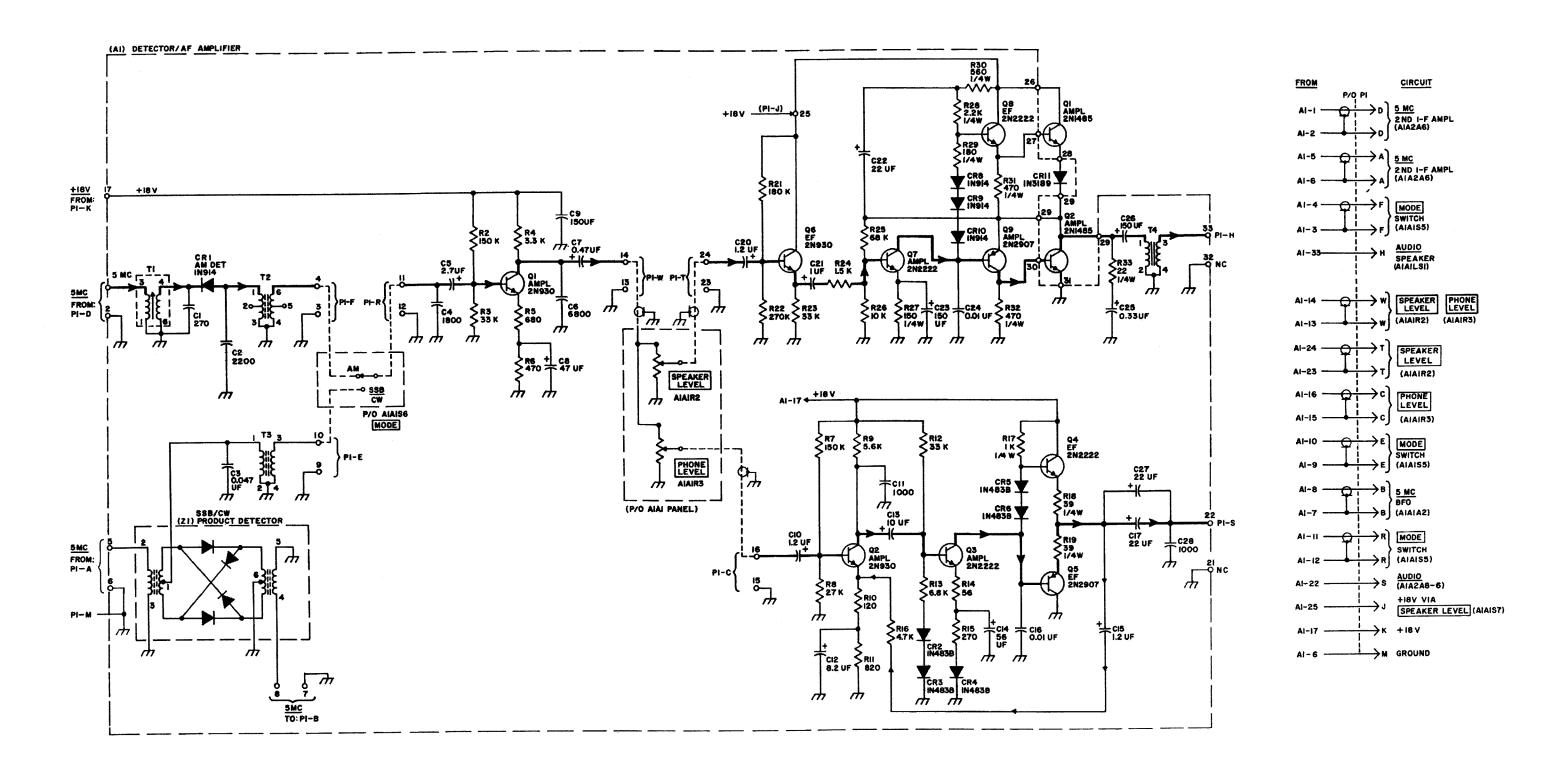

| 4-17   | Detector/AF Amplifier AlA2A7; Detector Circuits (p/o Al), Simplified Schematic Diagram                             | 4-53  |

| 4-18   | Detector/AF Amplifier AlA2A7; Headset Amplifier (p/o Al), Simplified Schematic Diagram                             | 4-54  |

| 4-19   | Detector/AF Amplifier A1A2A7; Speaker Amplifier (p/o A1), Simplified Schematic Diagram                             | 4-56  |

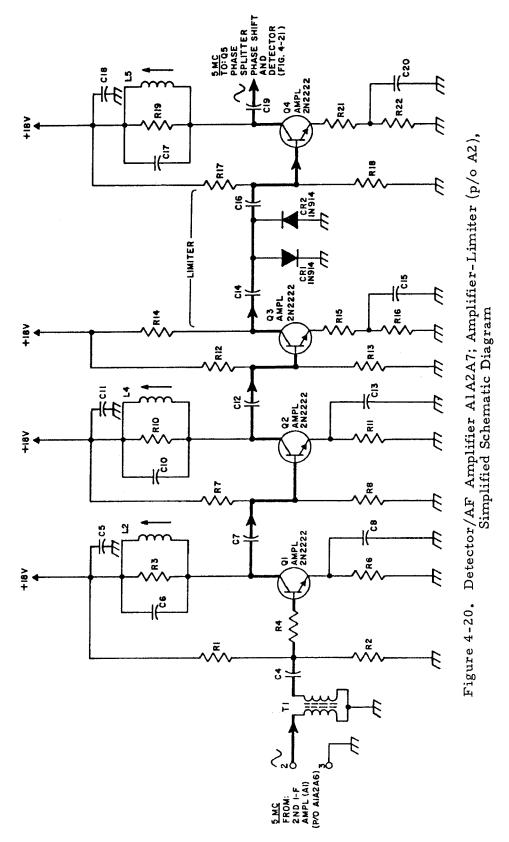

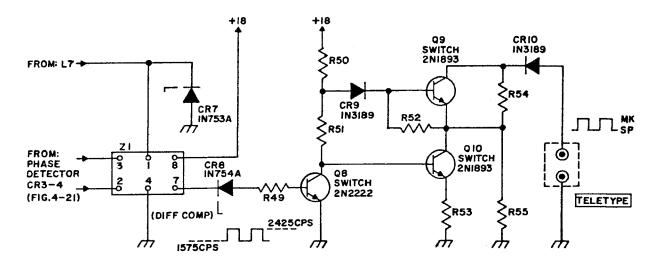

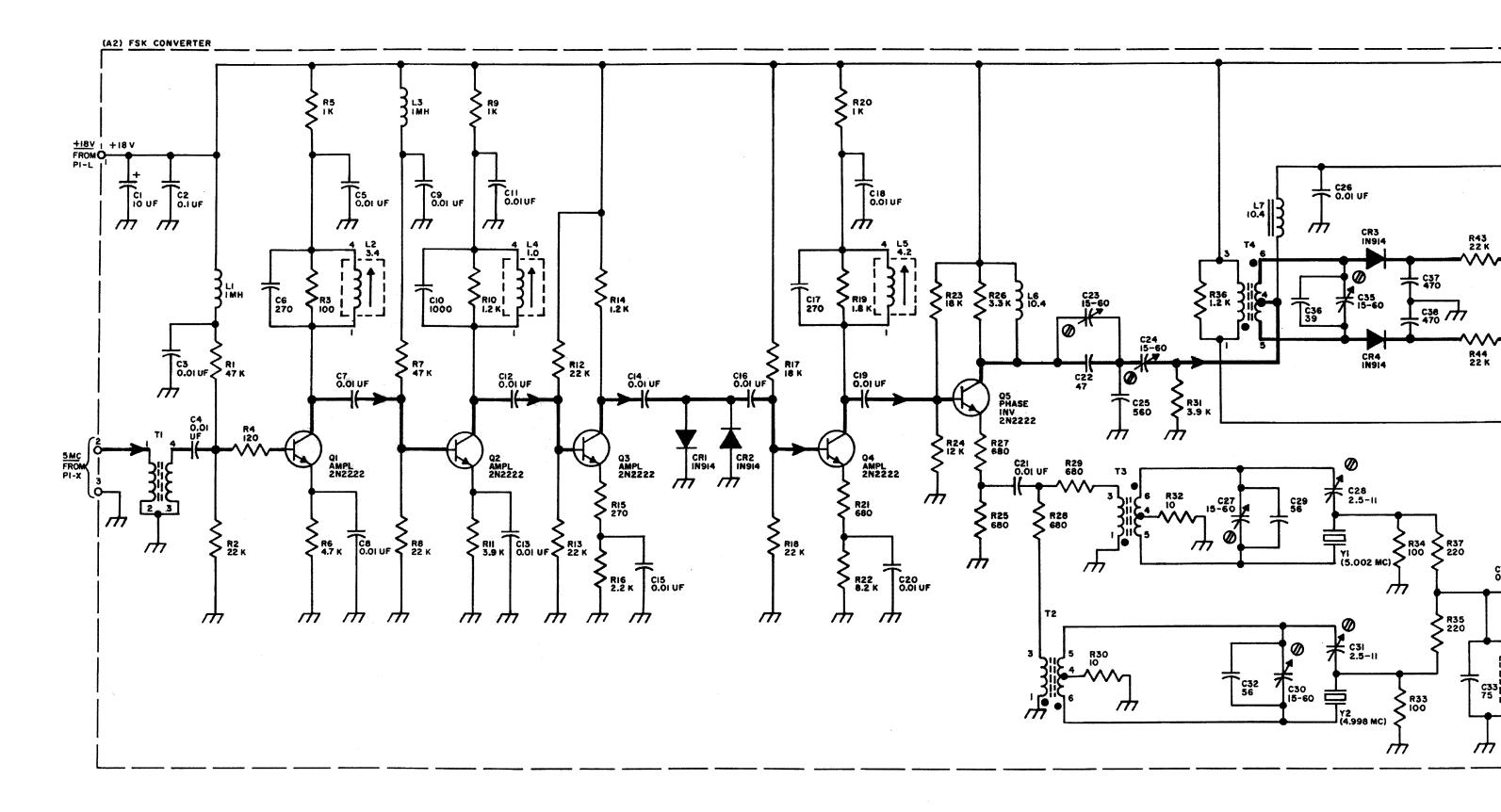

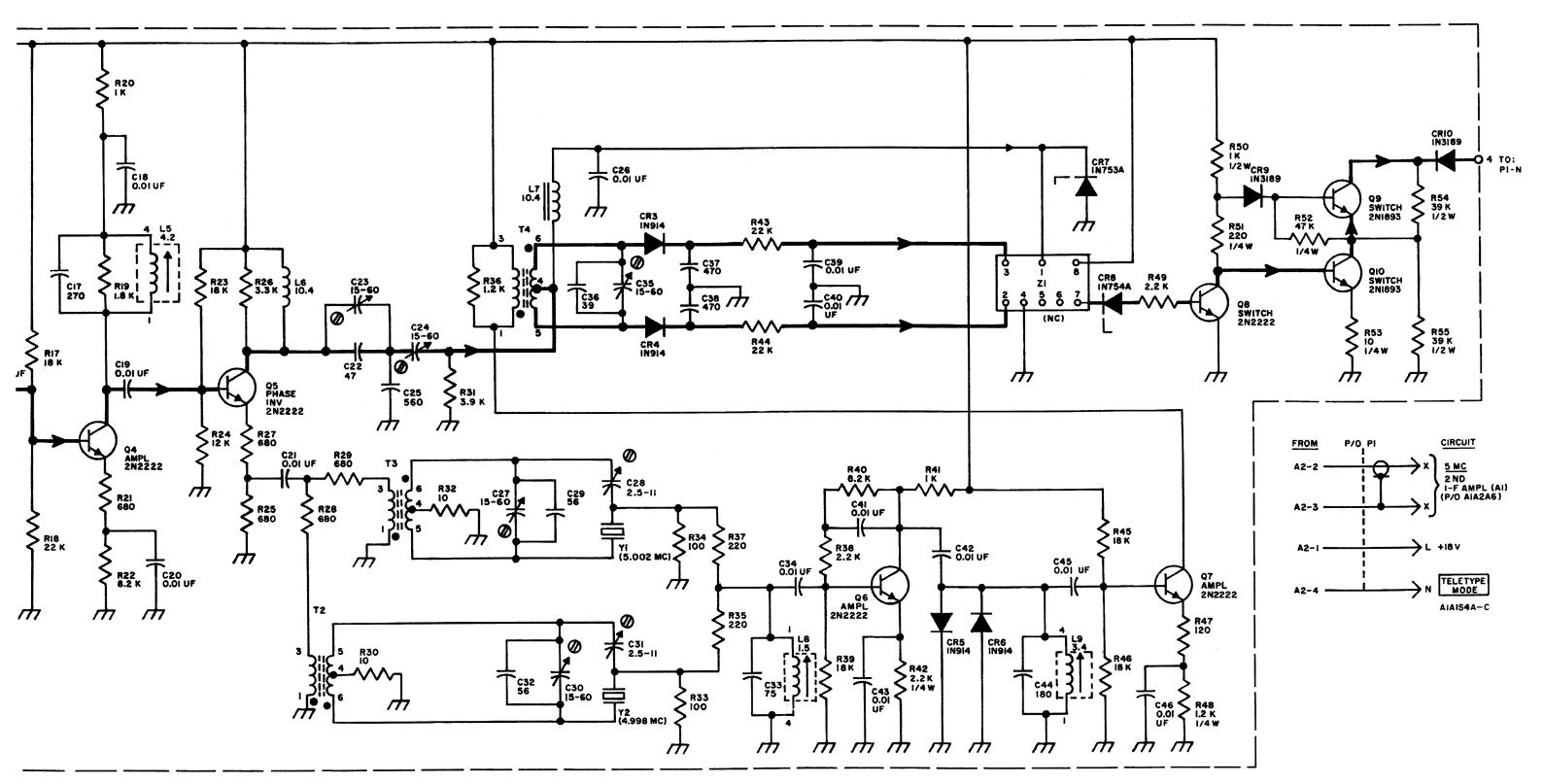

| 4-20   | Detector/AF Amplifier A1A2A7; Amplifier-Limiter (p/o A2),<br>Simplified Schematic Diagram                          | 4-57  |

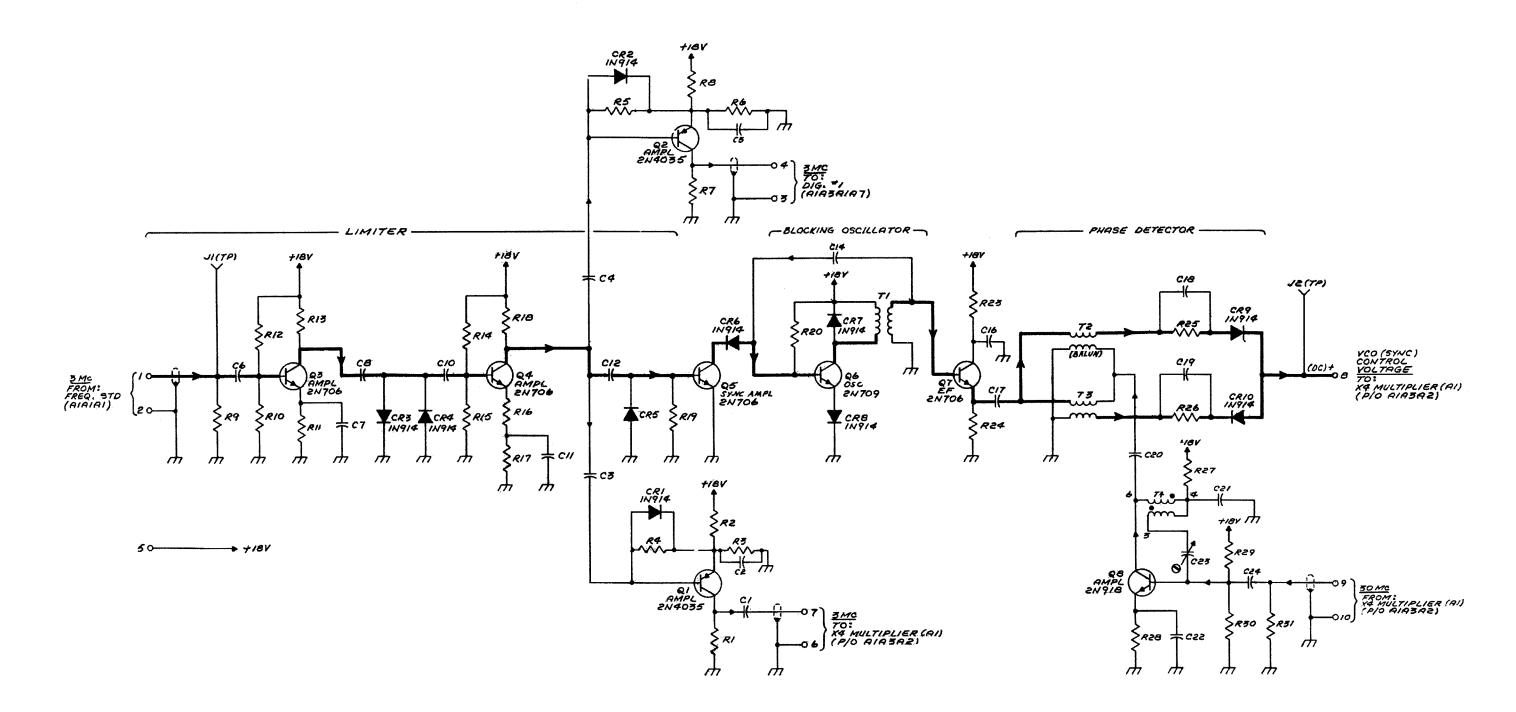

| 4-21   | Detector/AF Amplifier A1A2A7; Phase Detector (p/o A2), Simplified Schematic Diagram                                | 4-58  |

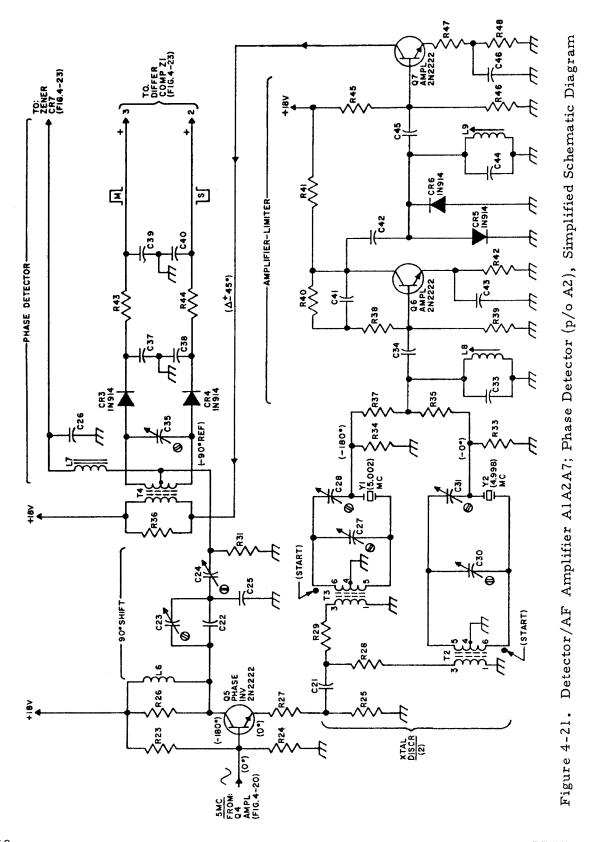

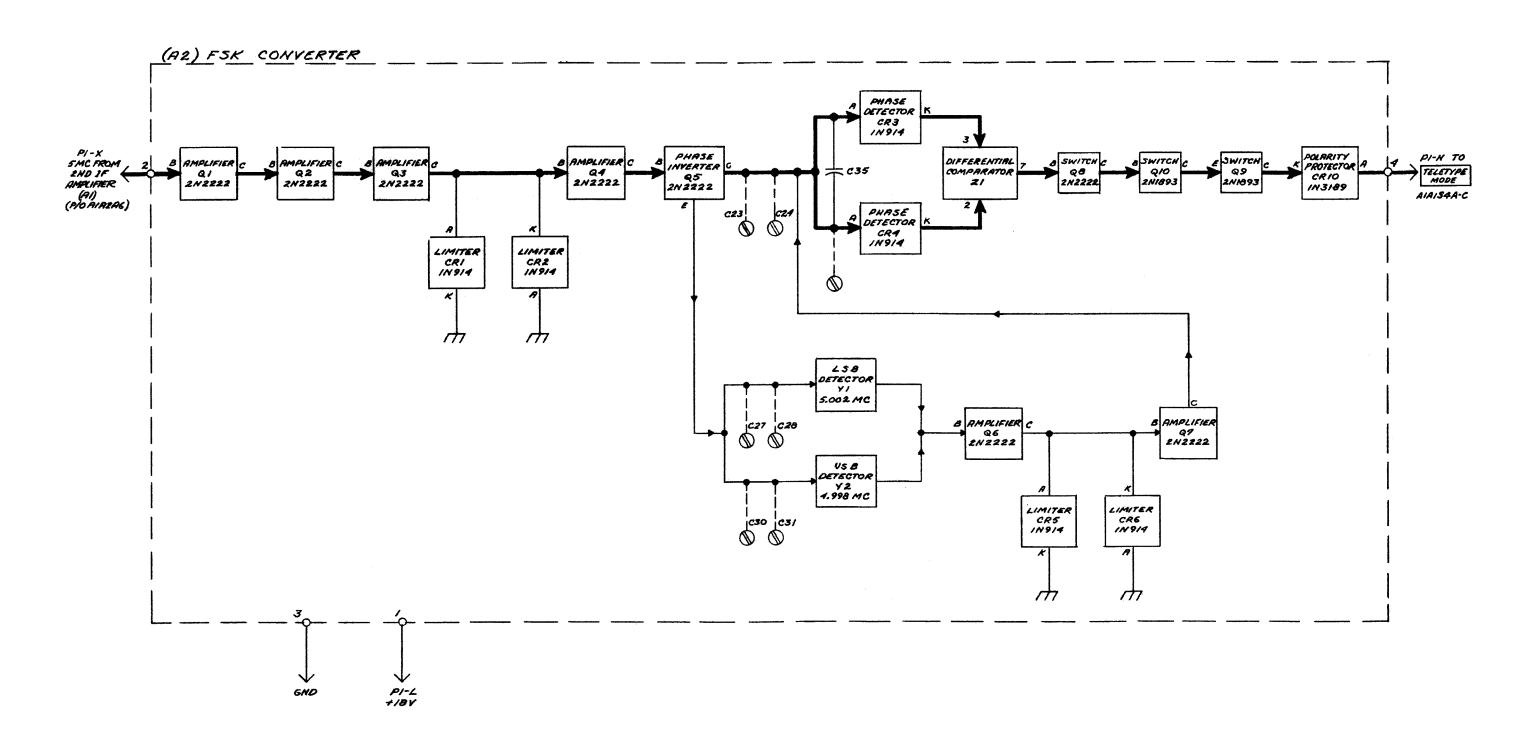

| 4-22   | Detector/AF Amplifier AlA2A7; Phase Detector (p/o A2), Functional Block Diagram                                    | 4-60  |

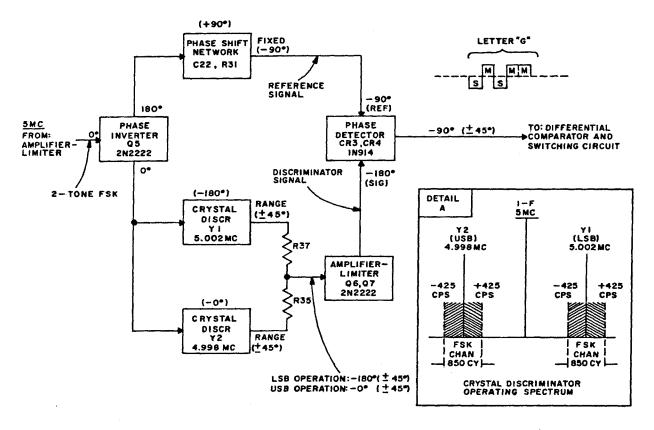

| 4-23   | Detector/AF Amplifier A1A2A7; Switching Circuit (p/o A2), Simplified Schematic Diagram                             | 4-61  |

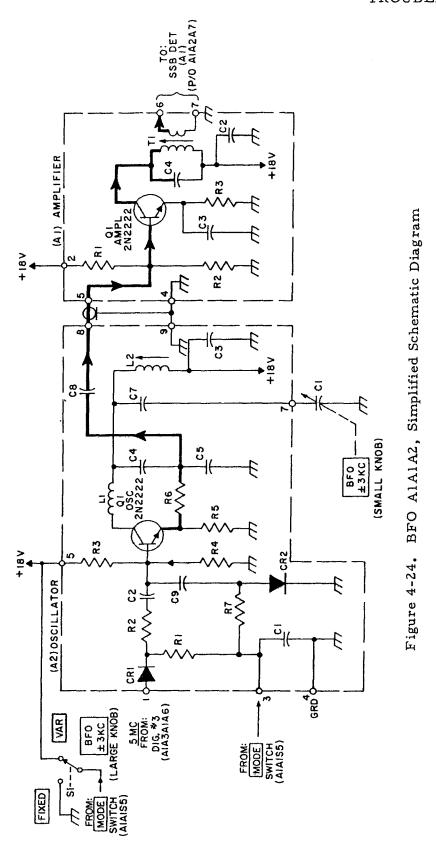

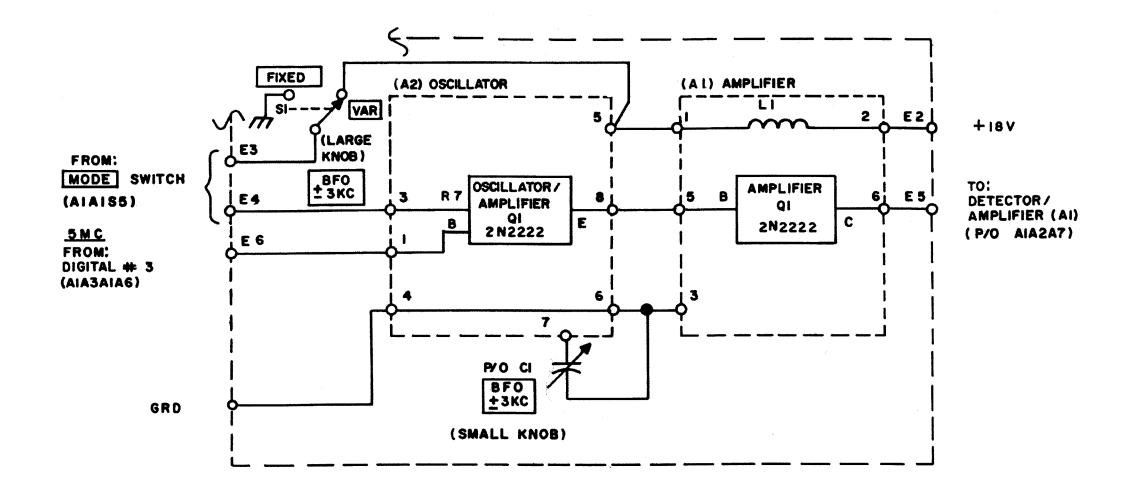

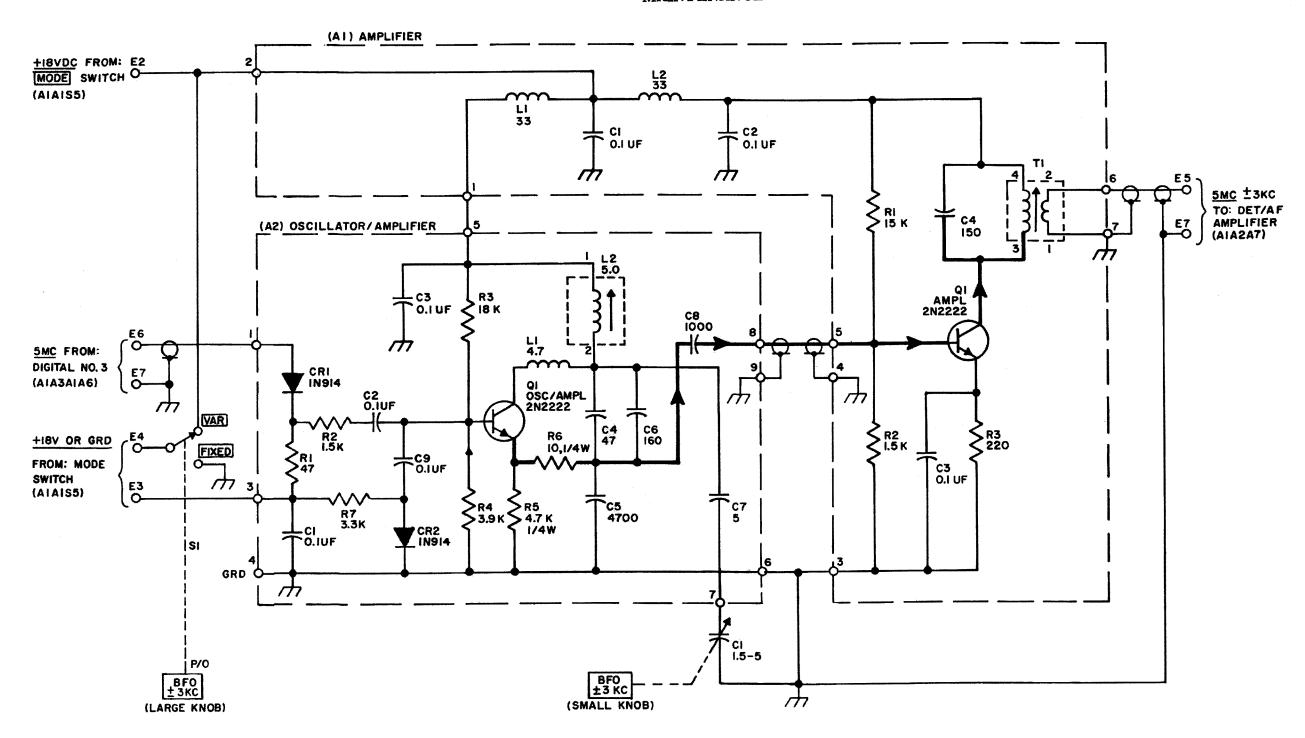

| 4-24   | BFO AlAlA2, Simplified Schematic Diagram                                                                           | 4-64  |

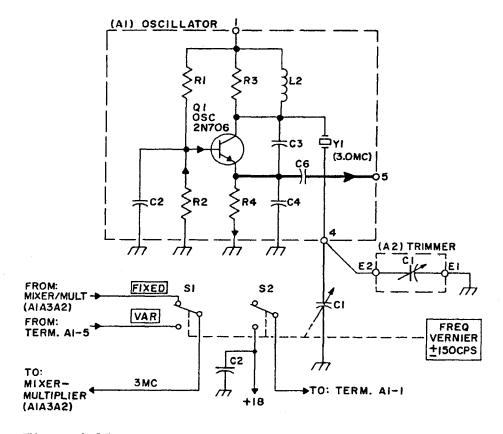

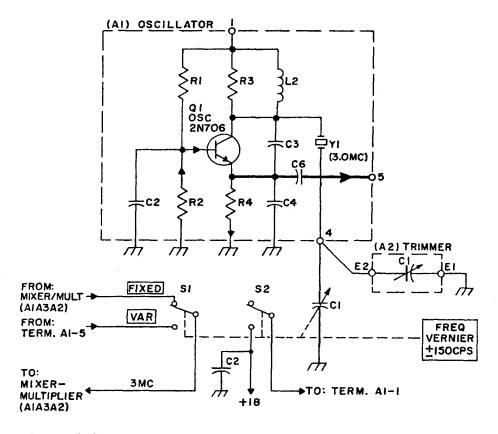

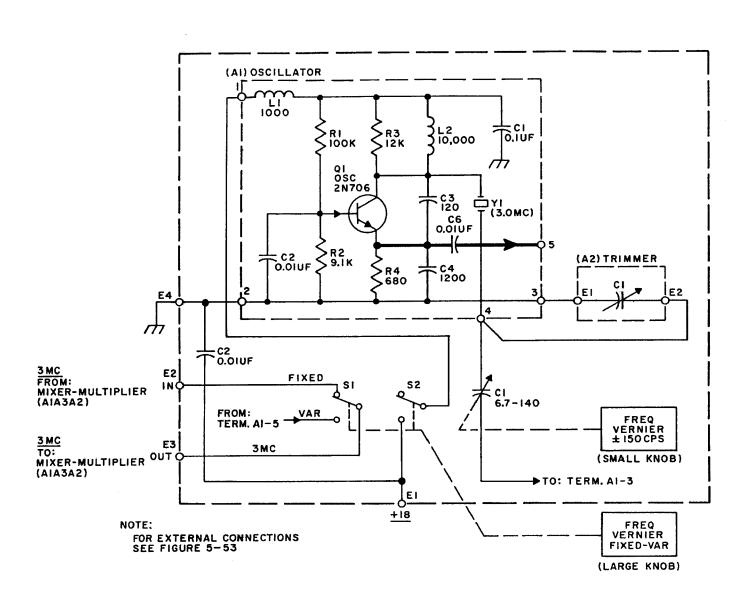

| 4-25   | VFO AlAlA3, Simplified Schematic Diagram                                                                           | 4-66  |

| 4-26   | Synthesizer AlA3Al, Simplified Block Diagram                                                                       | 4-68  |

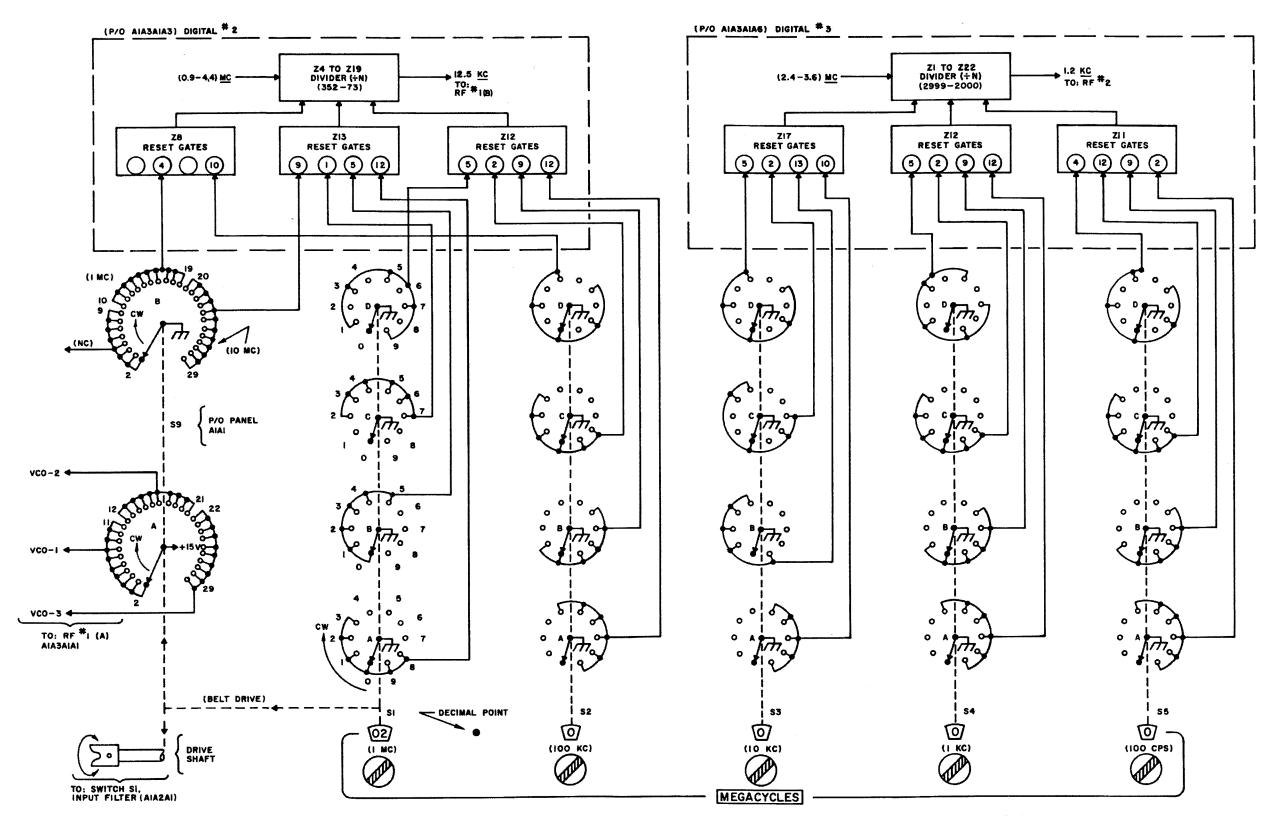

| 4-27   | MEGACYCLES Frequency Selector AlAlA5, Functional Diagram                                                           | 4-77  |

| 4-28   | RF #1(A) AlA3AlA1; Filter-Amplifier, Simplified Schematic Diagram                                                  | 4-82  |

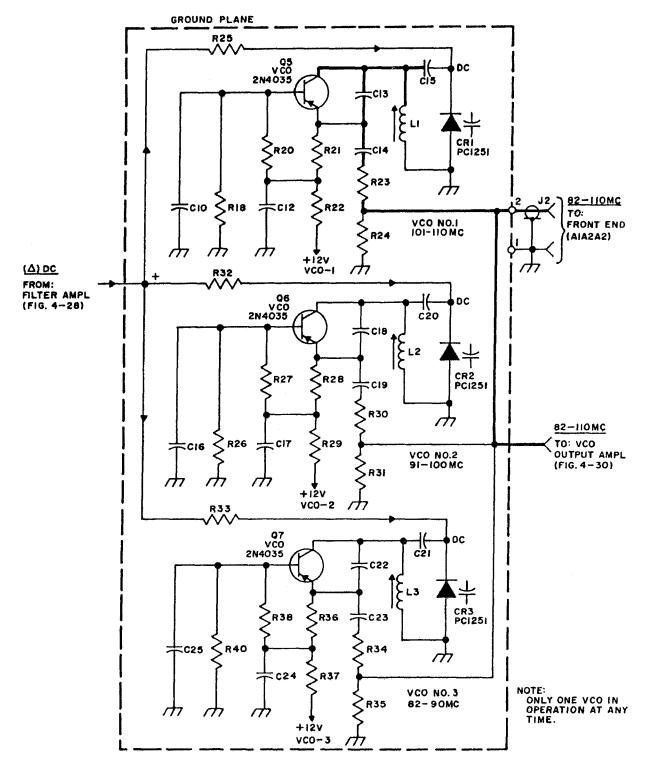

| 4-29   | RF #1(A) AlA3AlA1; VCO Circuits, Simplified Schematic Diagram                                                      | 4-84  |

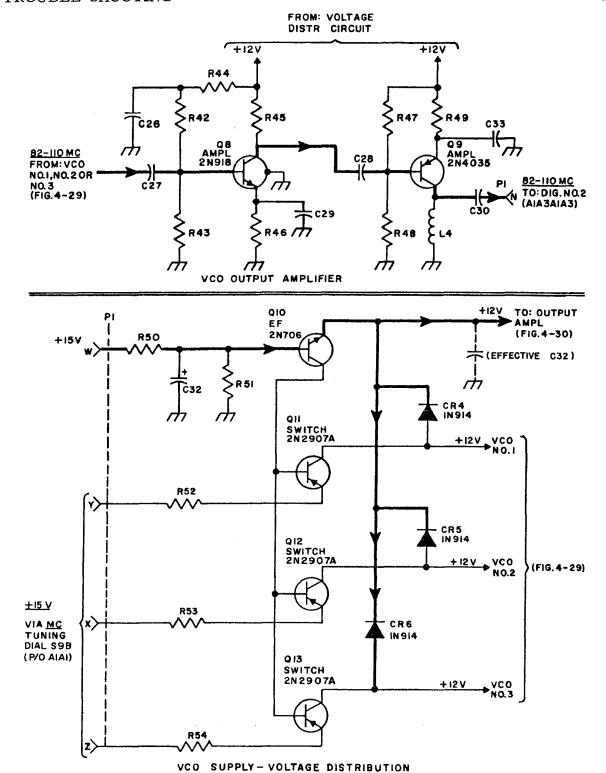

| 4-30   | RF #1(A) A1A3A1A1; VCO Output Amplifier and VCO Supply-Voltage Distribution Circuit, Simplified Schematic Diagrams | 4-85  |

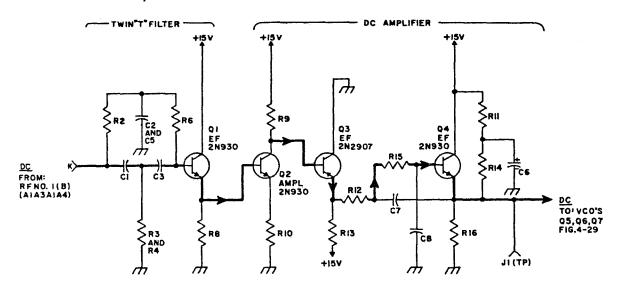

| 4-31   | RF #1(B) A1A3A1A4; Simplified Schematic Diagram                                                                    | 4-87  |

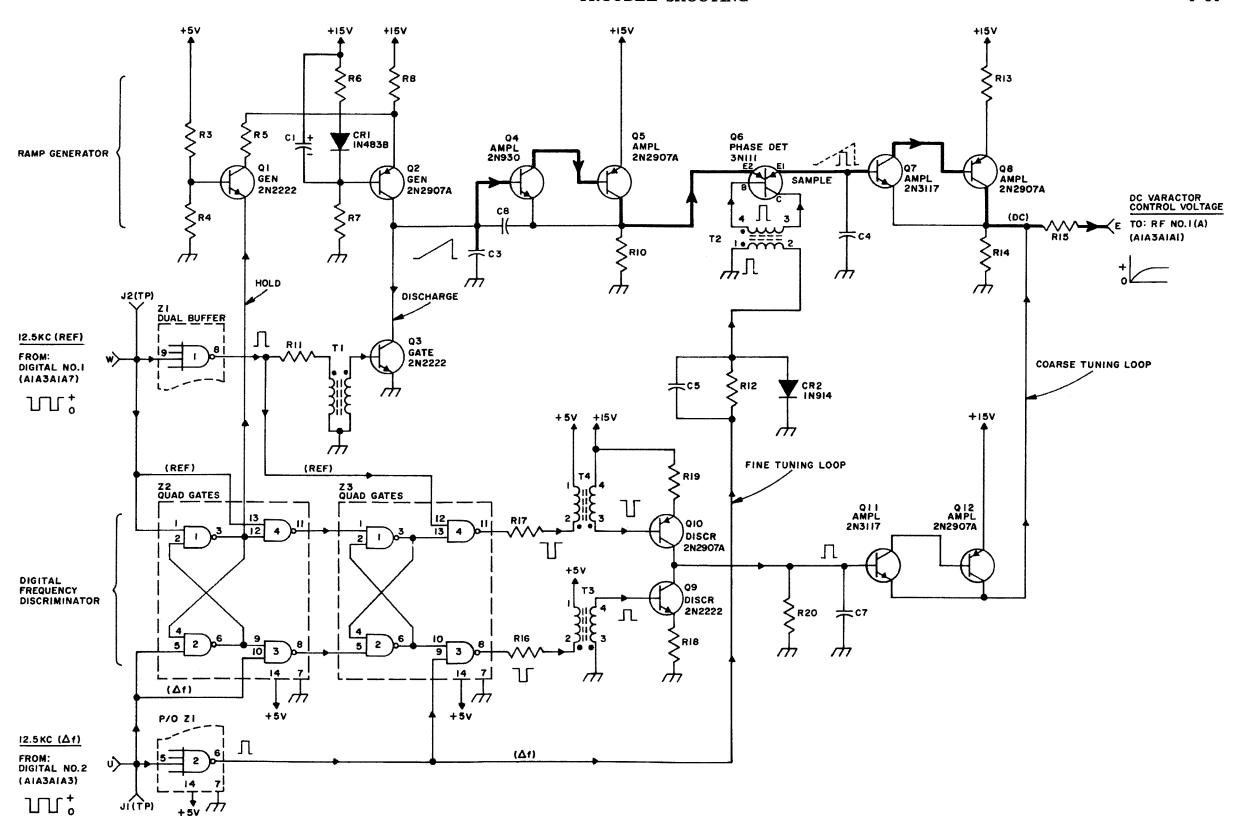

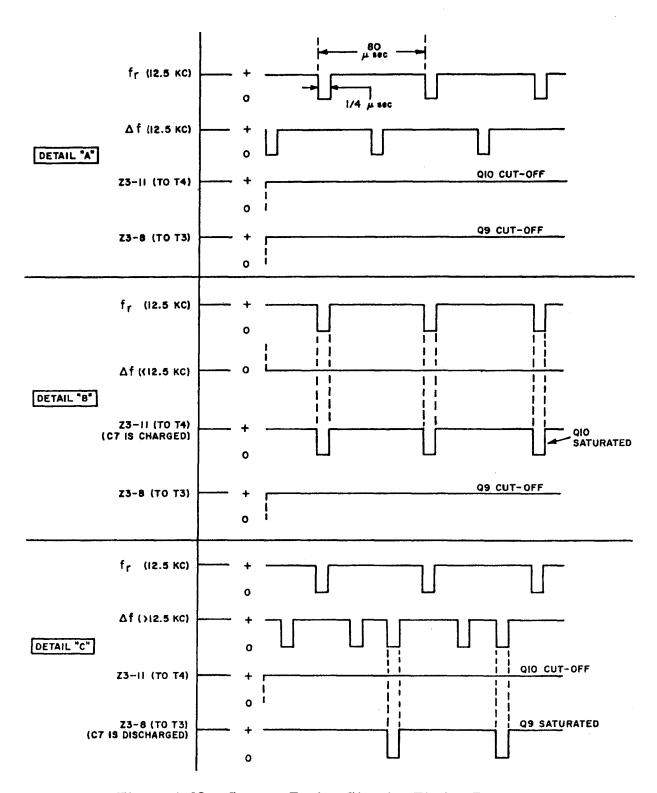

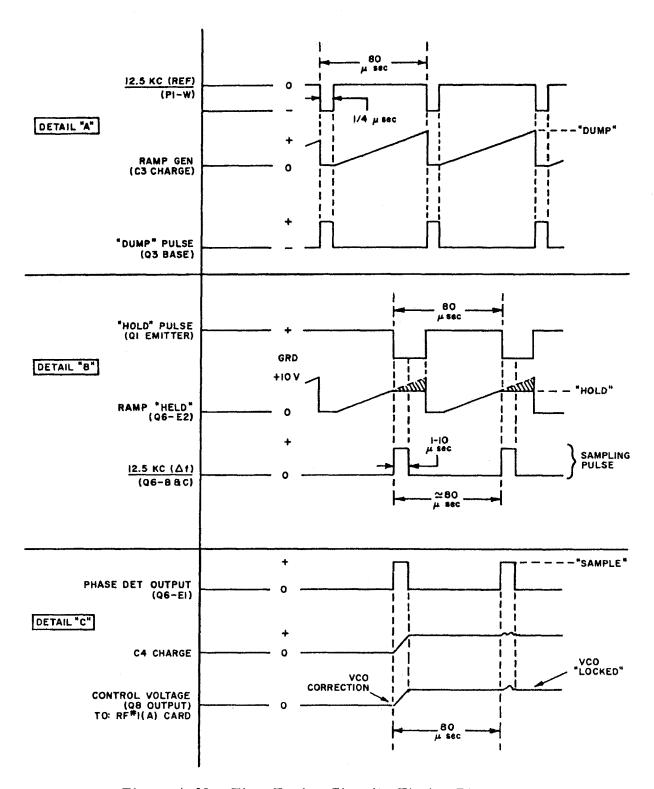

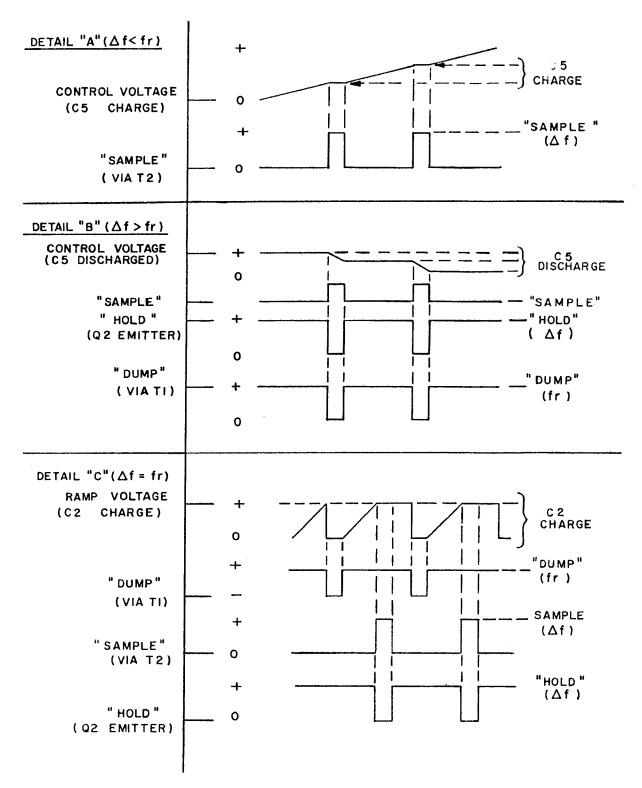

| 4-32   | Coarse-Tuning Circuit, Timing Diagram                                                                              | 4-90  |

| 4-33   | Fine-Tuning Circuit, Timing Diagram                                                                                | 4-94  |

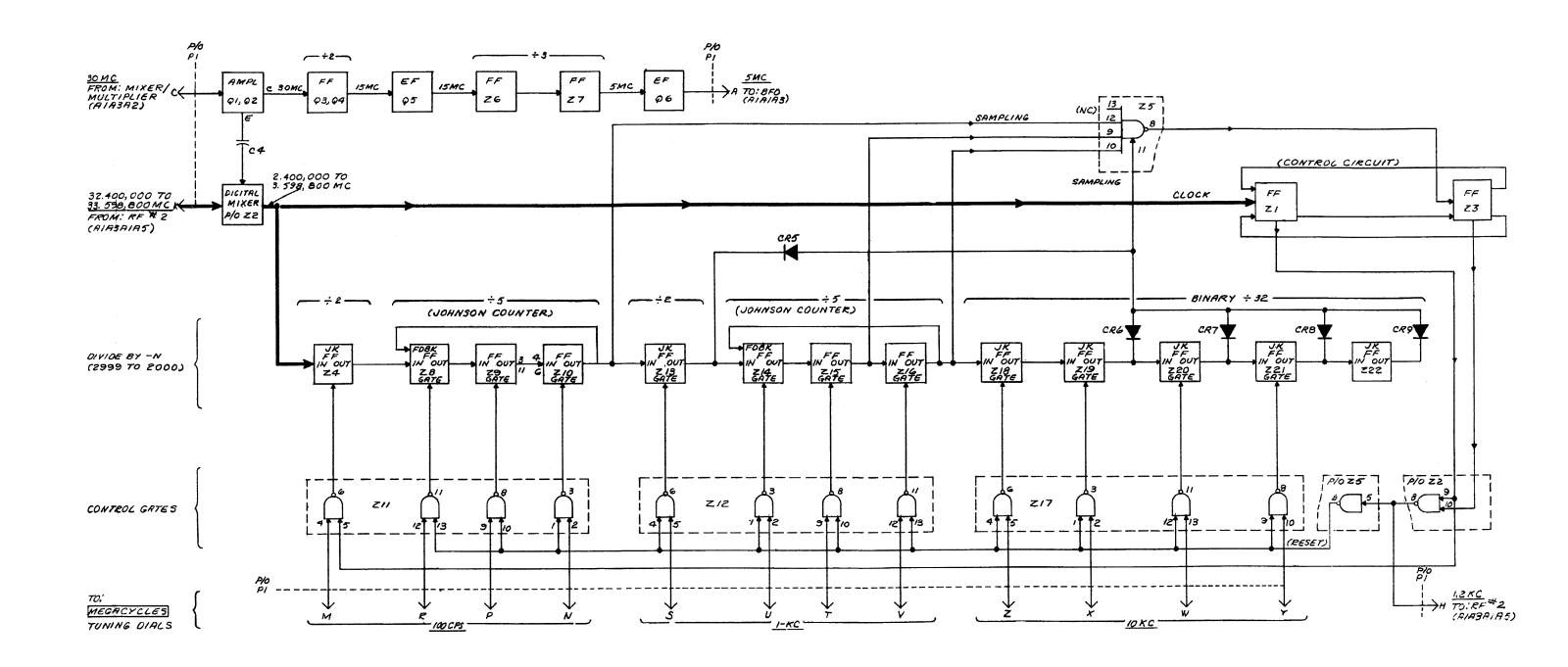

| 4-34   | Digital #2 AlA3AlA3, Simplified Block Diagram                                                                      | 4-97  |

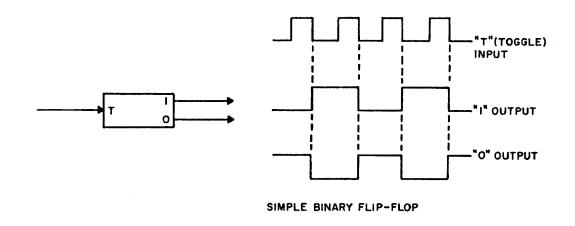

| 4-35   | Comparison, Triggered Binary Flip-Flops                                                                            | 4-99  |

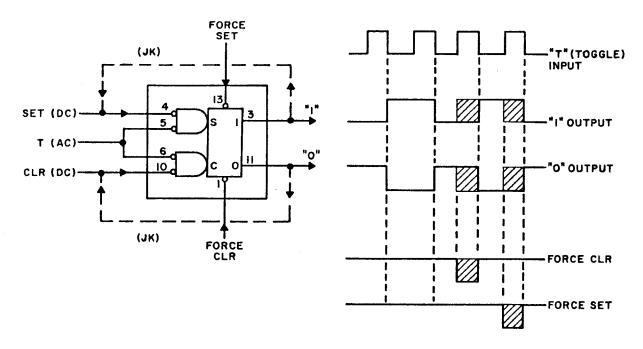

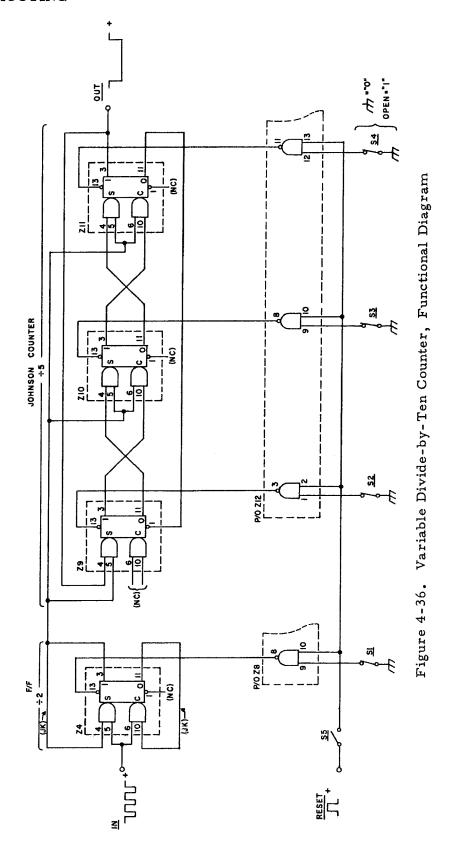

| 4-36   | Variable Divide-by-Ten Counter, Functional Diagram                                                                 | 4-101 |

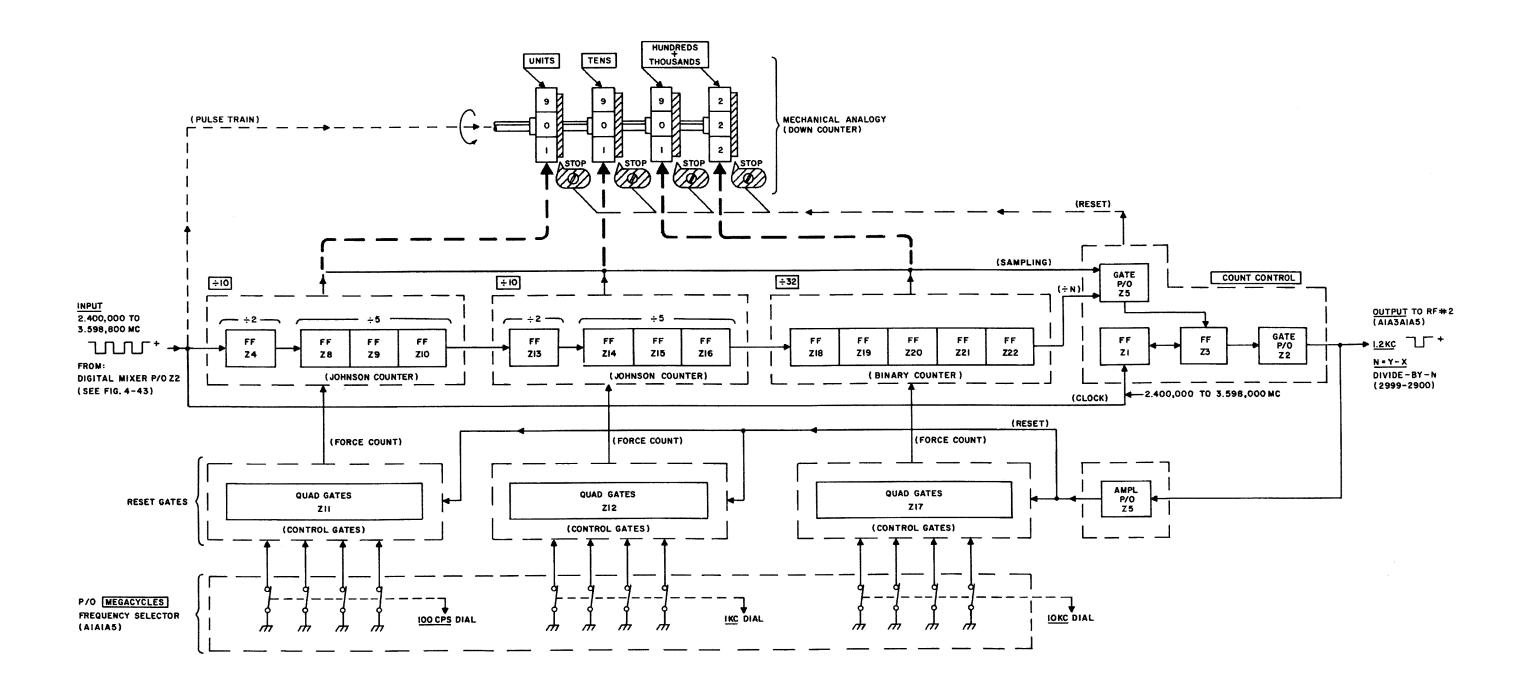

| 4-37   | Digital #2 Divide-by-N Counter, Mechanical Analogy                                                                 | 4-103 |

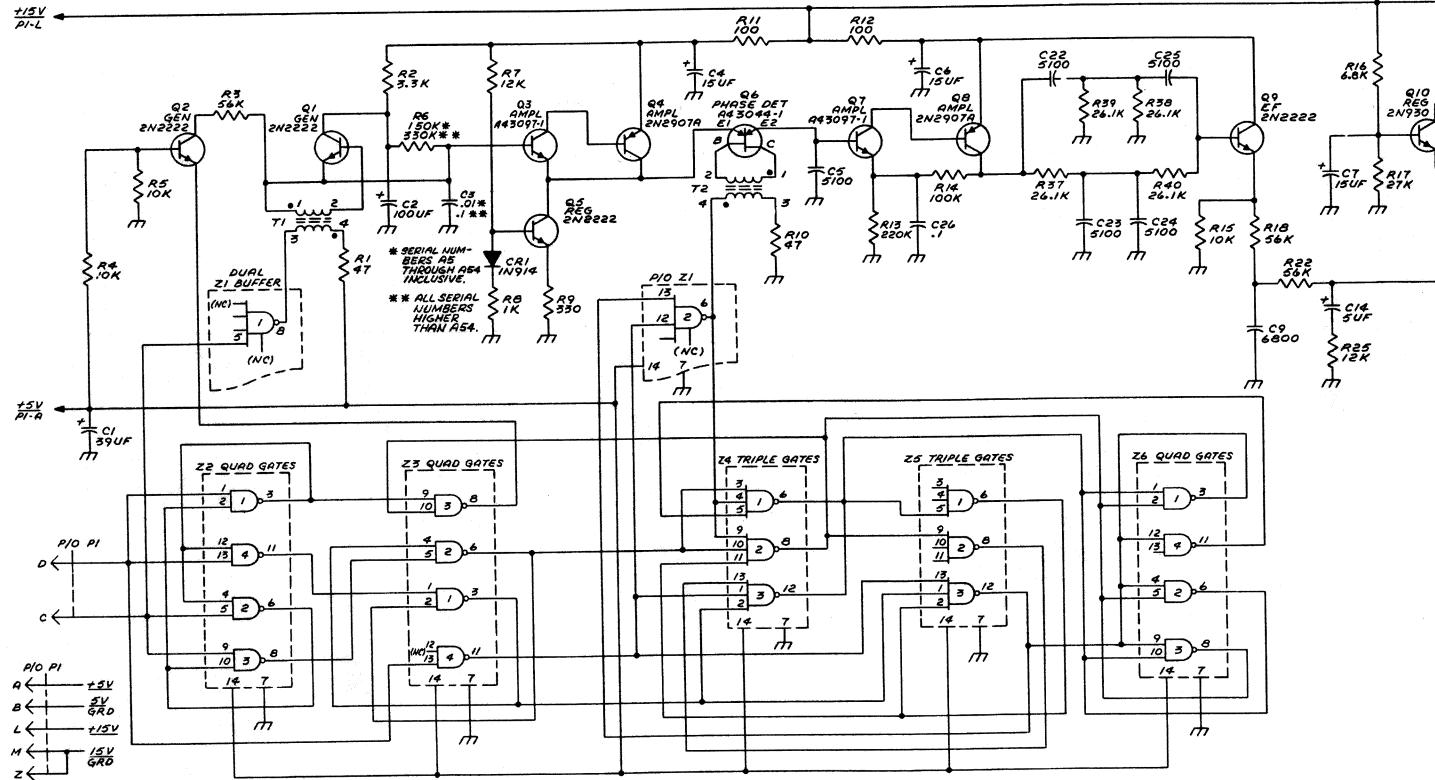

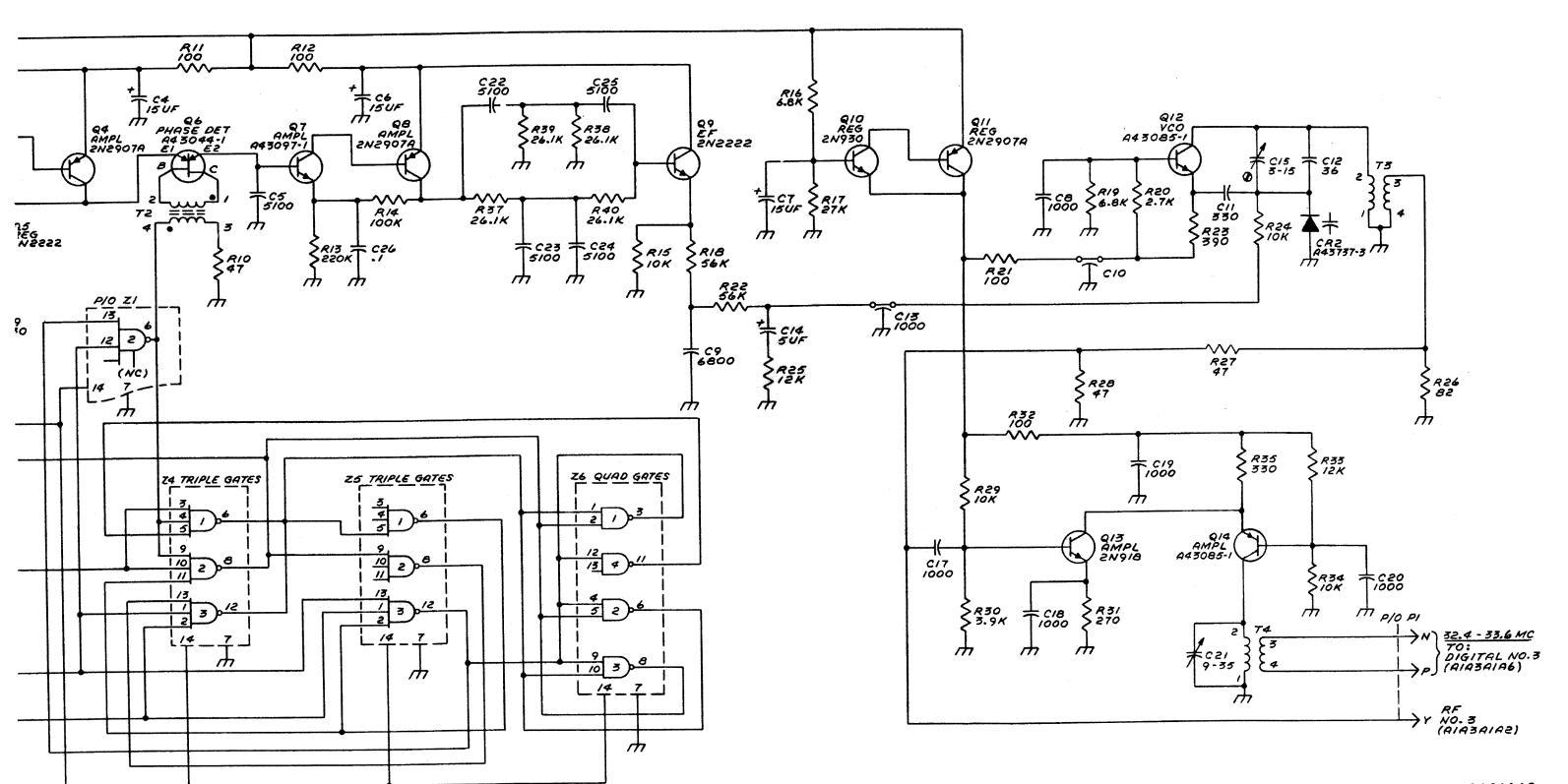

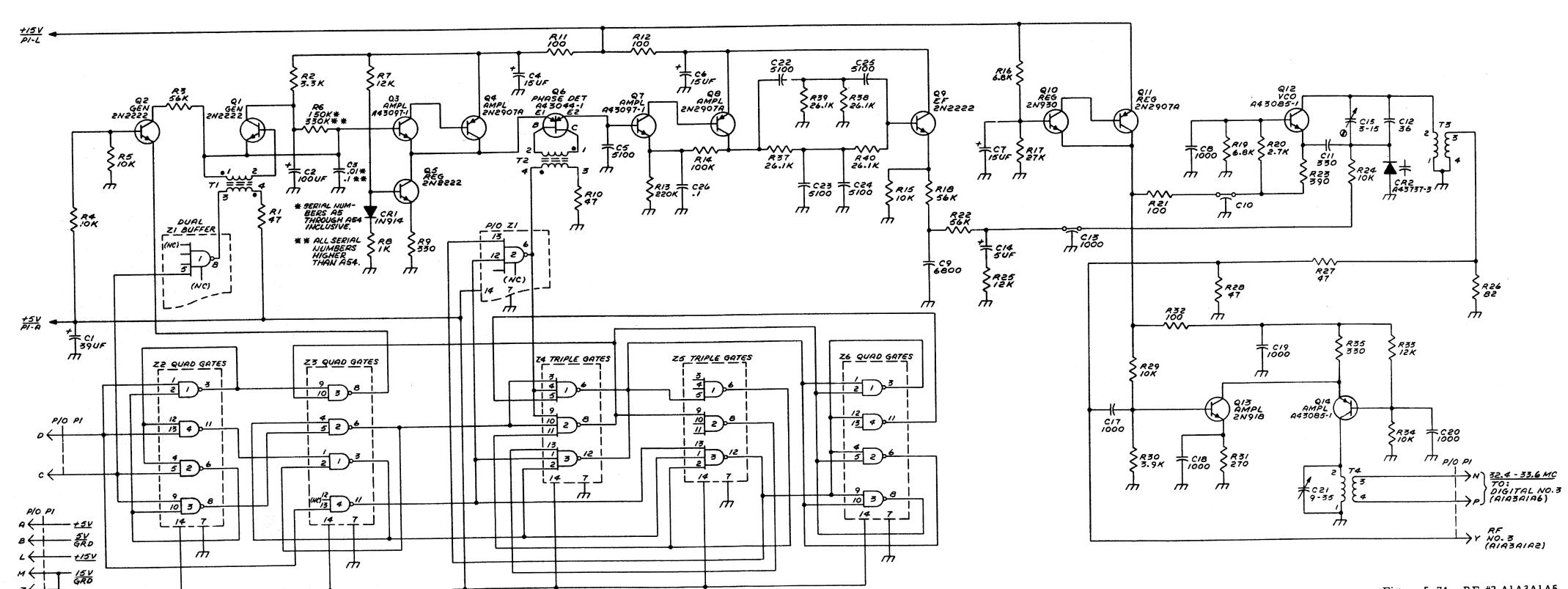

| 4-38   | RF #3 AlA3AlA2, Simplified Schematic Diagram                                                                       | 4-107 |

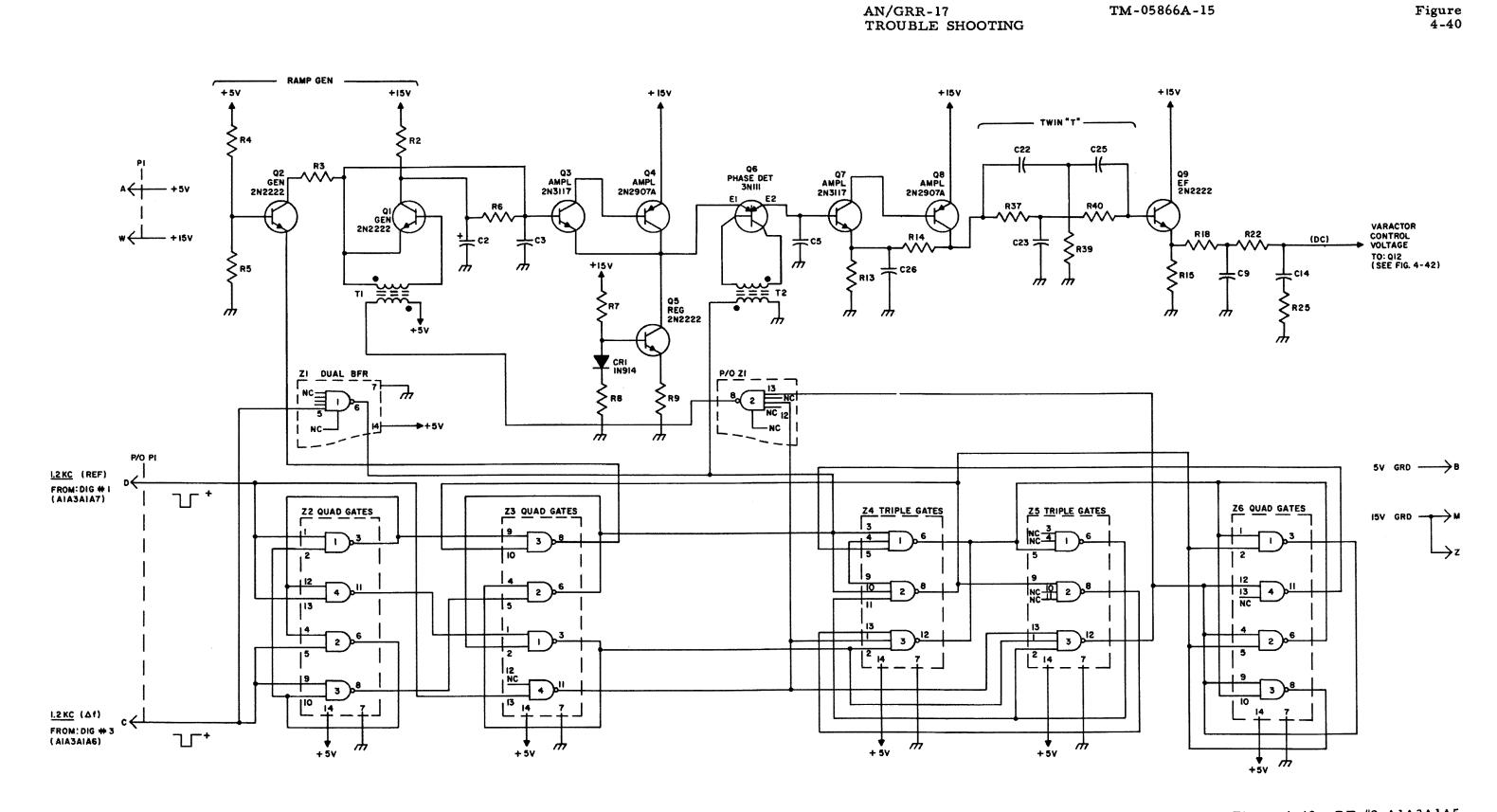

| 4-39   | Timing Diagram, Phase Detector Operation                                                                           | 4-109 |

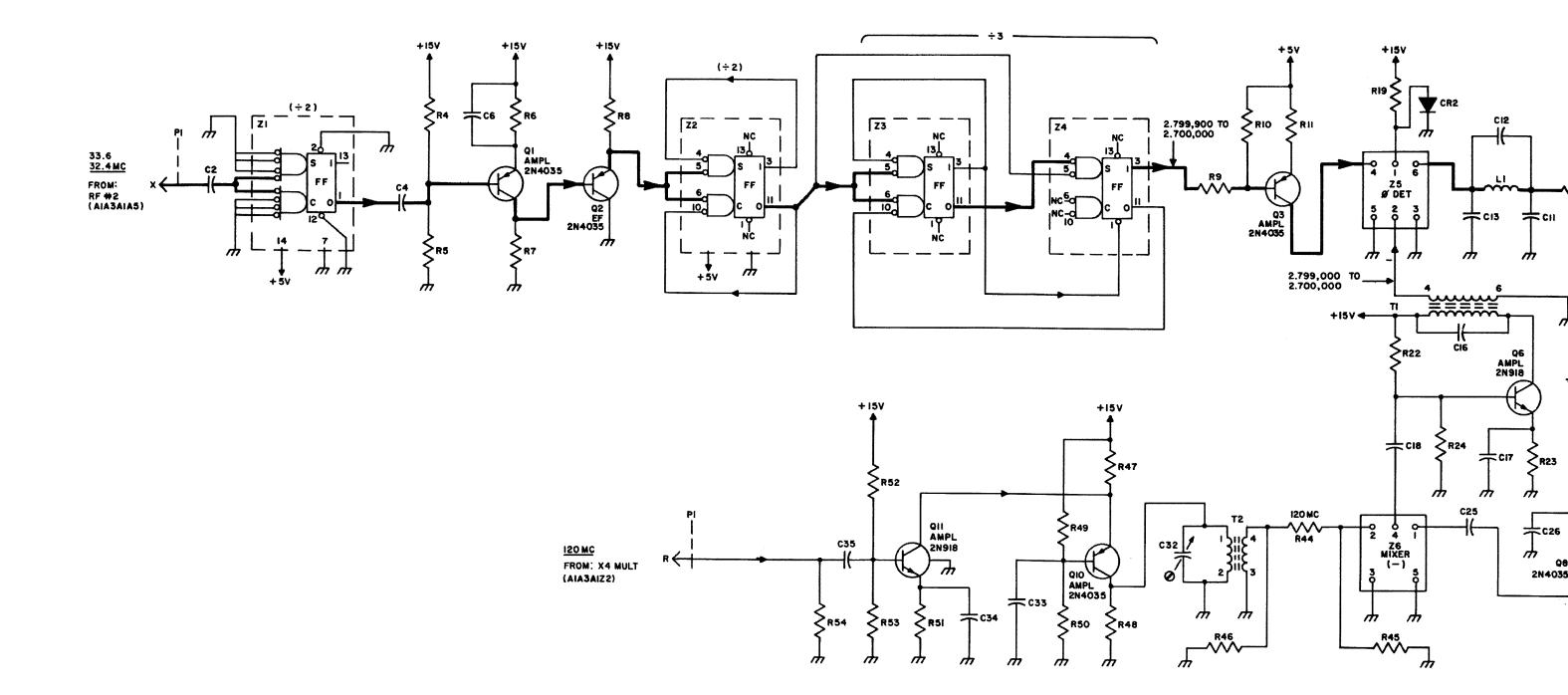

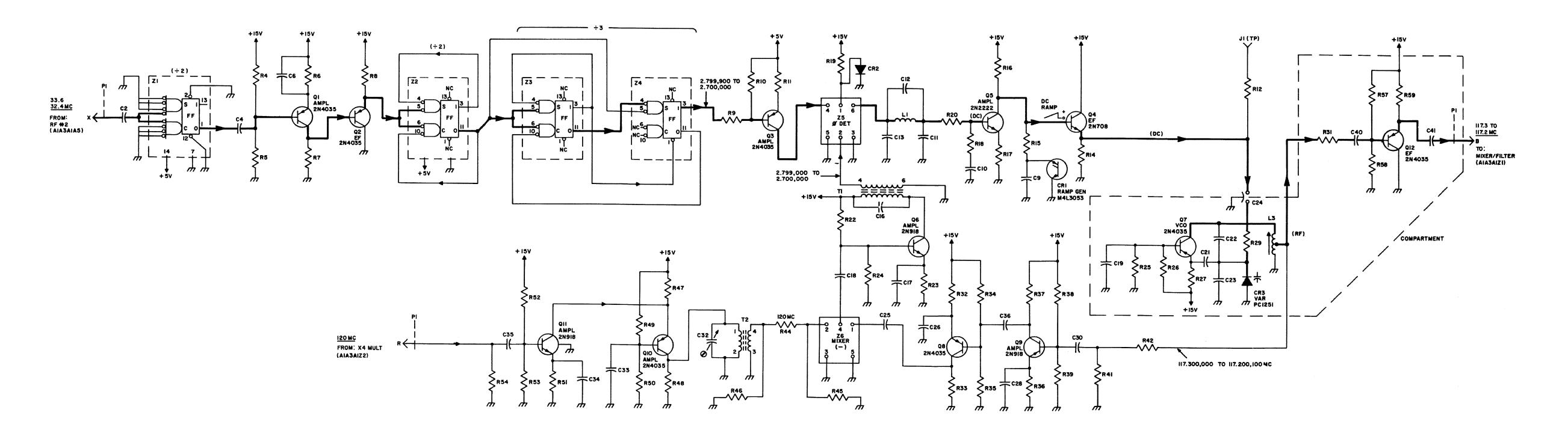

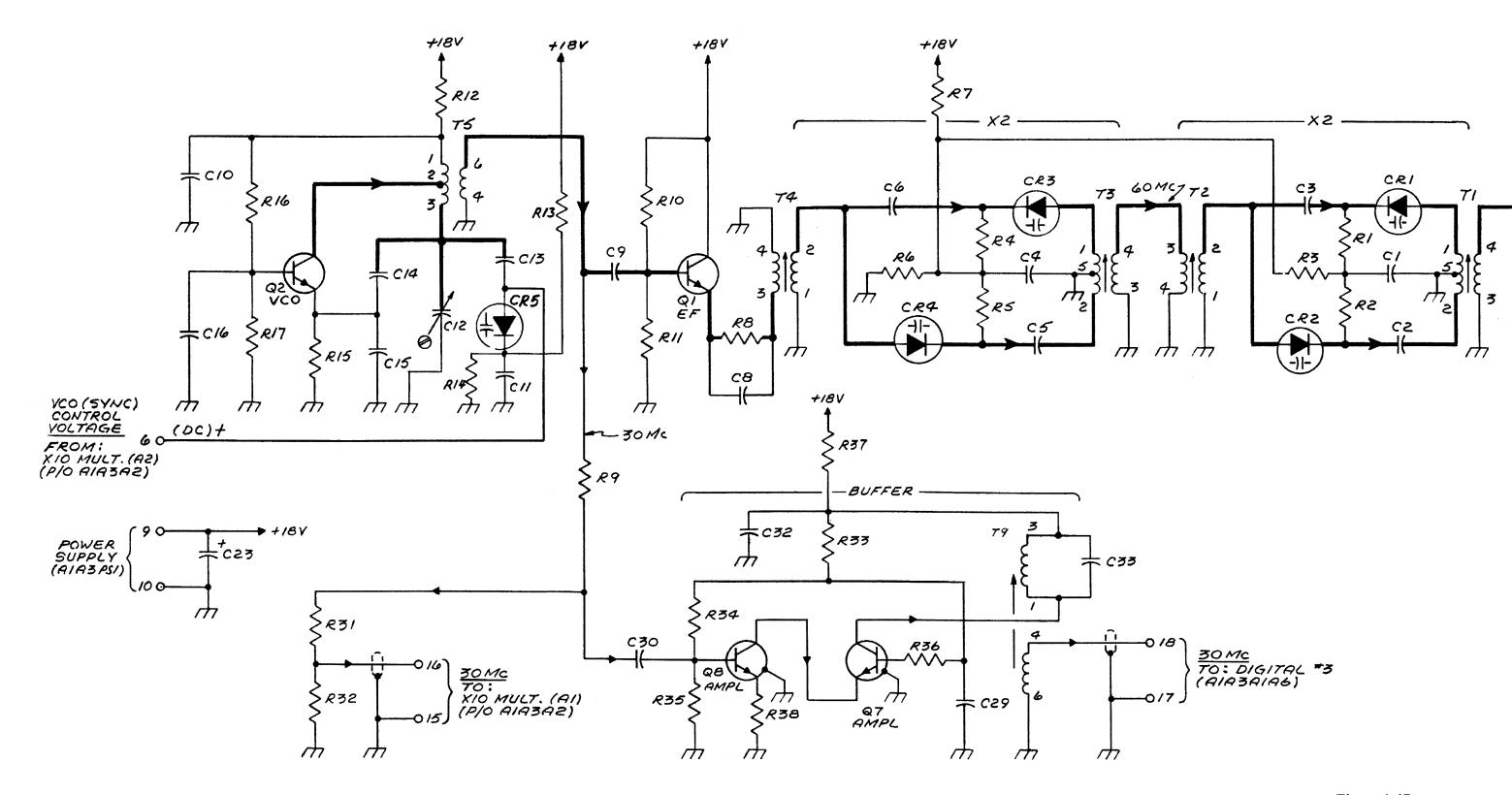

| 4-40   | RF #2 AlA3AlA5, Simplified Schematic Diagram                                                                       | 4-113 |

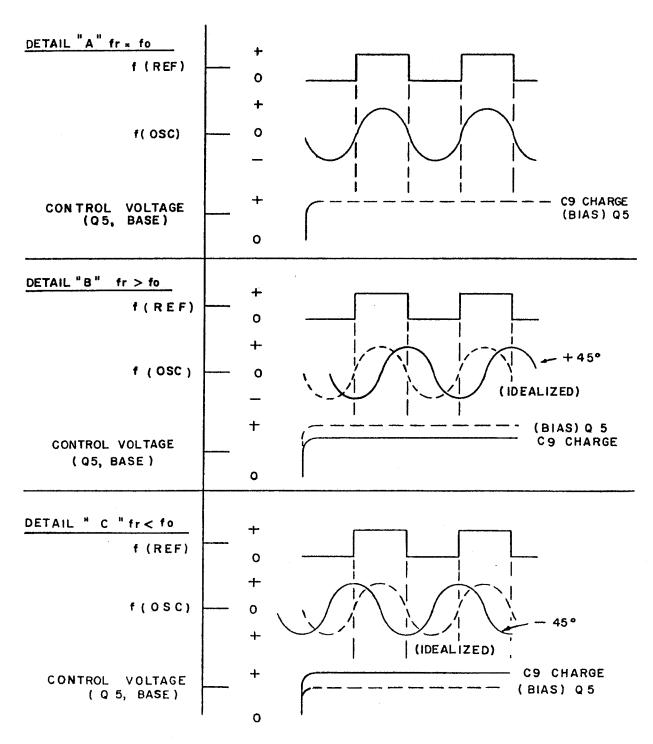

| 4-41   | RF #2 Timing Diagram, Digital Discriminator                                                                        | 4-115 |

viii

| FIGURE | TITLE                                                                                                              | PAGE  |

|--------|--------------------------------------------------------------------------------------------------------------------|-------|

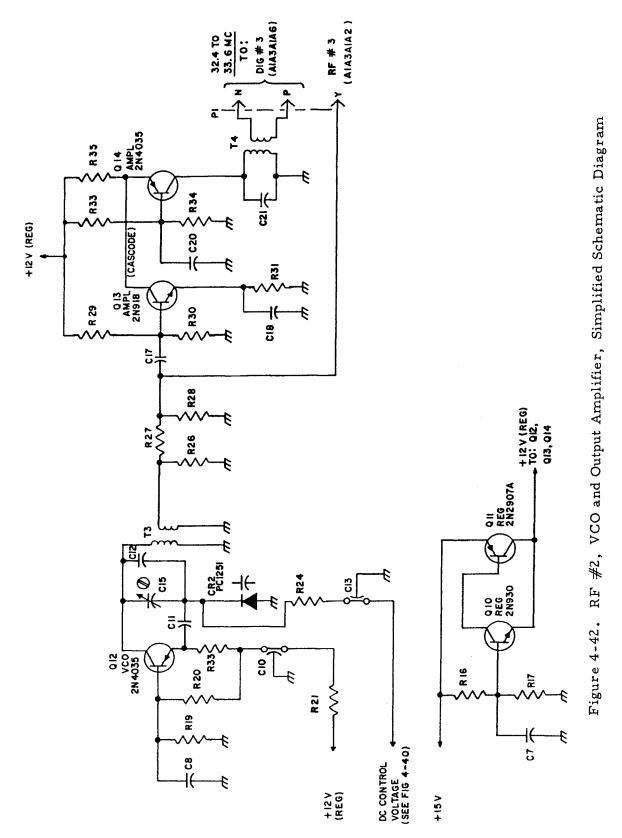

| 4-42   | RF #2, VCO and Output Amplifier, Simplified Schematic Diagram                                                      | 4-116 |

| 4-43   | Digital #3 AlA3AlA6, Simplified Block Diagram                                                                      | 4-119 |

| 4-44   | Digital #3 Divide-by-N Counter, Mechanical Analogy                                                                 | 4-121 |

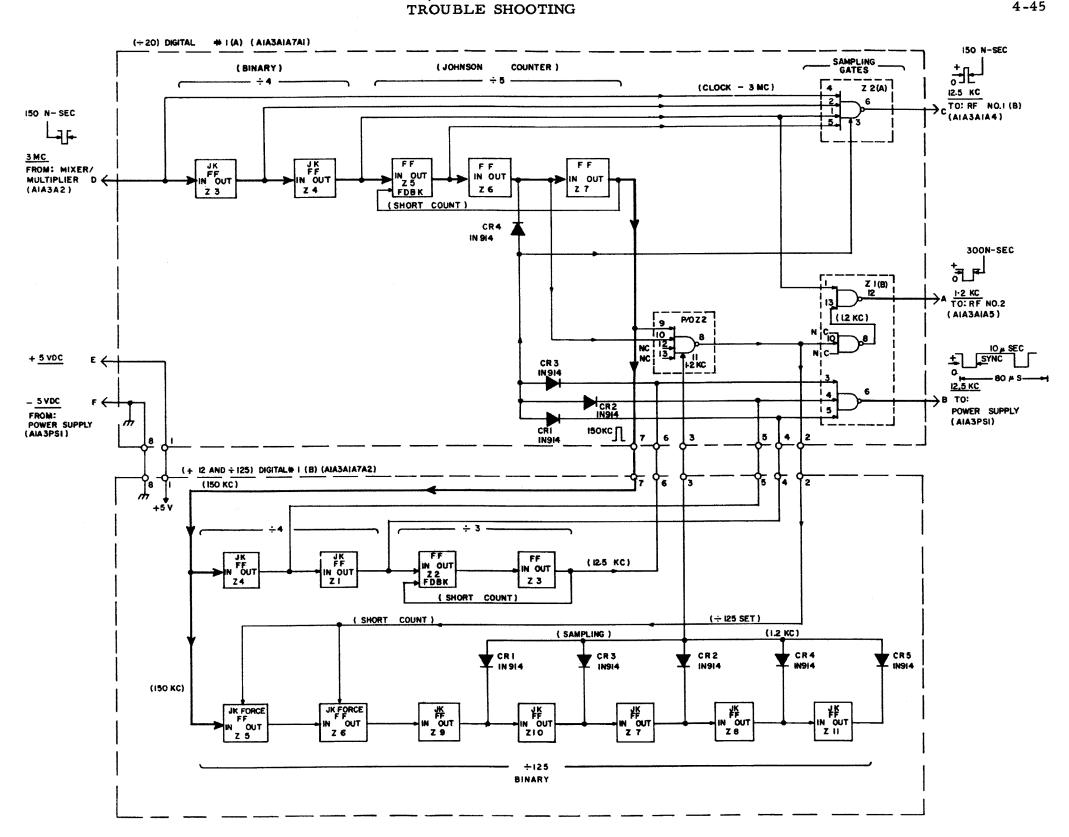

| 4-45   | Digital #1 AlA3AlA7, Simplified Block Diagram                                                                      | 4-125 |

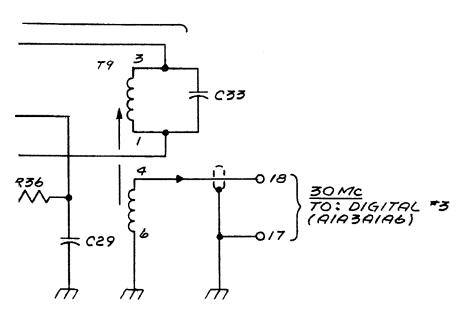

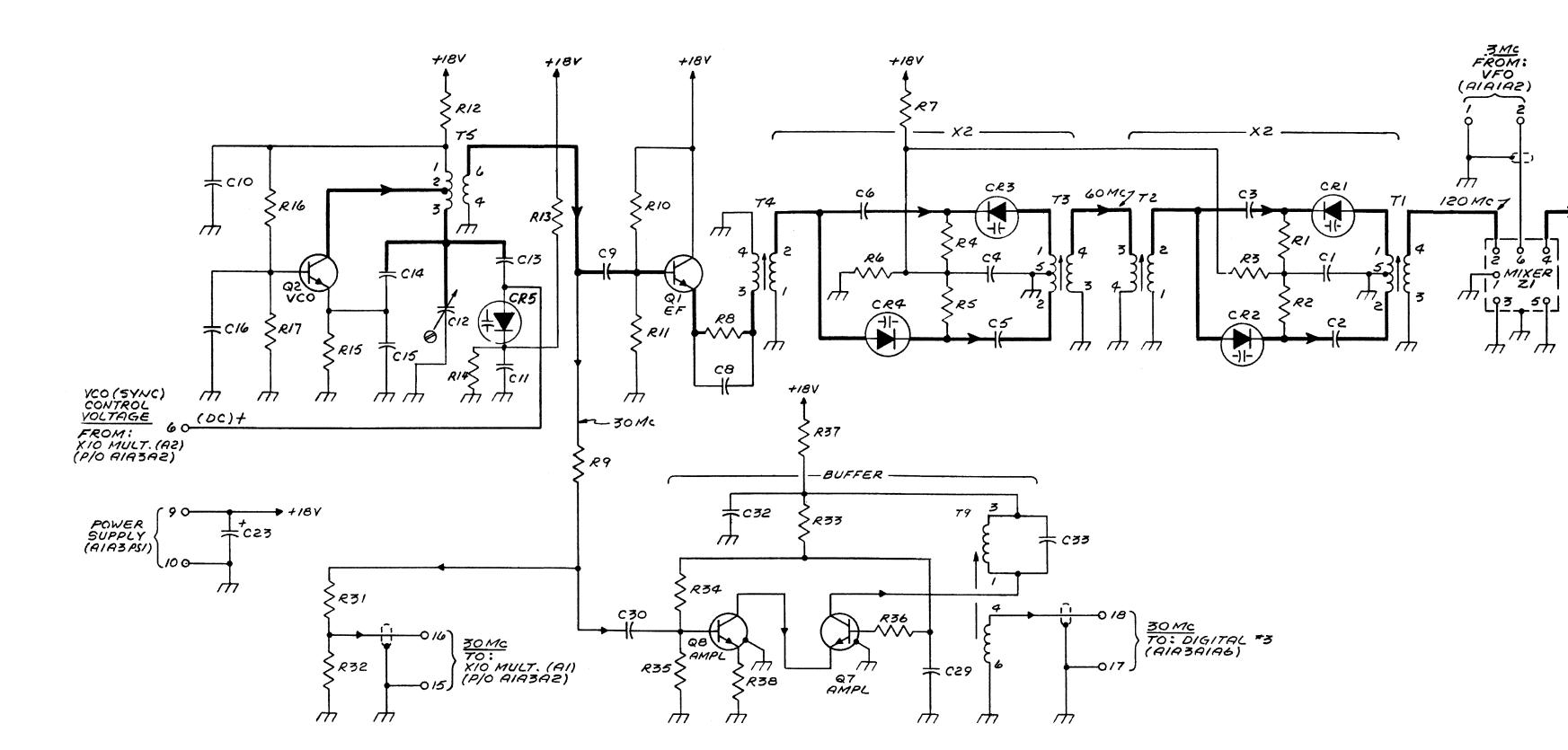

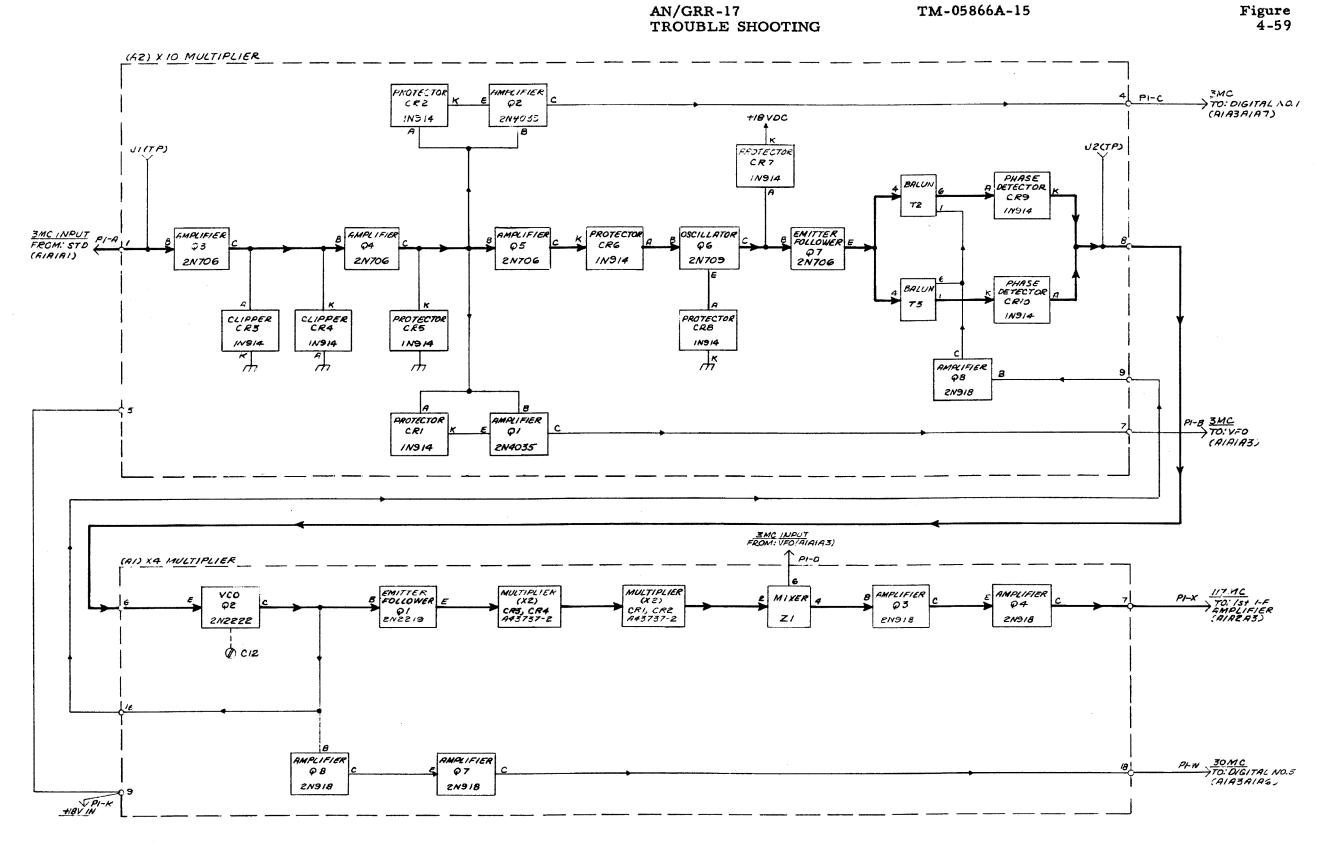

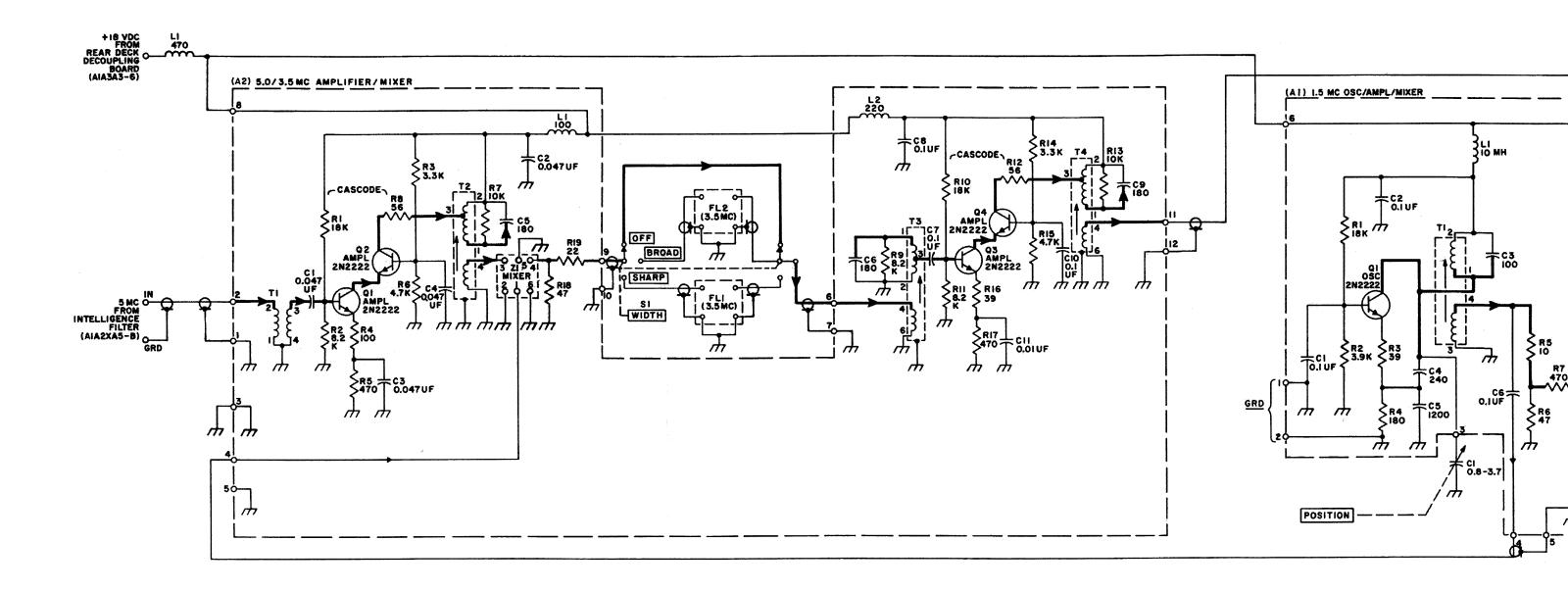

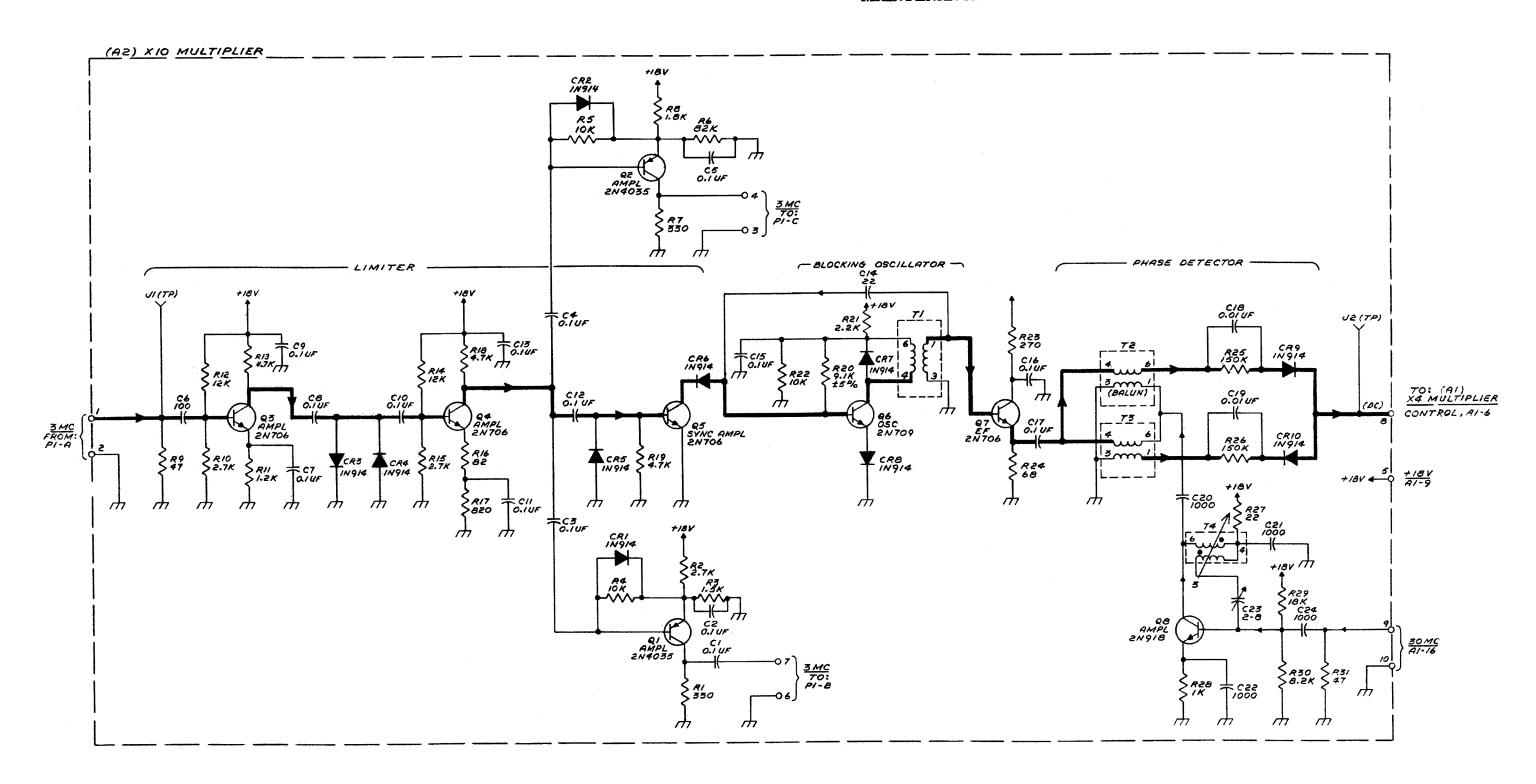

| 4-46   | Mixer/Multiplier A1A3A2, X10 Multiplier (A2); Simplified Schematic Diagram                                         | 4-129 |

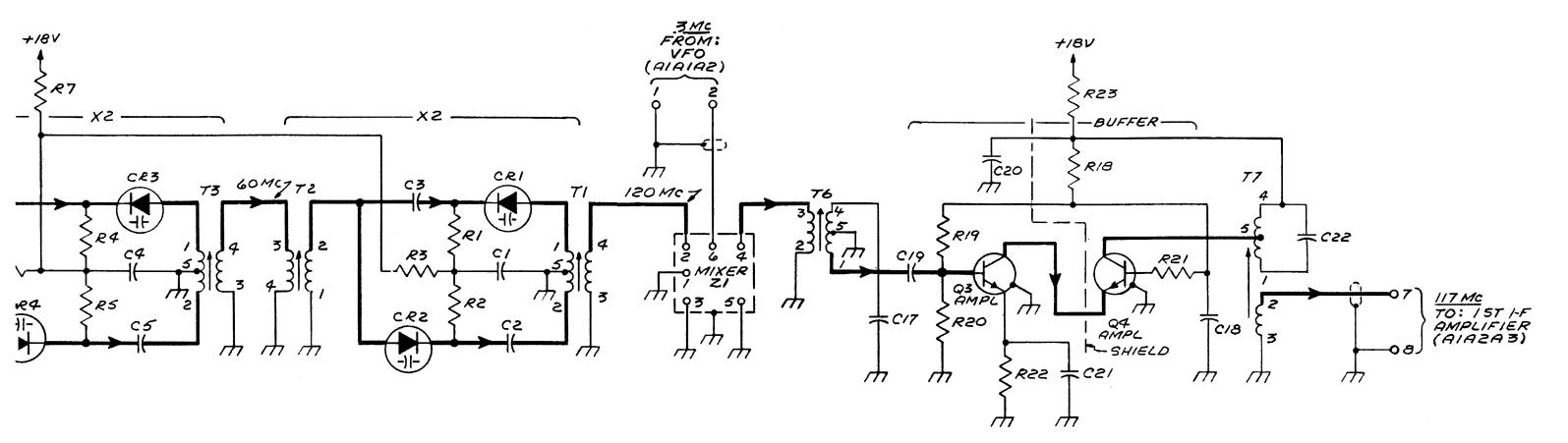

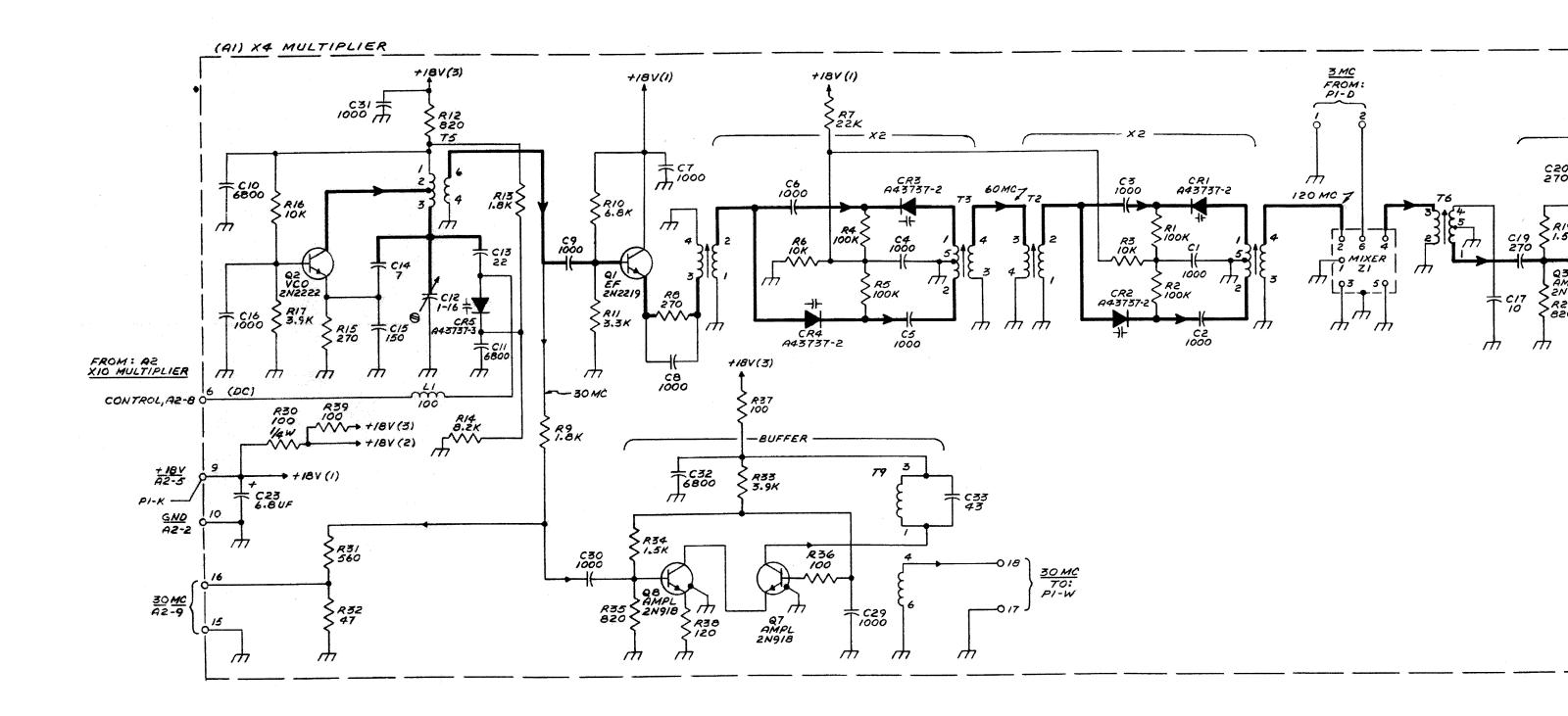

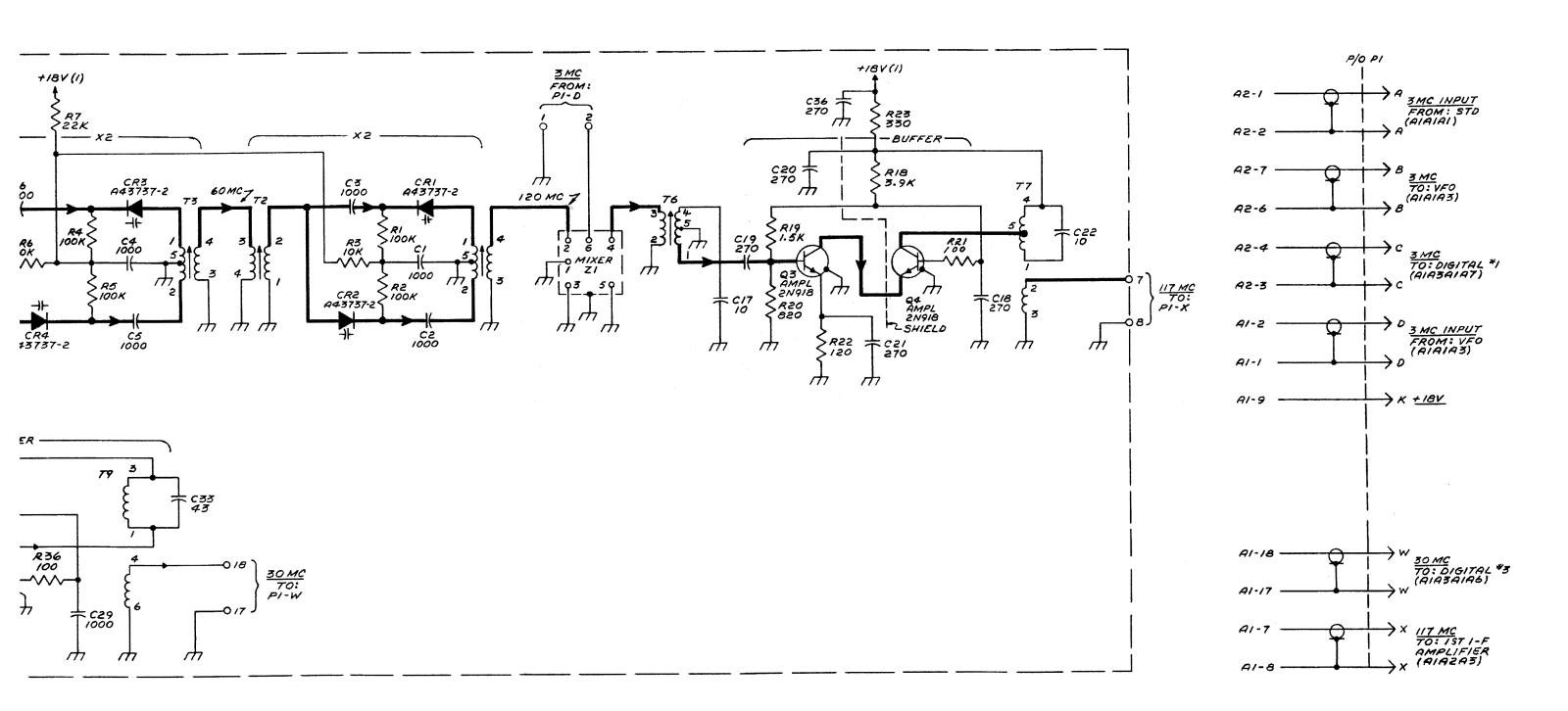

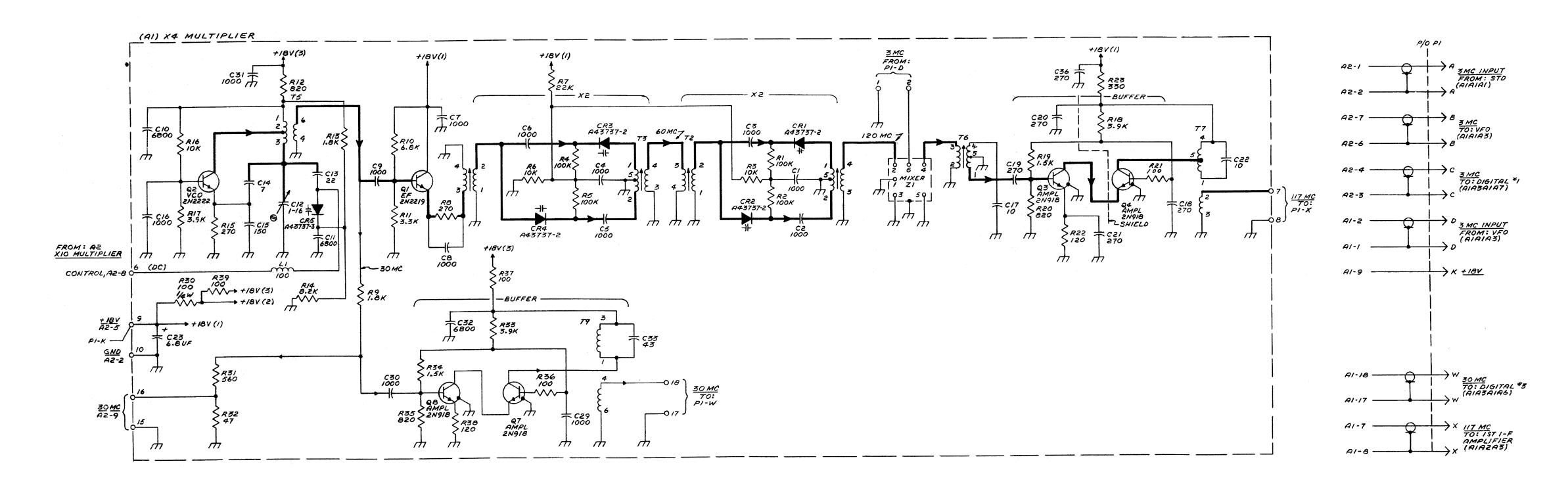

| 4-47   | Mixer/Multiplier A1A3A2, X4 Multiplier (A1); Simplified Schematic Diagram                                          | 4-131 |

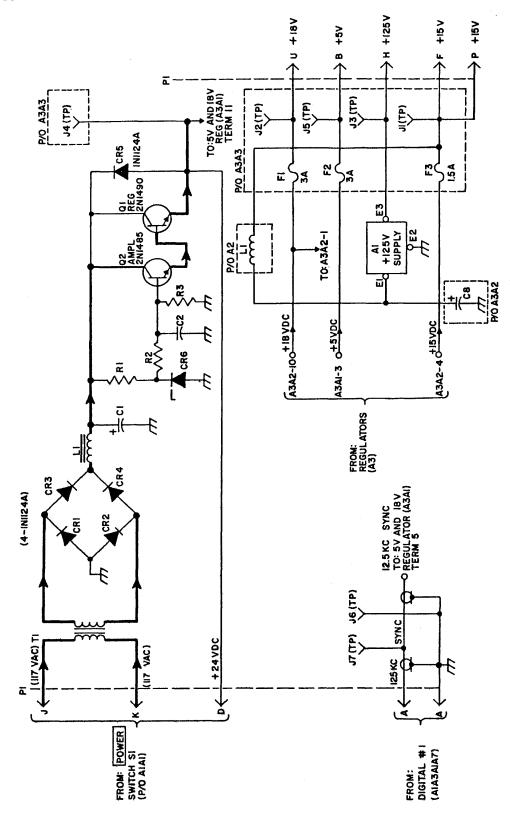

| 4-48   | Power Supply AlA3PS1; Pre-regulator and +125 Volt Supply (A1), Simplified Schematic Diagram                        | 4-136 |

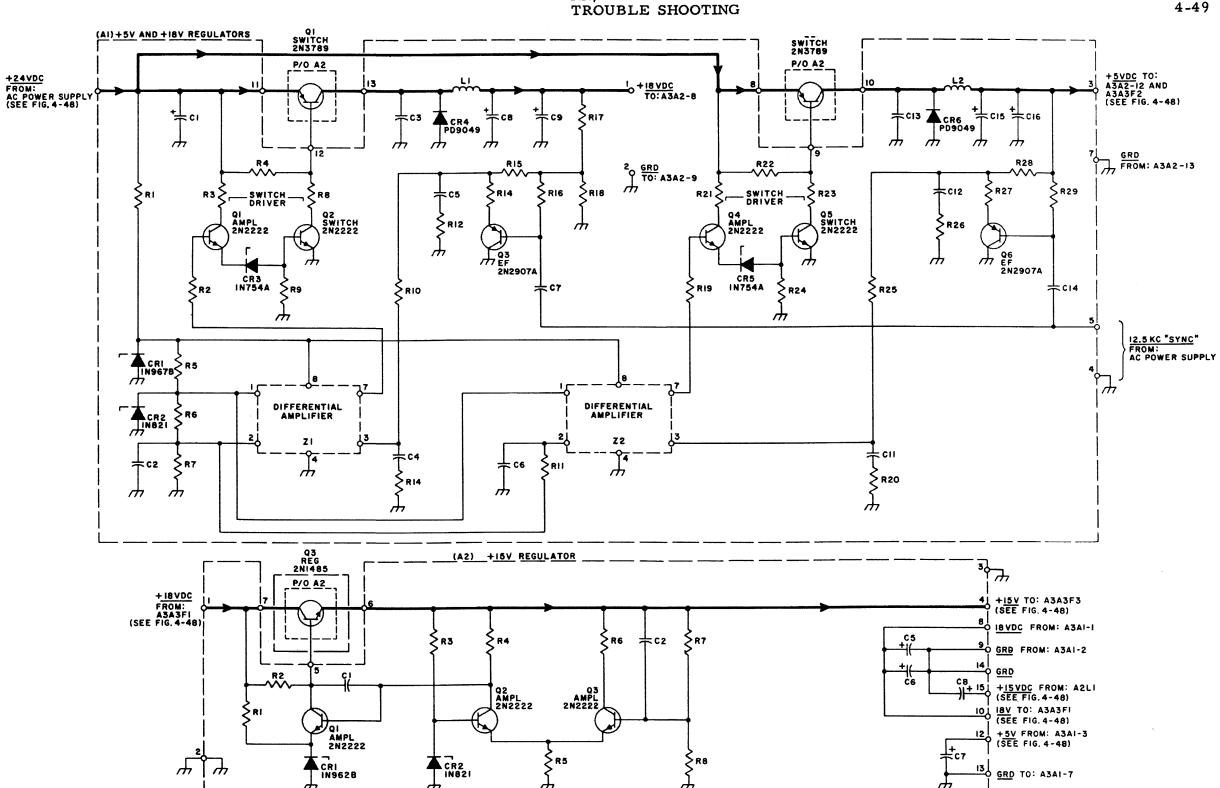

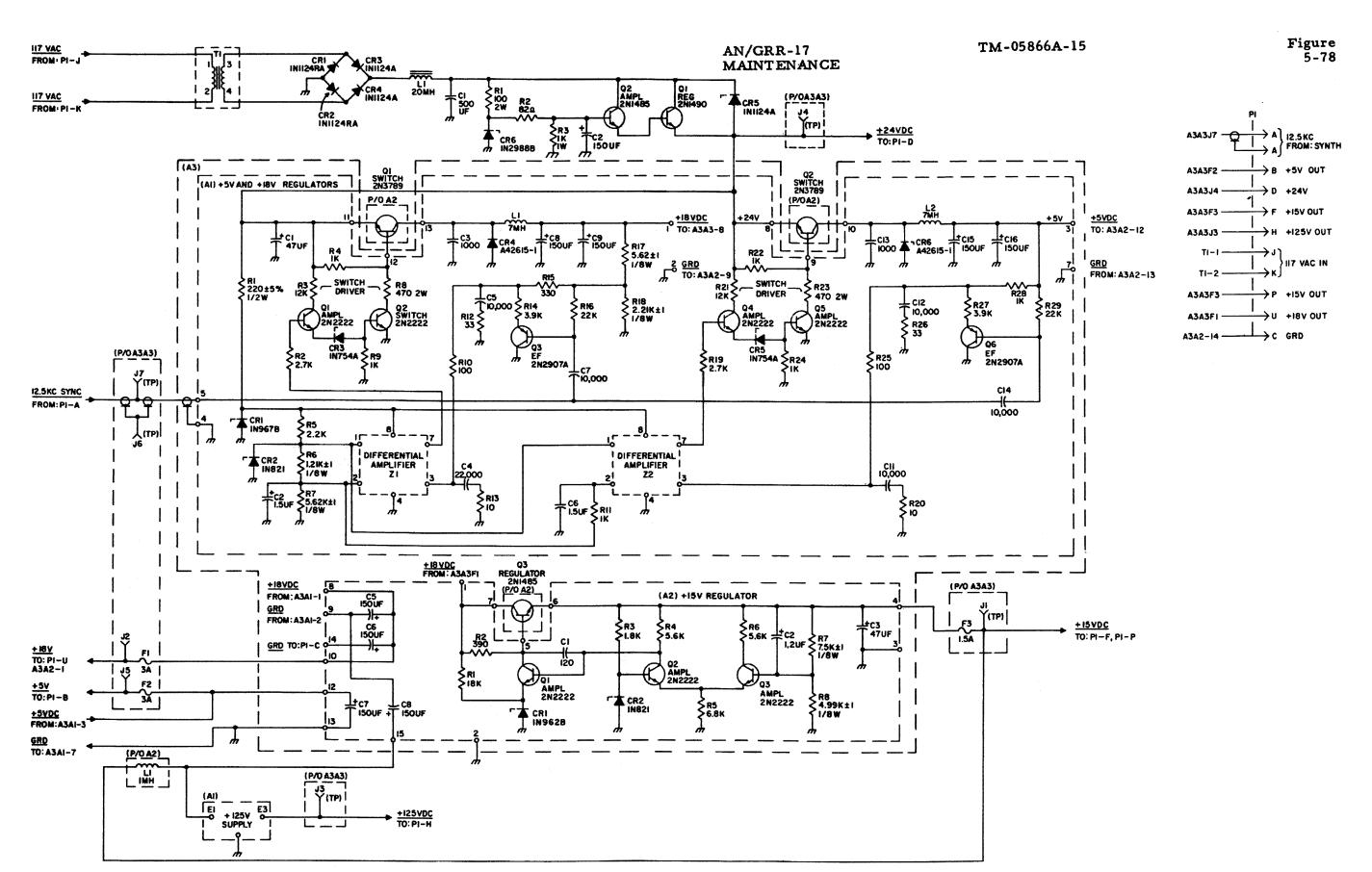

| 4-49   | Power Supply AlA3PS1; +5 Volt, +18 Volt Regulators (A3A1), +15 Volt Regulator (A3A2); Simplified Schematic Diagram | 4-137 |

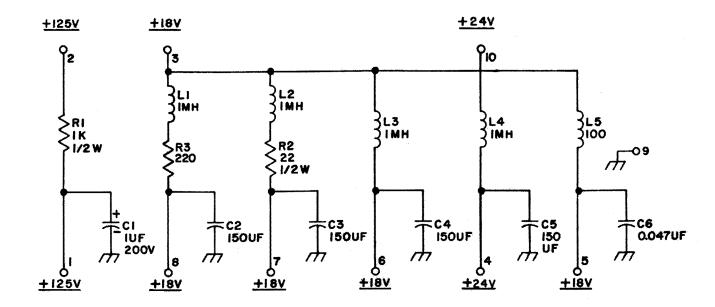

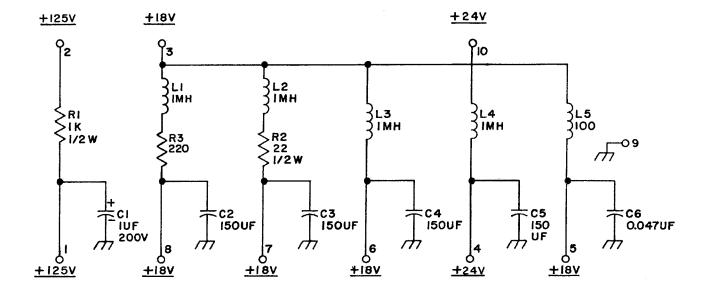

| 4-50   | Power Supply Decoupling Boards AlA2A8 and AlA3A3, Simplified Schematic Diagram                                     | 4-142 |

| 4-51   | Front End A1A2A2, Servicing Block Diagram                                                                          | 4-147 |

| 4-52   | First I-F Amplifier AlA2A3, Servicing Block Diagram                                                                | 4-149 |

| 4-53   | Noise Blanker A1A2A4, Servicing Block Diagram                                                                      | 4-151 |

| 4-54   | Notch Filter AlAlA4, Servicing Block Diagram                                                                       | 4-153 |

| 4-55   | Second I-F/AGC Amplifier AlA2A6, Servicing Block Diagram (Sheet 1 of 2)                                            | 4-155 |

| 4-55   | Second I-F/AGC Amplifier AlA2A6, Servicing Block Diagram (Sheet 2 of 2)                                            | 4-157 |

| 4-56   | Detector/AF Amplifier AlA2A7, Servicing Block Diagram (Sheet 1 of 2)                                               | 4-159 |

| 4-56   | Detector/AF Amplifier AlA2A7, Servicing Block Diagram (Sheet 2 of 2)                                               | 4-161 |

| 4-57   | BFO AlAlA2, Servicing Block Diagram                                                                                | 4-163 |

| 4-58   | Synthesizer AlA3Al, Servicing Block Diagram                                                                        | 4-165 |

| 4-59   | Mixer/Multiplier AlA3A2, Servicing Block Diagram                                                                   | 4-167 |

| 4-60   | Power Supply AlA3PSI, Servicing Block Diagram                                                                      | 4-169 |

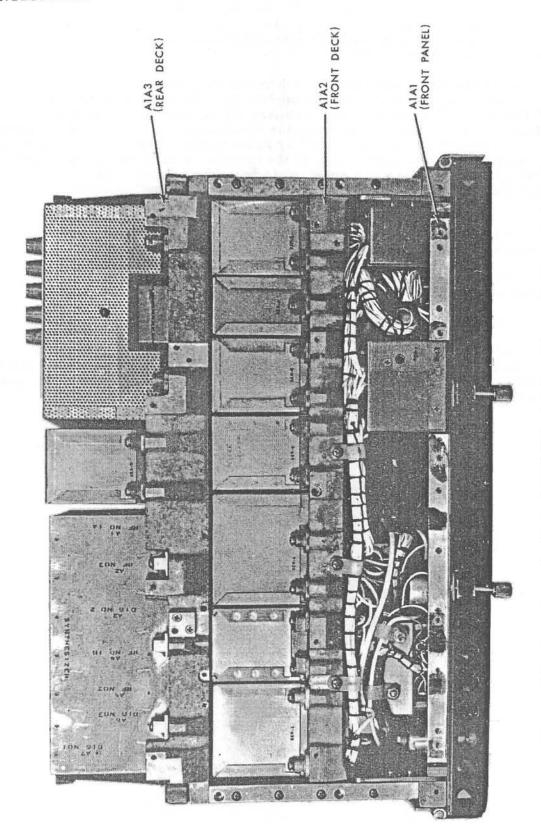

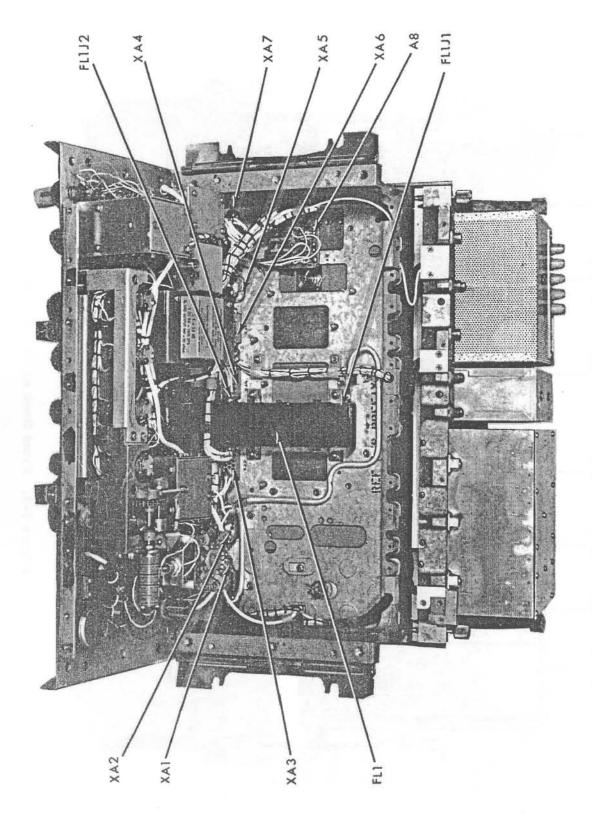

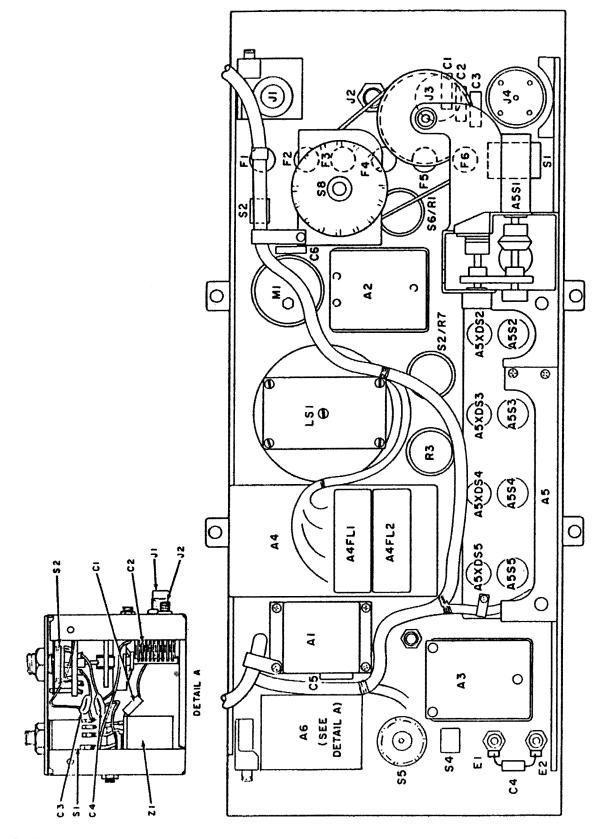

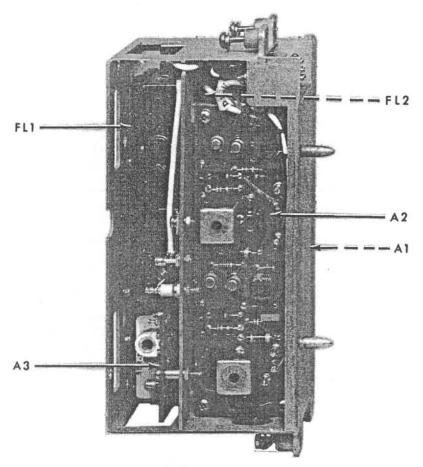

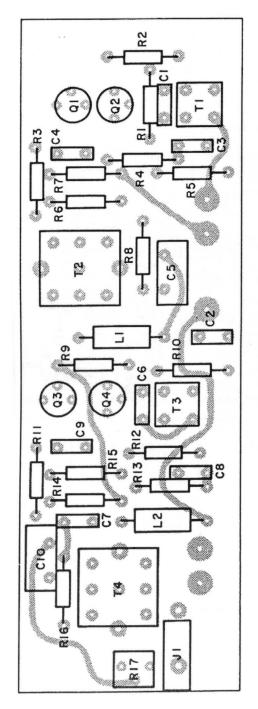

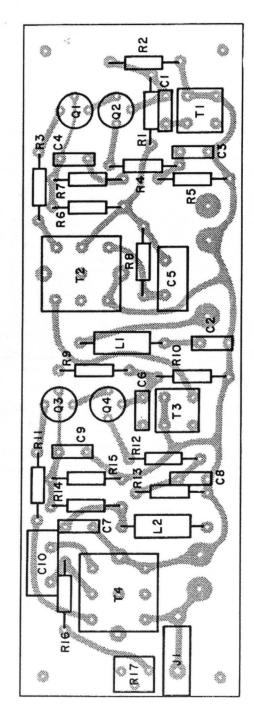

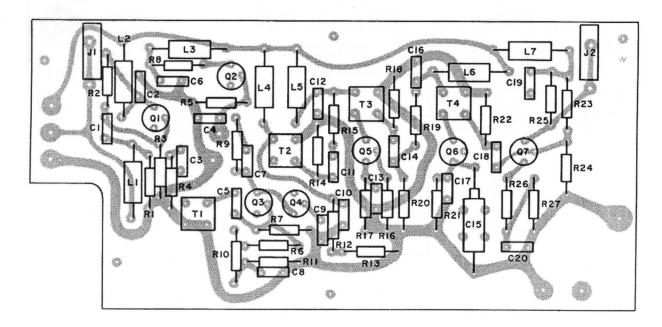

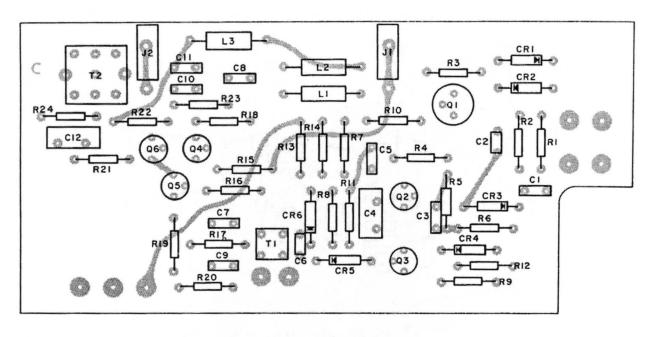

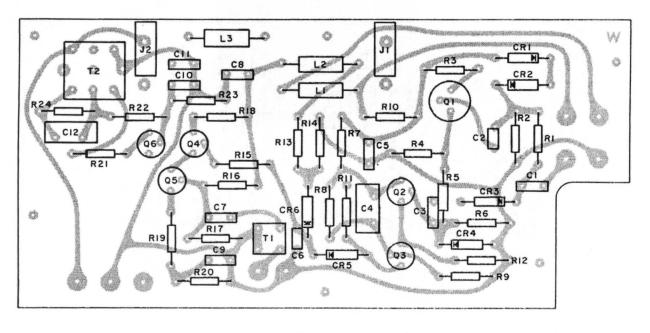

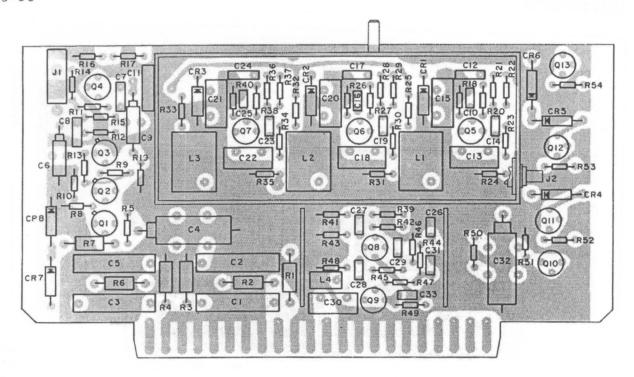

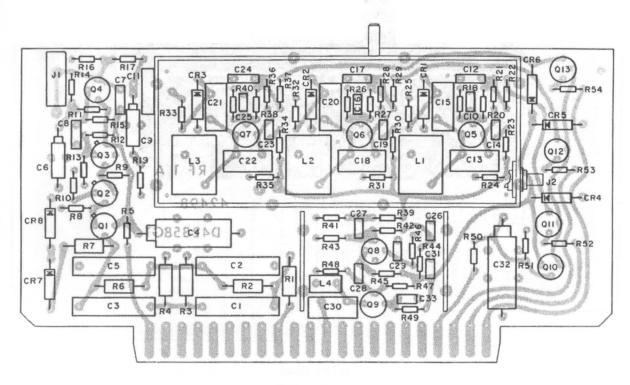

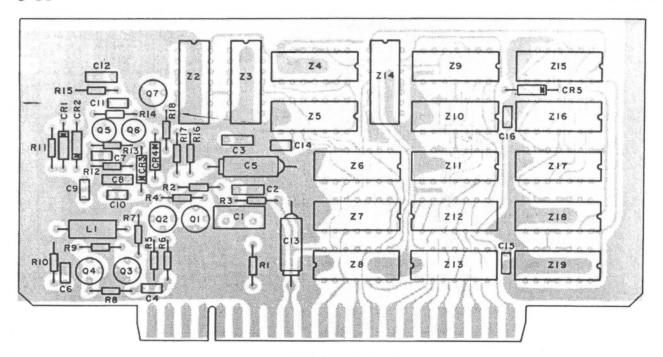

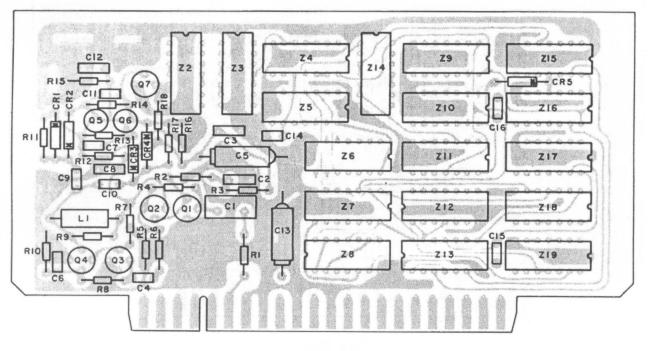

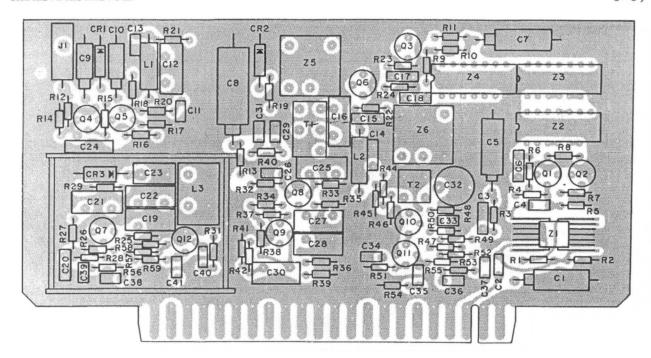

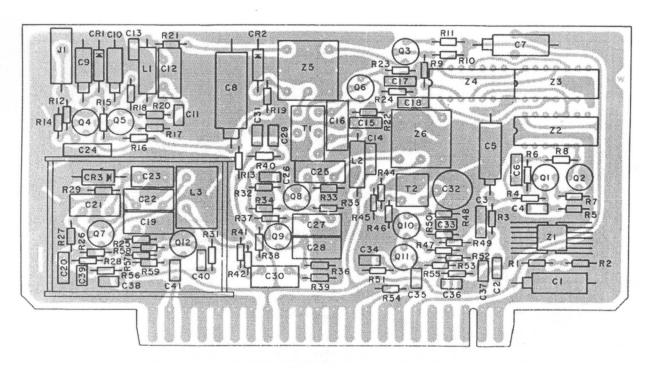

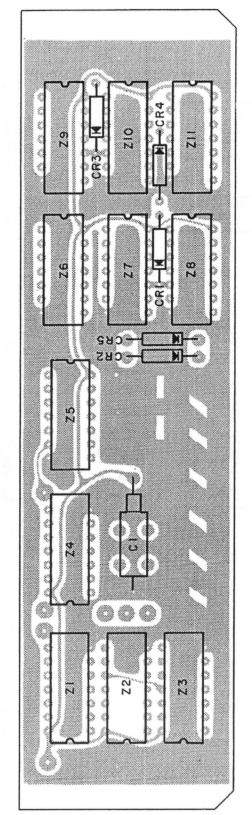

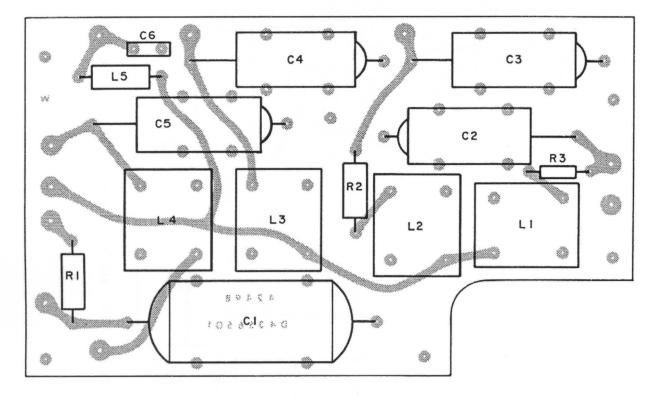

| 5-1    | Receiver, Radio R-1490/GRR-17, Top View with Transit Case Removed                                                  | 5-39  |

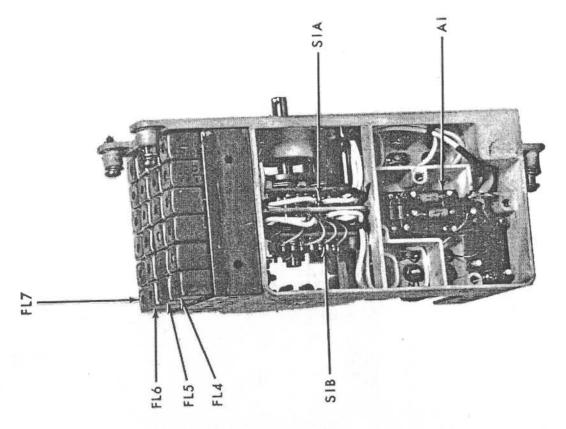

| 5-2    | Front Panel AlAl, Front View                                                                                       | 5-40  |

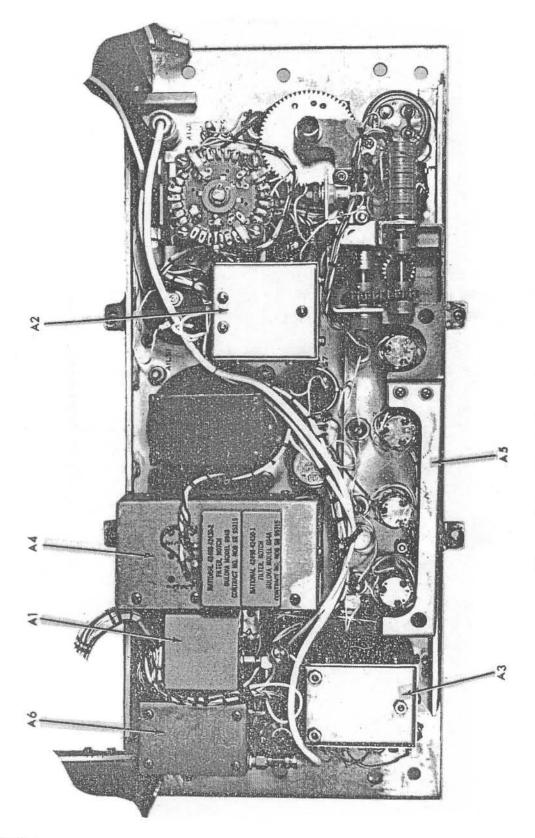

| 5-3    | Front Panel AlAl, Rear View                                                                                        | 5-41  |

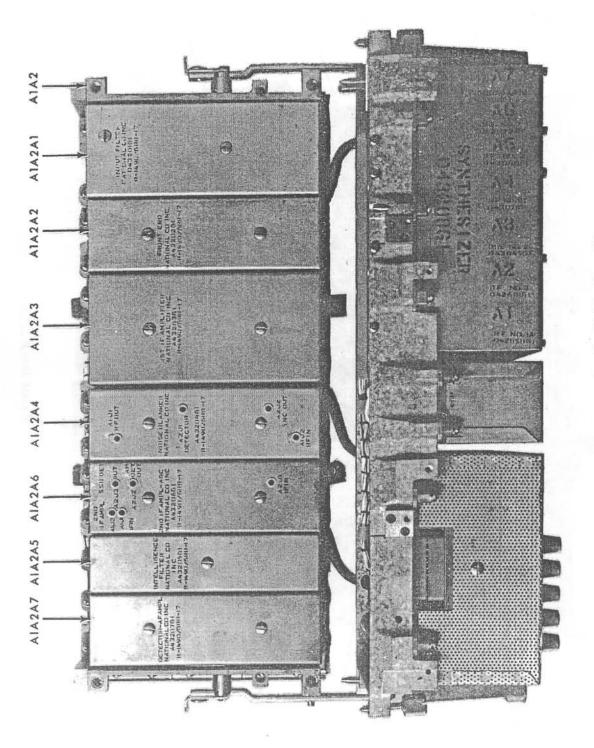

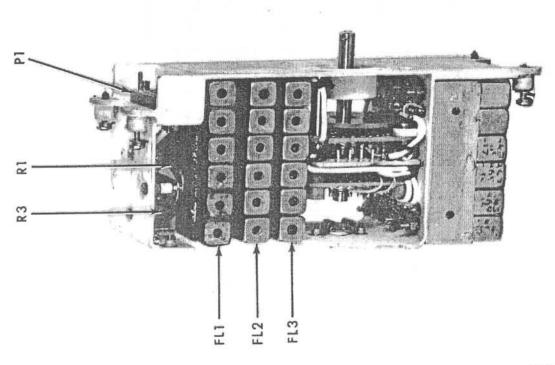

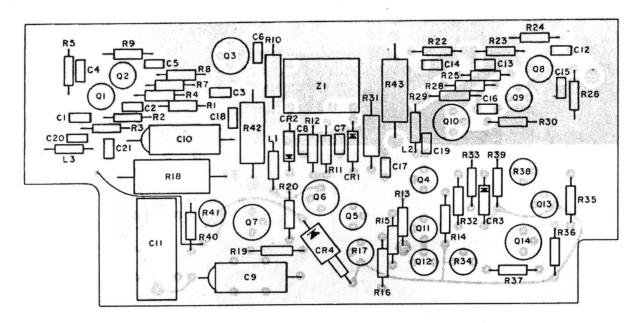

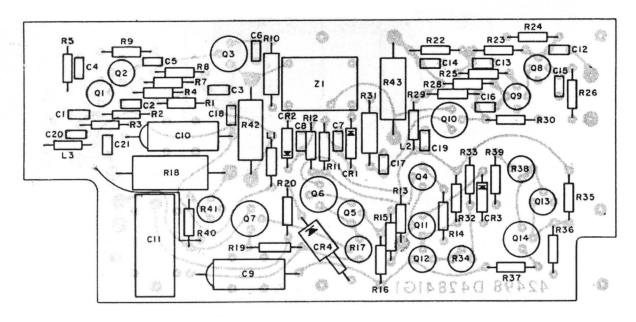

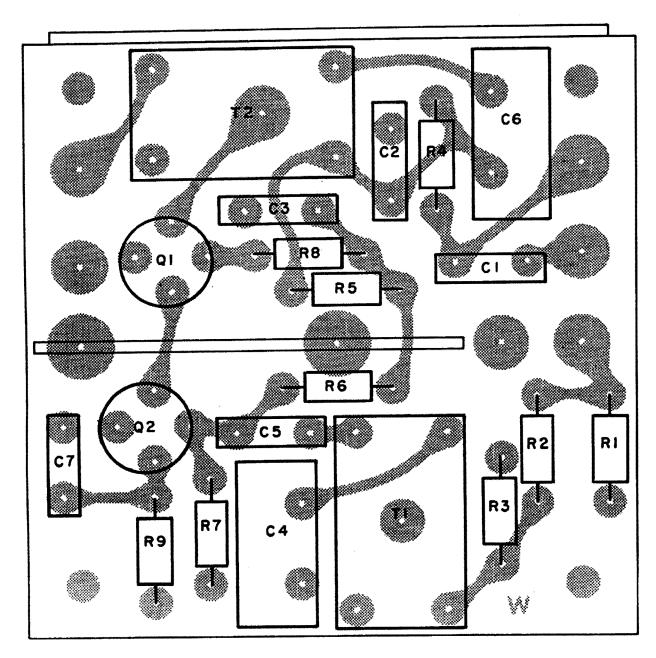

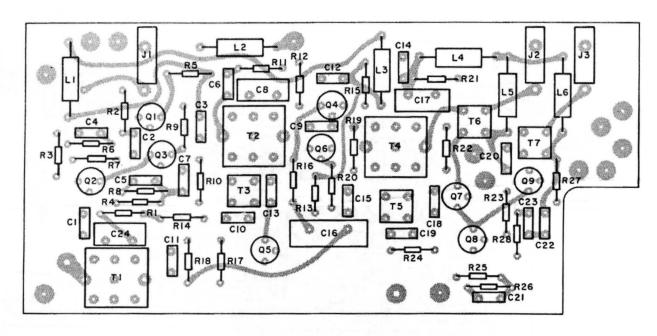

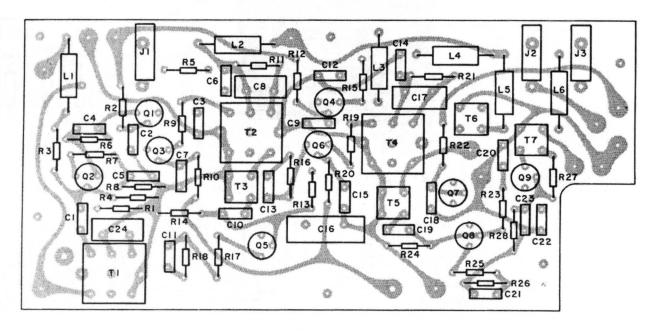

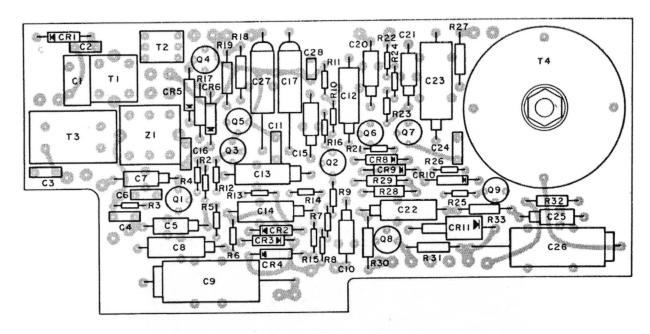

| 5-4    | Front Deck A1A2, Bottom View                                                                                       | 5-42  |

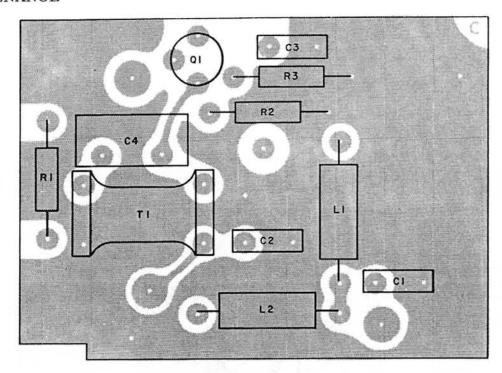

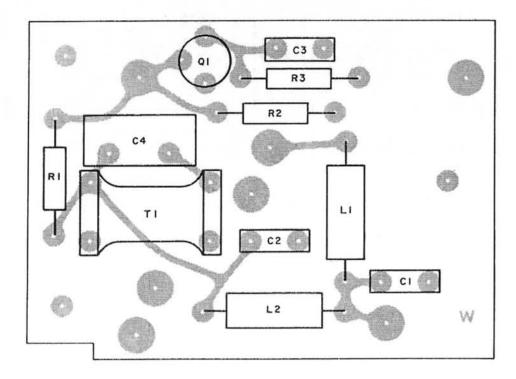

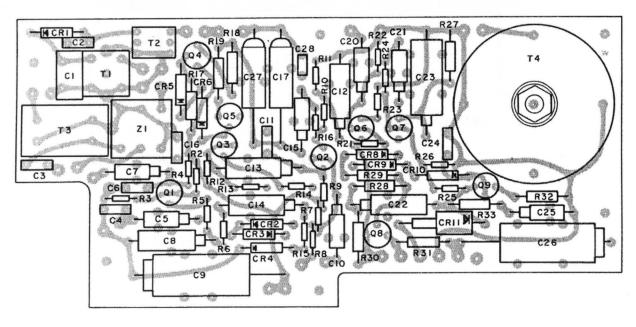

| 5-5    | Front Deck AlA2, Top View                                                                                          | 5-43  |

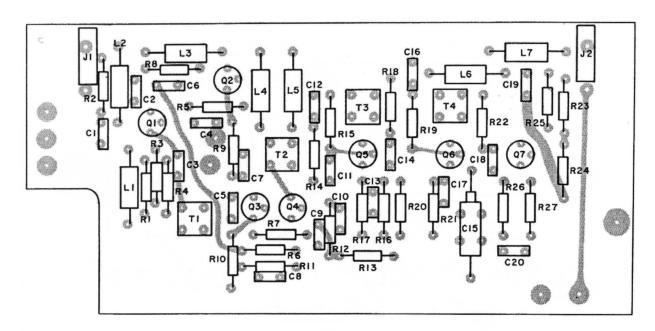

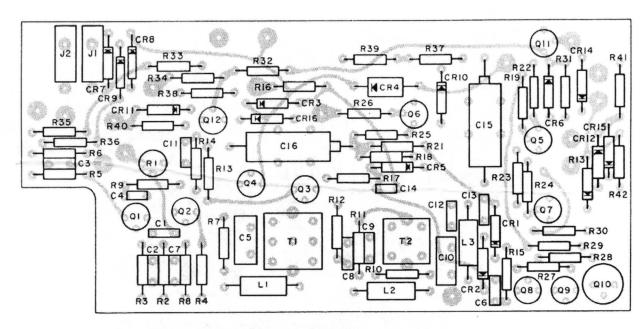

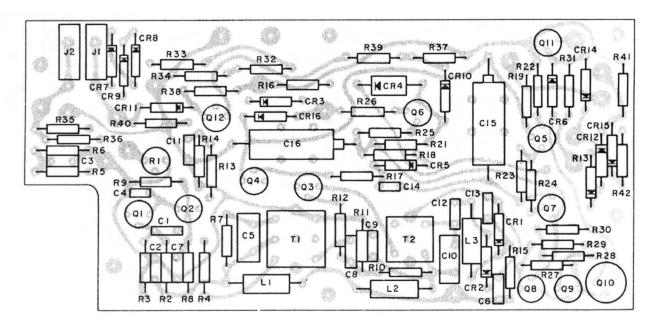

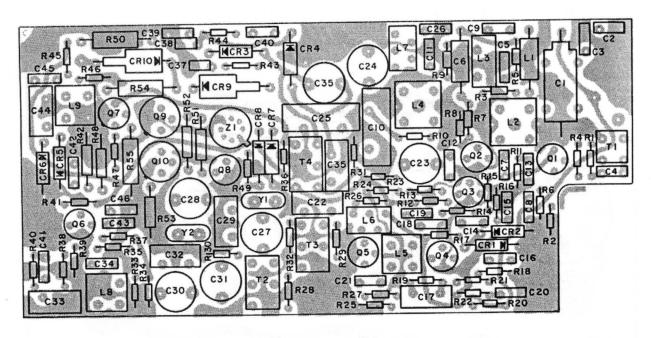

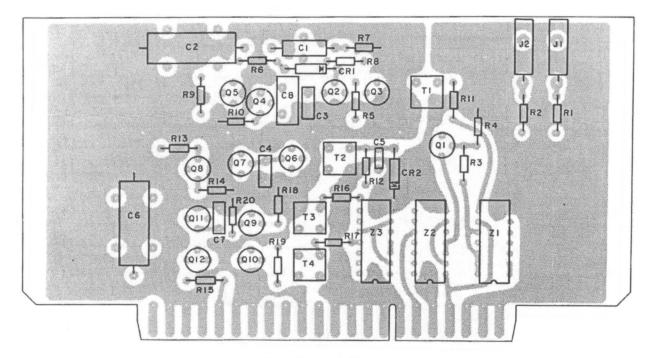

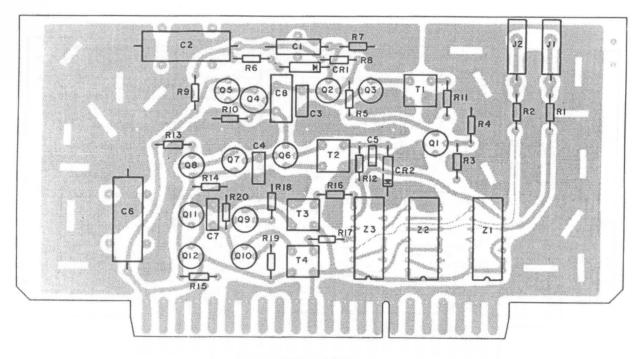

| 5-6    | Rear Deck AlA3, Bottom View                                                                                        | 5-44  |

| 5-7    | Rear Deck AlA3, Top View                                                                                           | 5-45  |

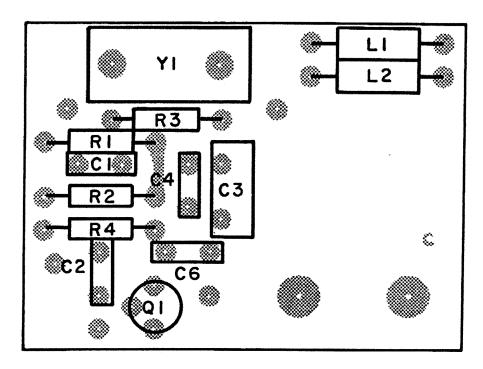

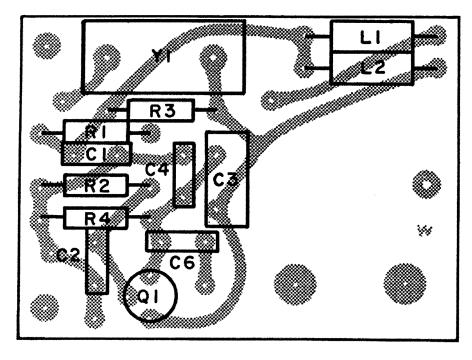

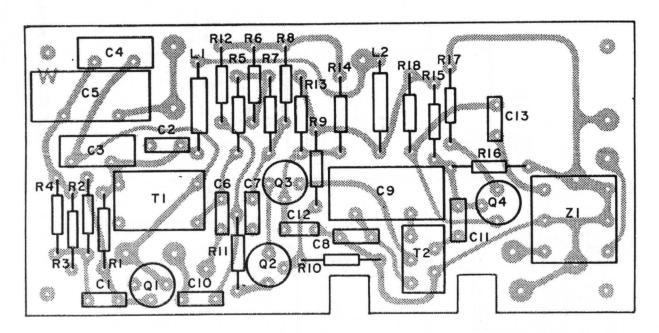

| 5-8    | VFO AlAlA3, Parts Location                                                                                         | 5-46  |

| 5-9    | VFO AlAlA3, Oscillator Al, Parts Location                                                                          | 5-47  |

| 5-10   | VFO AlAlA3, Tuning A2, Parts Location                                                                              | 5-48  |

| 5-11   | BFO AlAlA2, Parts Location                                                                                         | 5-49  |

ORIGINAL

| FIGURE | TITLE                                                                     | PAGE |

|--------|---------------------------------------------------------------------------|------|

| 5-12   | BFO AlAlA2, Oscillator A2, Parts Location                                 | 5~50 |

| 5-13   | BFO AlAlA2, Amplifier Al, Parts Location                                  | 5-51 |

| 5-14   | Notch Filter AlAlA4, Parts Location                                       | 5-52 |

| 5-15   | Notch Filter AlAlA4, Amplifier-Mixer A2, Parts Location                   | 5~53 |

| 5-16   | Notch Filter AlAlA4, Oscillator-Mixer Al, Parts Location                  | 5-54 |

| 5-17   | MEGACYCLES Frequency Selector AlAlA5, Parts Location                      | 5-55 |

| 5-18   | Input Filter AlA2Al, Parts Location                                       | 5-56 |

| 5-19   | Front End AlA2A2, Parts Location                                          | 5-57 |

| 5-20   | VHF Oscillator Phase-Locked Loop AlA2A2A1, Parts Location                 | 5-58 |

| 5-21   | First I-F Amplifier AlA2A3, Parts Location                                | 5-59 |

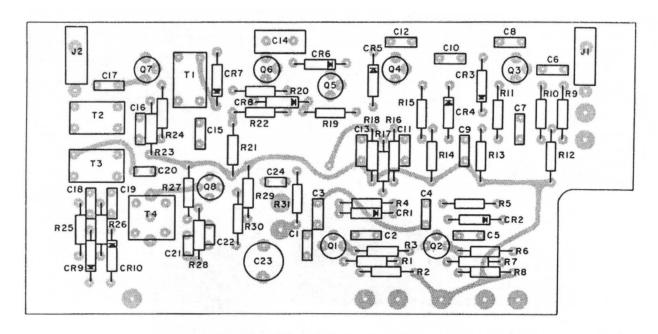

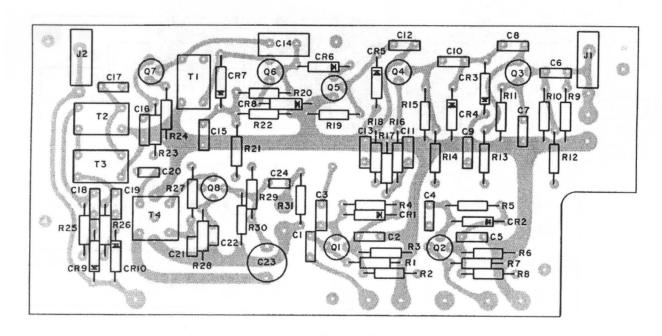

| 5-22   | First I-F Amplifier AlA2A3, 112 MC I-F Amplifier Al, Parts Location       | 5-60 |

| 5-23   | First I-F Amplifier AlA2A3, Reserve Gain Amplifier A2, Parts Location     | 5-61 |

| 5-24   | First I-F Amplifier A1A2A3, 117 MC Buffer Amplifier A3, Parts Location    | 5-62 |

| 5-25   | Noise Blanker AlA2A4, 5 MC Amplifier Al, Parts Location                   | 5-63 |

| 5-26   | Noise Blanker AlA2A4, Detector/Gated Amplifier A2, Parts Location         | 5-64 |

| 5-27   | Intelligence Filter A1A2A5, Parts Location                                | 5-65 |

| 5-28   | Second I-F Amplifier A1A2A6A1, Parts Location                             | 5-66 |

| 5-29   | AGC Amplifier AlA2A6A2, Parts Location                                    | 5-67 |

| 5-30   | Detector/AF Amplifier AlA2A7, Parts Location                              | 5-68 |

| 5-31   | Detector/AF Amplifier A1A2A7, Detector/Audio Amplifier A1, Parts Location | 5-69 |

| 5-32   | Detector/AF Amplifier AlA2A7, FSK Converter A2, Parts Location            | 5-70 |

| 5-33   | Front-Deck Supply Decoupling Board A1A2A8, Parts Location                 | 5-71 |

| 5-34   | Synthesizer AlA3Al, Decoupling Components Location                        | 5-72 |

| 5-35   | Synthesizer AlA3Al, Module Location                                       | 5-73 |

| 5-36   | RF #1(A) AlA3AlAl, Parts Location                                         | 5-74 |

| 5-37   | RF #1(B) A1A3A1A4, Parts Location                                         | 5-75 |

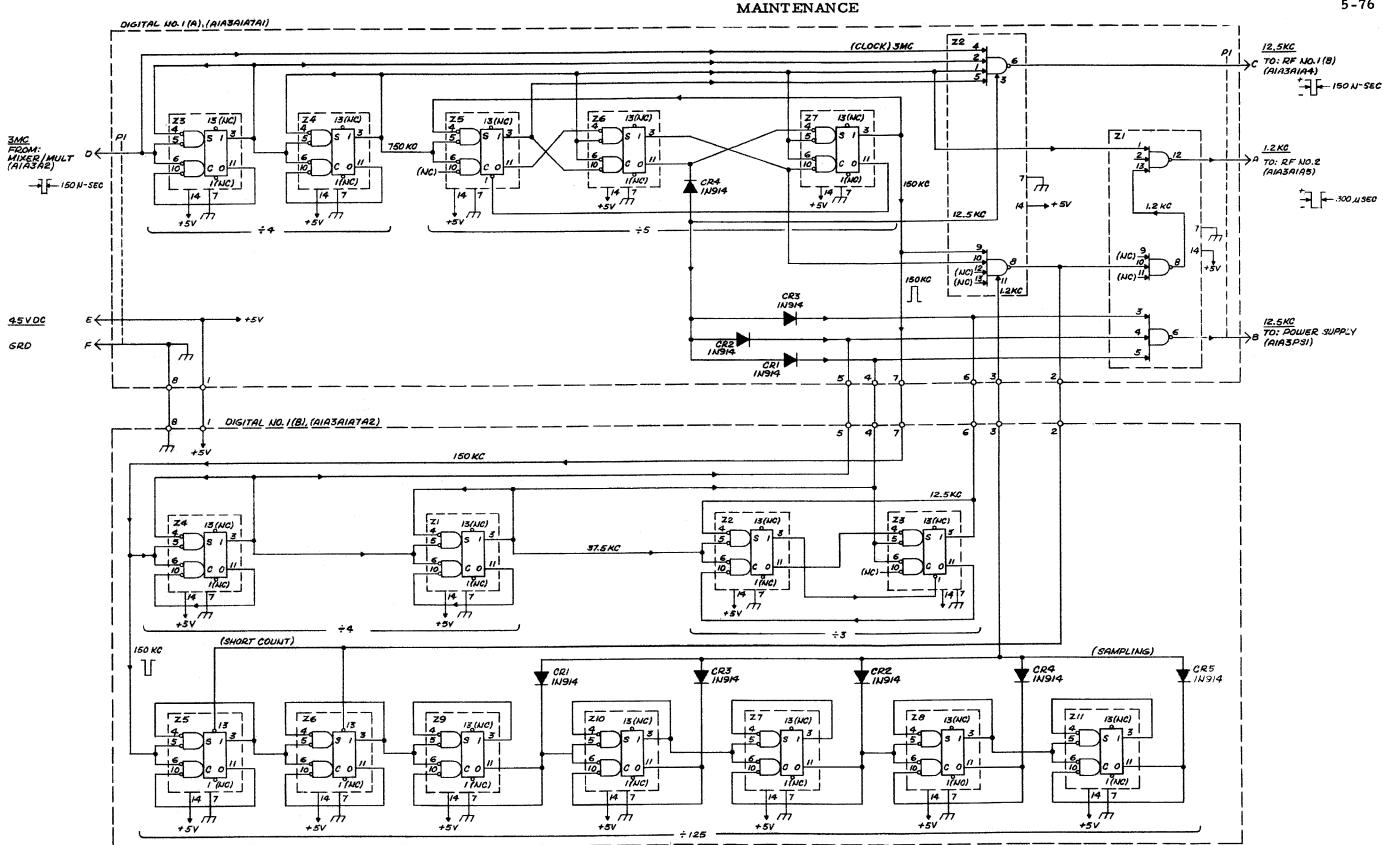

| 5-38   | Digital #2 AlA3AlA3, Parts Location                                       | 5-76 |

| 5-39   | RF #3 AlA3AlA2, Parts Location                                            | 5-77 |

| 5-40   | RF #2 AlA3AlA5, Parts Location                                            | 5-78 |

| 5-41   | Digital #3 AlA3AlA6, Parts Location                                       | 5-79 |

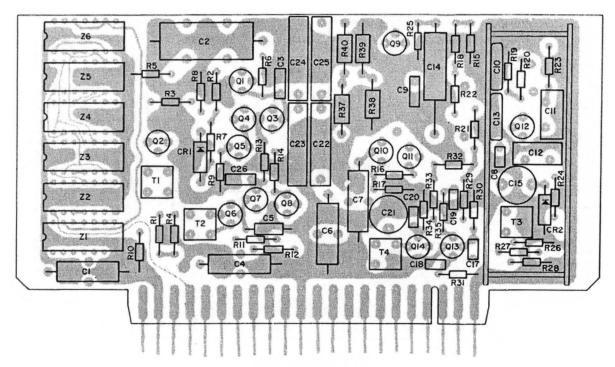

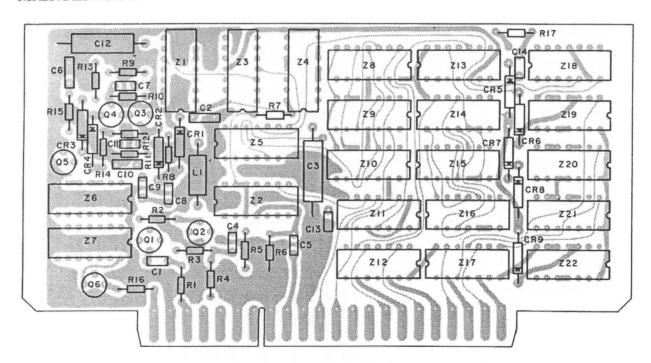

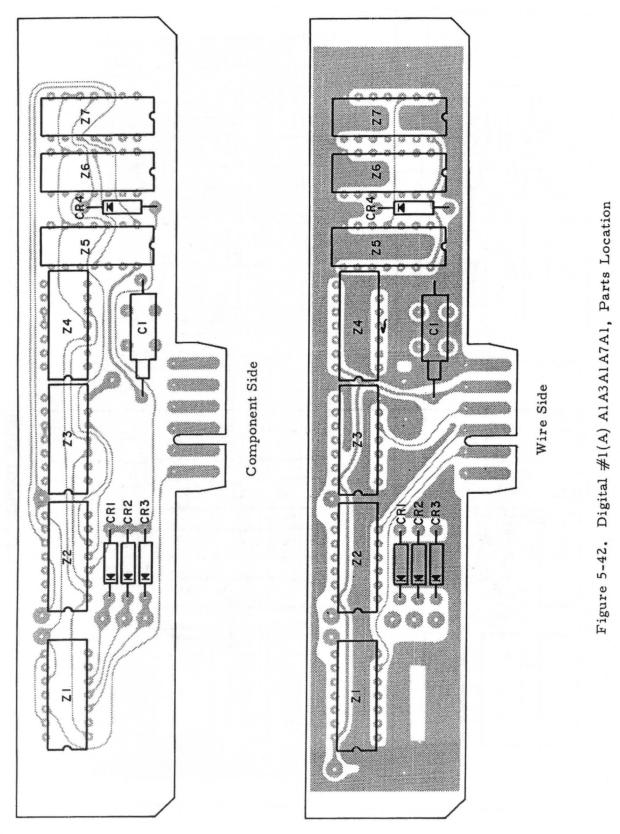

| 5-42   | Digital #1(A) AlA3AlA7Al, Parts Location                                  | 5-80 |

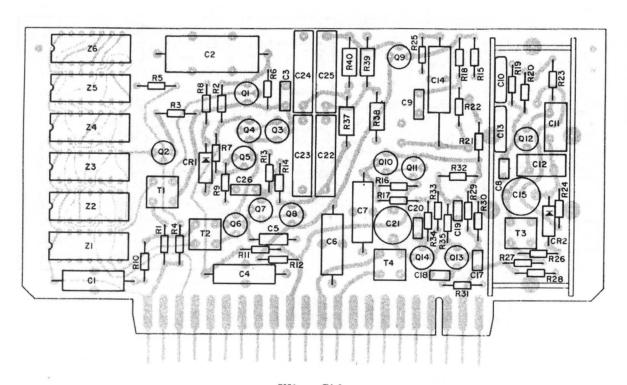

| 5-43   | Digital #1(B) AlA3AlA7A2, Parts Location                                  | 5-81 |

| 5-44   | Mixer/Multiplier AlA3A2, X4 Multiplier Al, Parts Location                 | 5-82 |

| 5-45   | Mixer/Multiplier A1A3A2, X10 Multiplier A2, Parts Location                | 5-83 |

| 5-46   | Power Supply AlA3PS1, Parts Location (Sheet 1)                            | 5~84 |

x ORIGINAL

| FIGURE | TITLE                                                                                    | PAGE  |

|--------|------------------------------------------------------------------------------------------|-------|

| 5-47   | Power Supply AlA3PS1, Parts Location (Sheet 2)                                           | 5-85  |

| 5-48   | Power Supply AlA3PS1, Parts Location (Sheet 3)                                           | 5-86  |

| 5-49   | Power Supply AlA3PS1; +5 Volt and +18 Volt Regulators (A3A1), Parts Location             | 5-87  |

| 5-50   | Power Supply AlA3PS1; +15 Volt Regulator (A3A2), Parts Location                          | 5-88  |

| 5-51   | Rear-Deck Supply Decoupling Board AlA3A3, Parts Location                                 | 5-89  |

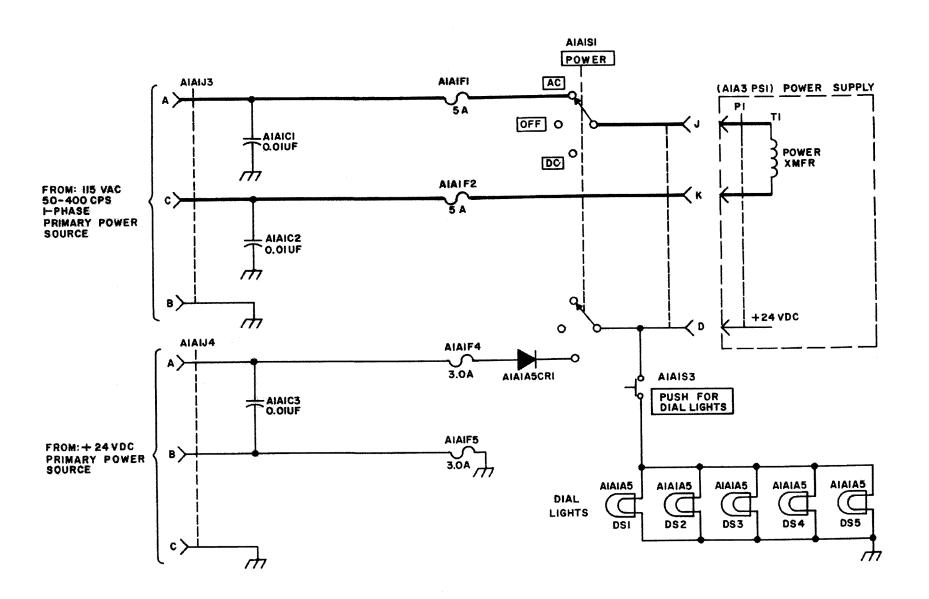

| 5-52   | Primary Power Distribution, Schematic Diagram                                            | 5-91  |

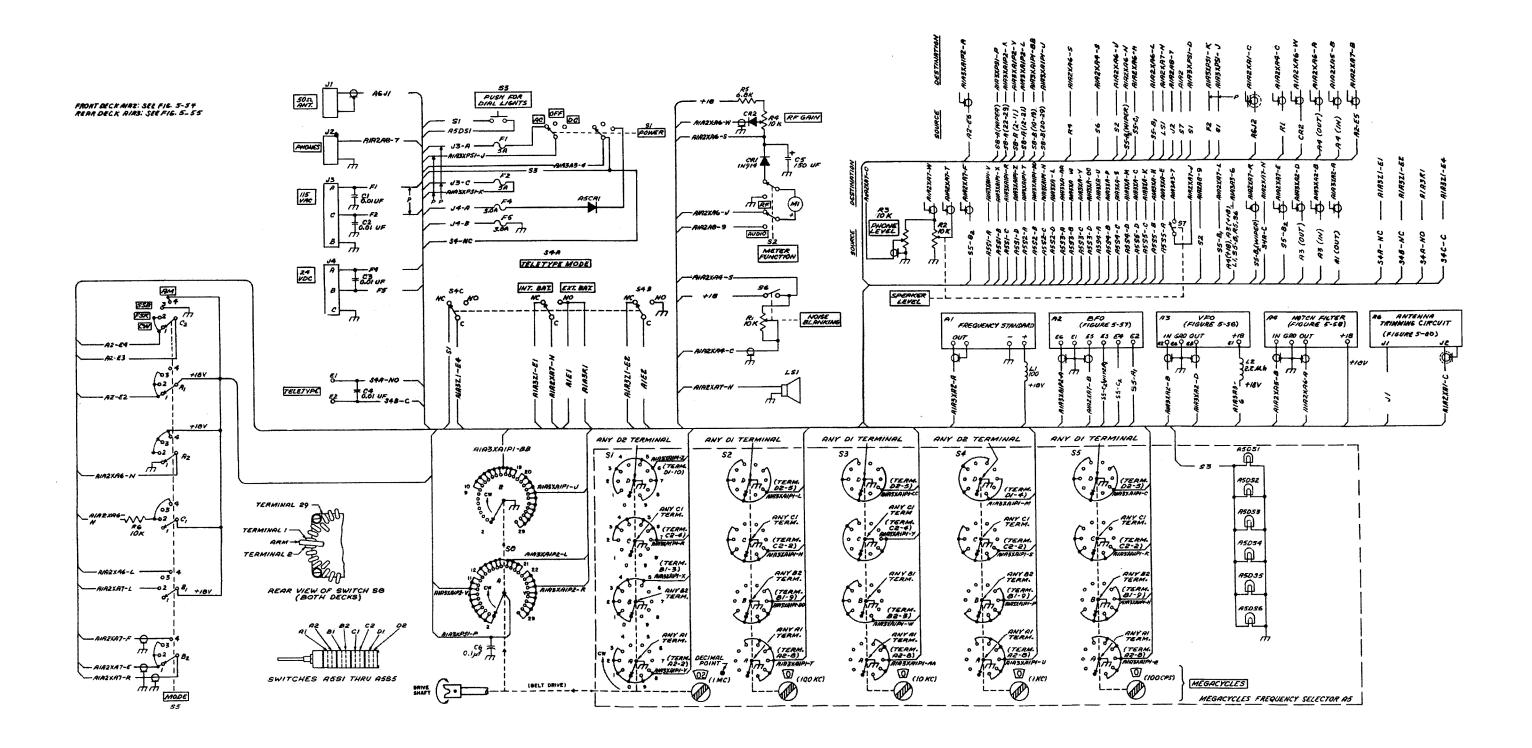

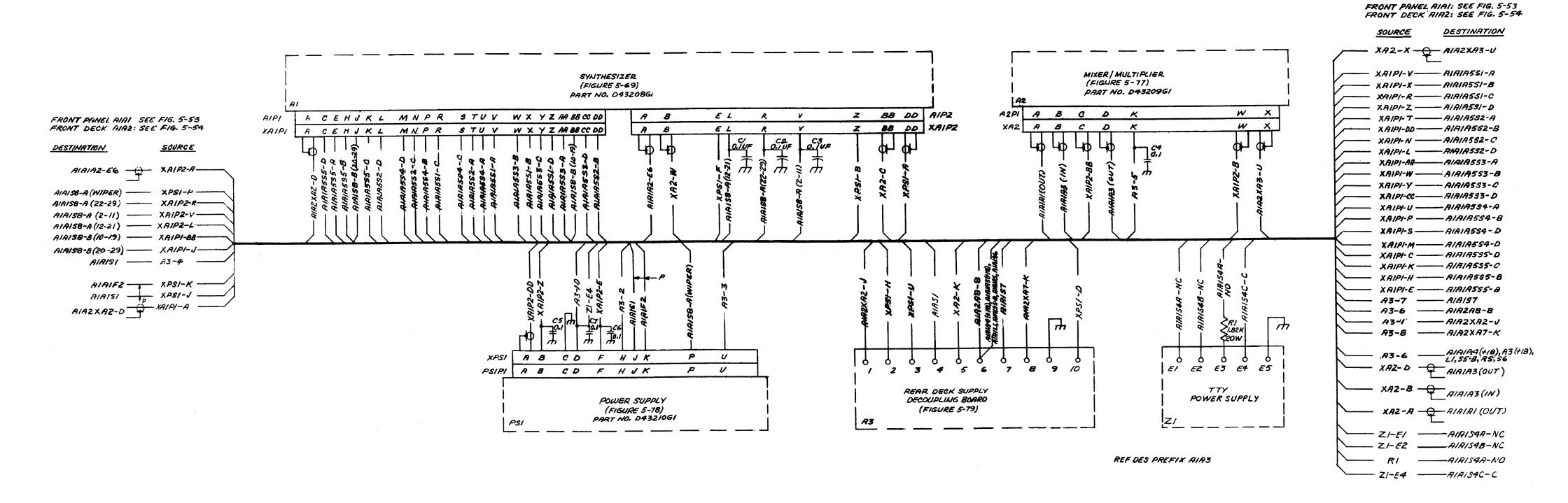

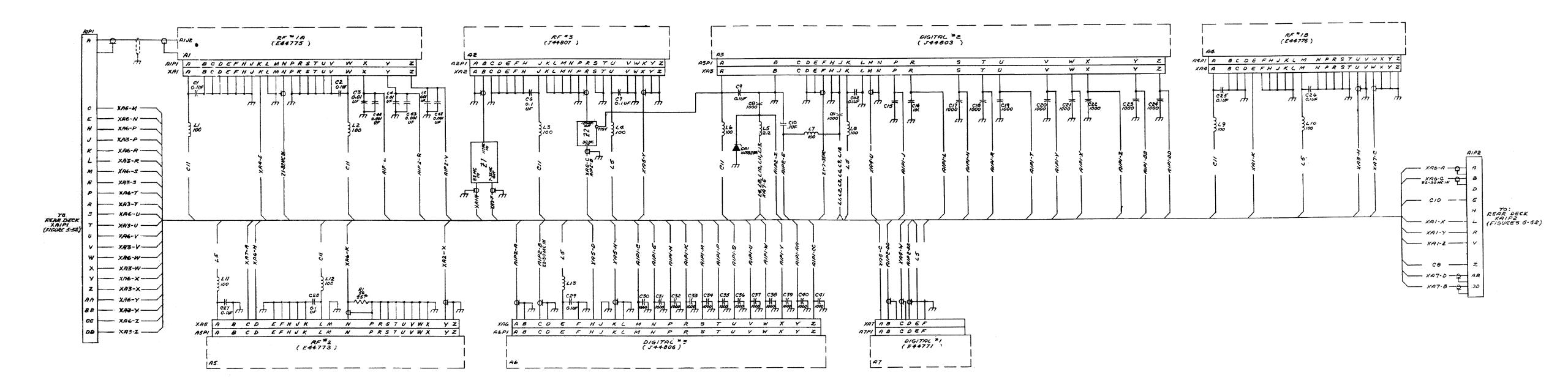

| 5-53   | Receiver, Radio R-1490/GRR-17 Module Interconnection Diagram (Sheet 1, Front Panel A1A1) | 5-93  |

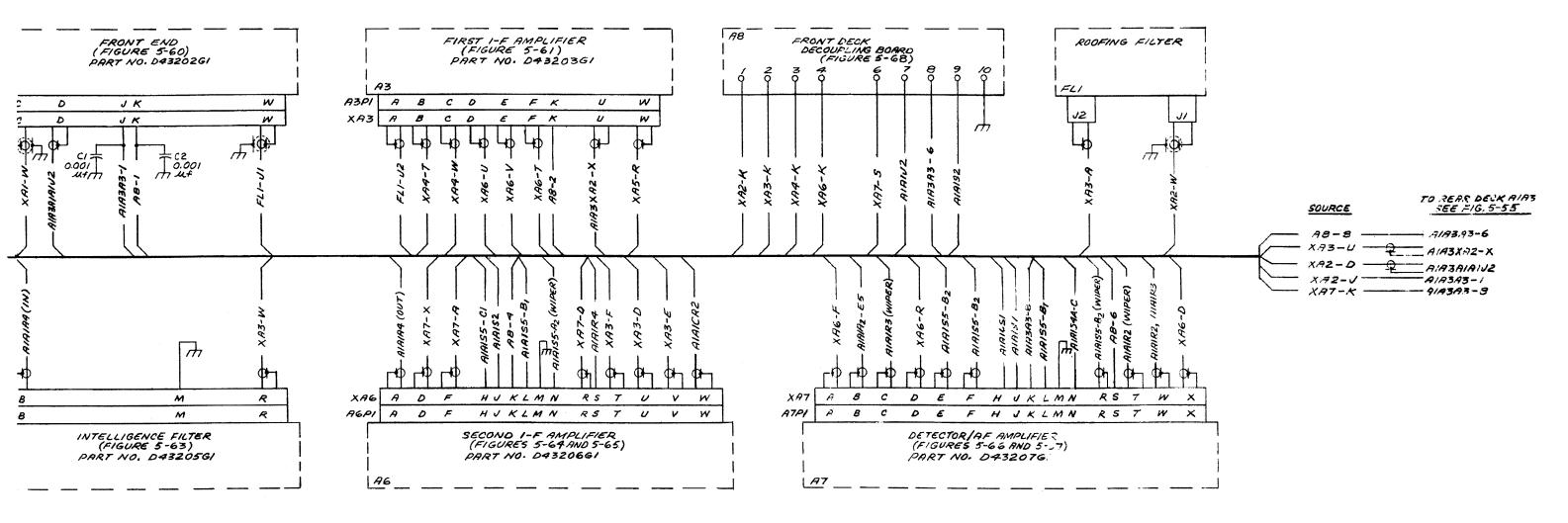

| 5-54   | Receiver, Radio R-1490/GRR-17 Module Interconnection Diagram (Sheet 2, Front Deck A1A2)  | 5-95  |

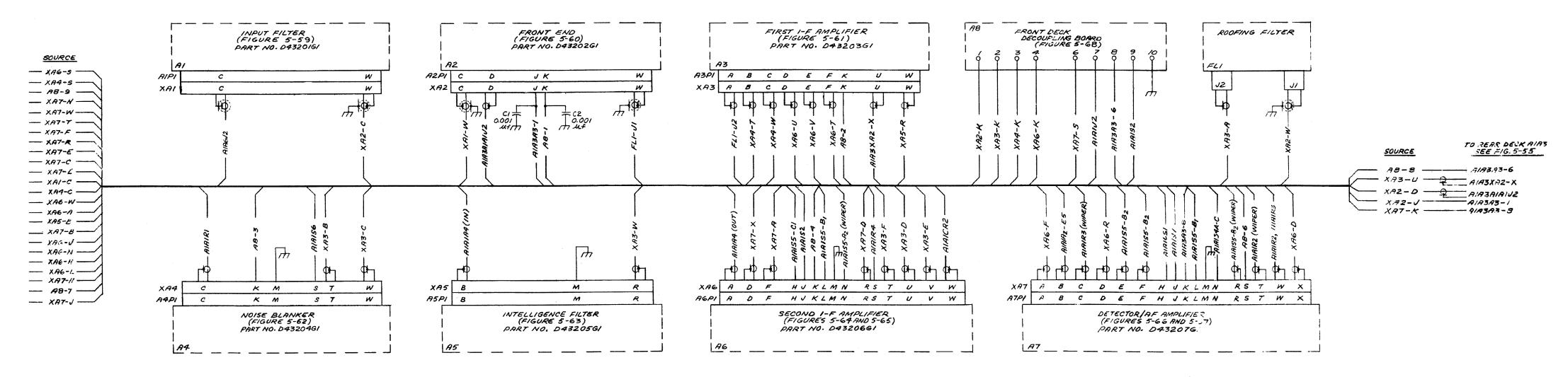

| 5-55   | Receiver, Radio R-1490/GRR-17 Module Interconnection Diagram (Sheet 3, Rear Deck A1A3)   | 5-97  |

| 5-56   | VFO AlAlA3, Schematic Diagram                                                            | 5-99  |

| 5-57   | BFO AlAlA2, Schematic Diagram                                                            | 5-101 |

| 5-58   | Notch Filter AlAlA4, Schematic Diagram                                                   | 5-103 |

| 5-59   | Input Filter AlA2Al, Schematic Diagram                                                   | 5-105 |

| 5-60   | Front End AlA2A2, Schematic Diagram                                                      | 5-107 |

| 5-61   | First I-F Amplifier AlA2A3, Schematic Diagram                                            | 5-109 |

| 5-62   | Noise Blanker / 1A2A4, Schematic Diagram                                                 | 5-111 |

| 5-63   | Intelligence Filter AlA2A5, Schematic Diagram                                            | 5-113 |

| 5-64   | Second I-F/AGC Amplifier AlA2A6, Schematic Diagram (Sheet 1)                             | 5-115 |

| 5-65   | Second I-F/AGC Amplifier A1A2A6, Schematic Diagram (Sheet 2)                             | 5-117 |

| 5-66   | Detector/AF Amplifier AlA2A7, Schematic Diagram (Sheet 1)                                | 5-119 |

| 5-67   | Detector/AF Amplifier A1A2A7, Schematic Diagram (Sheet 2)                                | 5-121 |

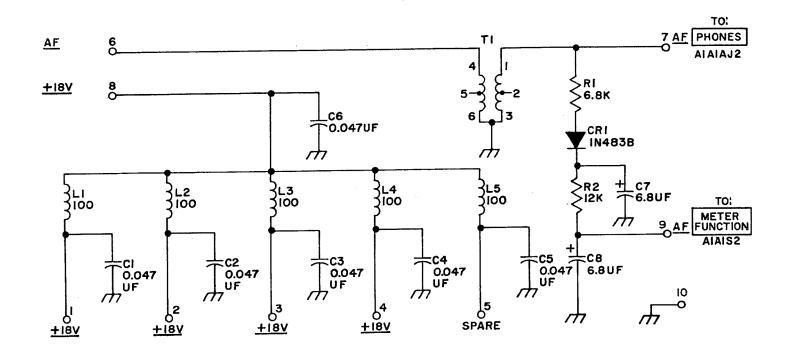

| 5-68   | Front Deck Supply Decoupling Board AlA2A8, Schematic Diagram                             | 5-123 |

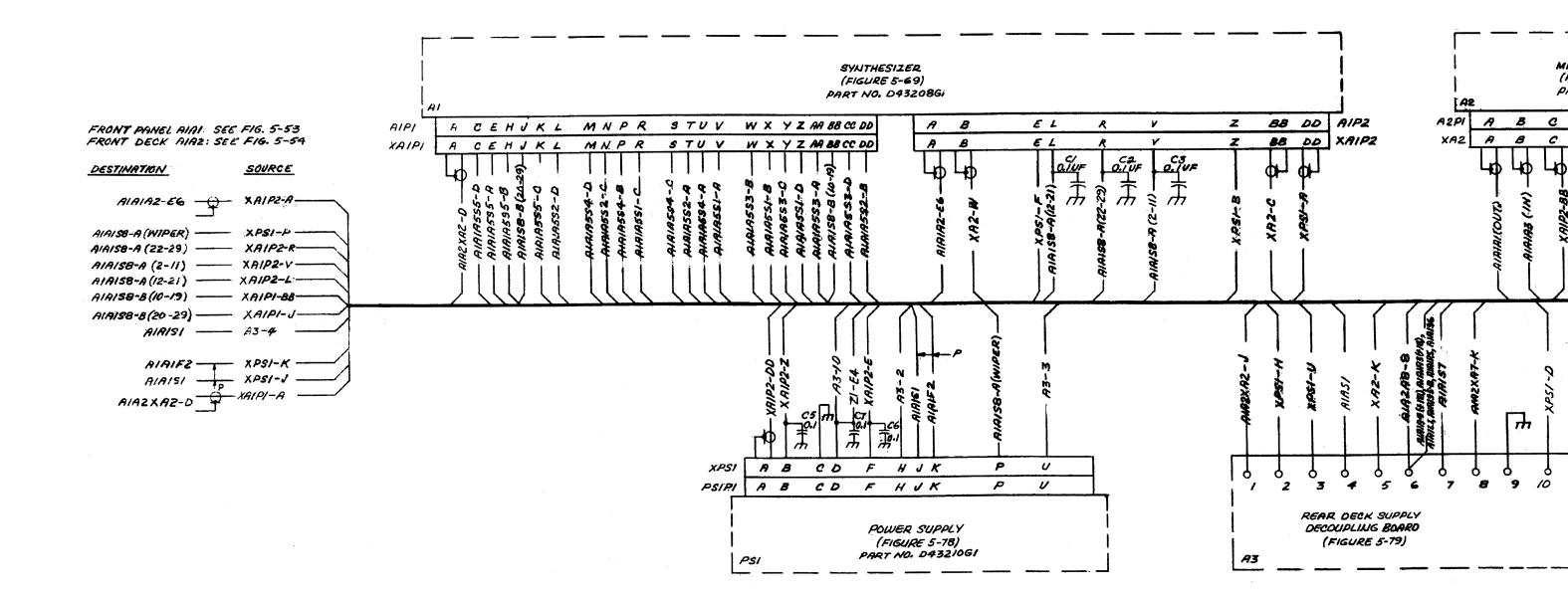

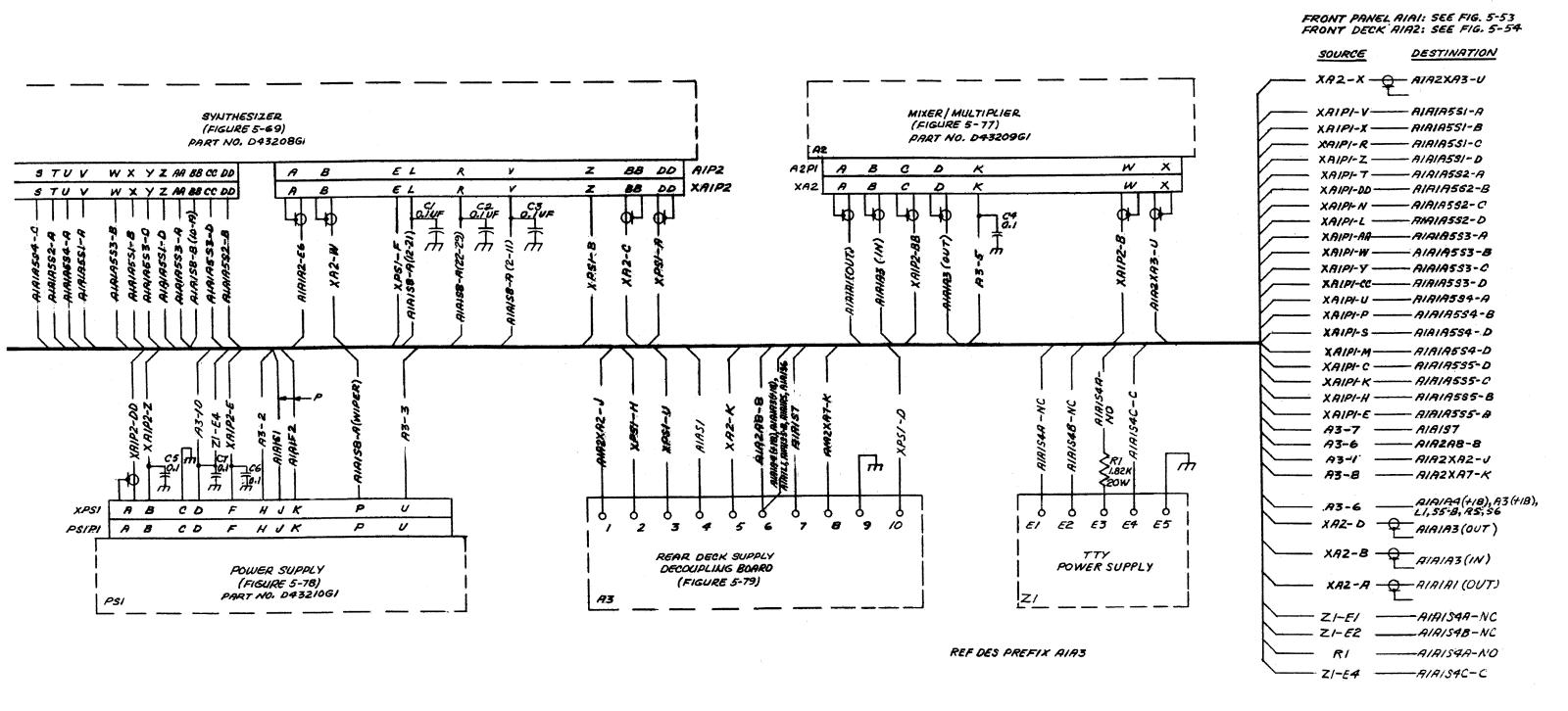

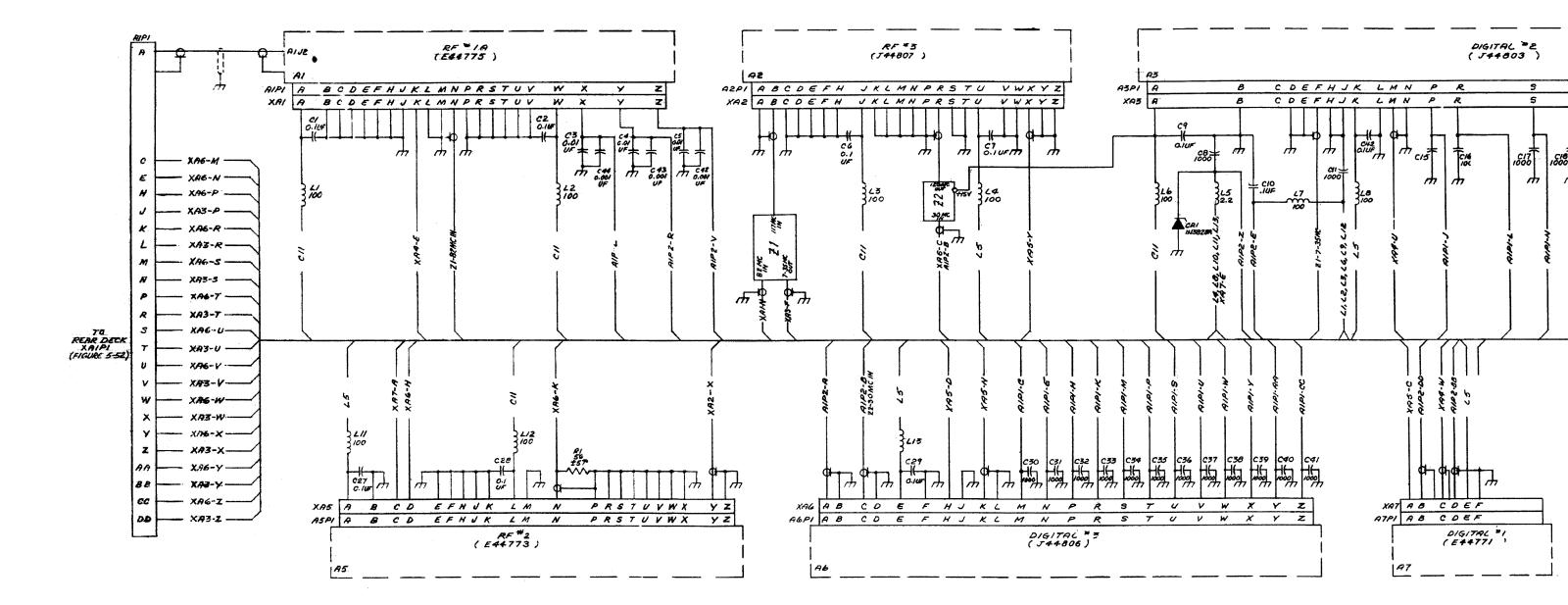

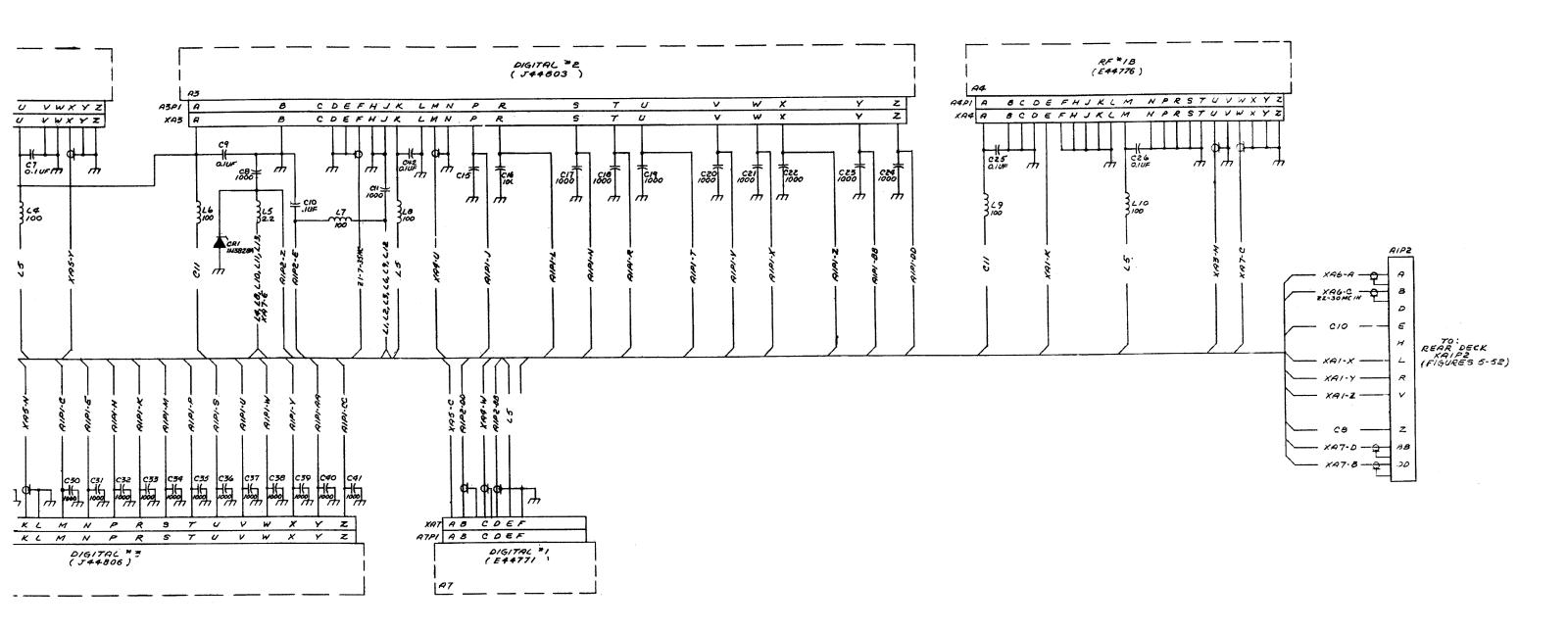

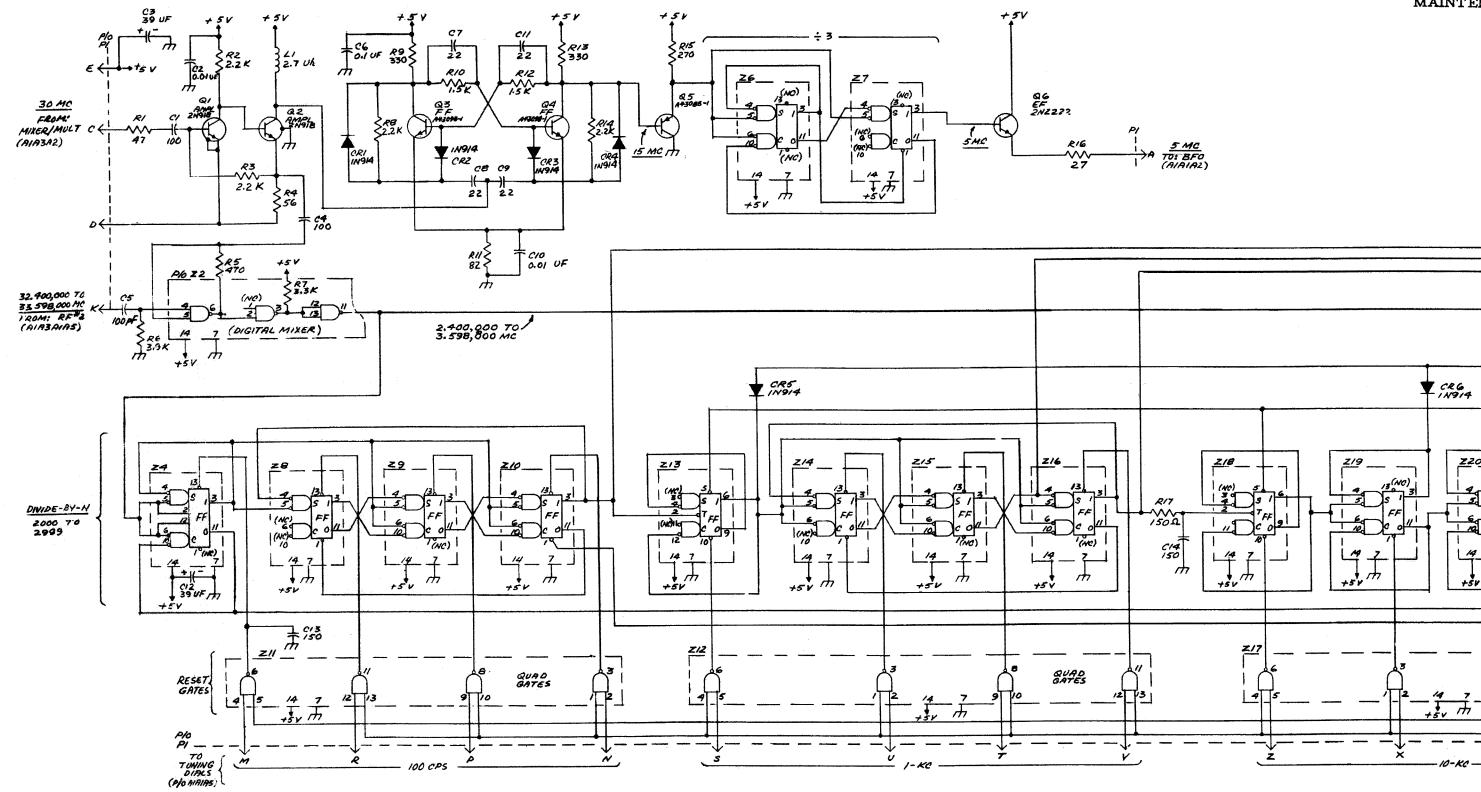

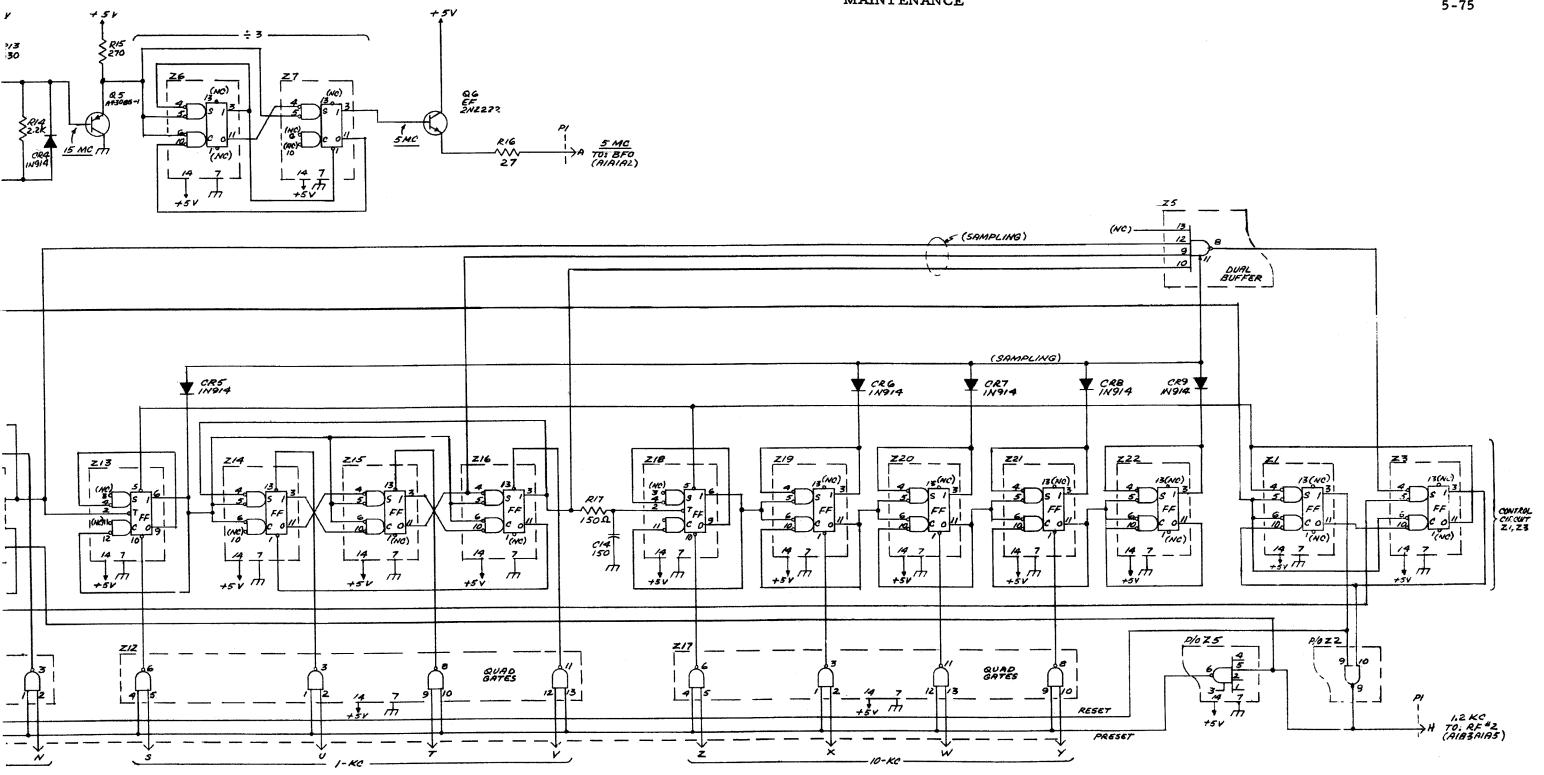

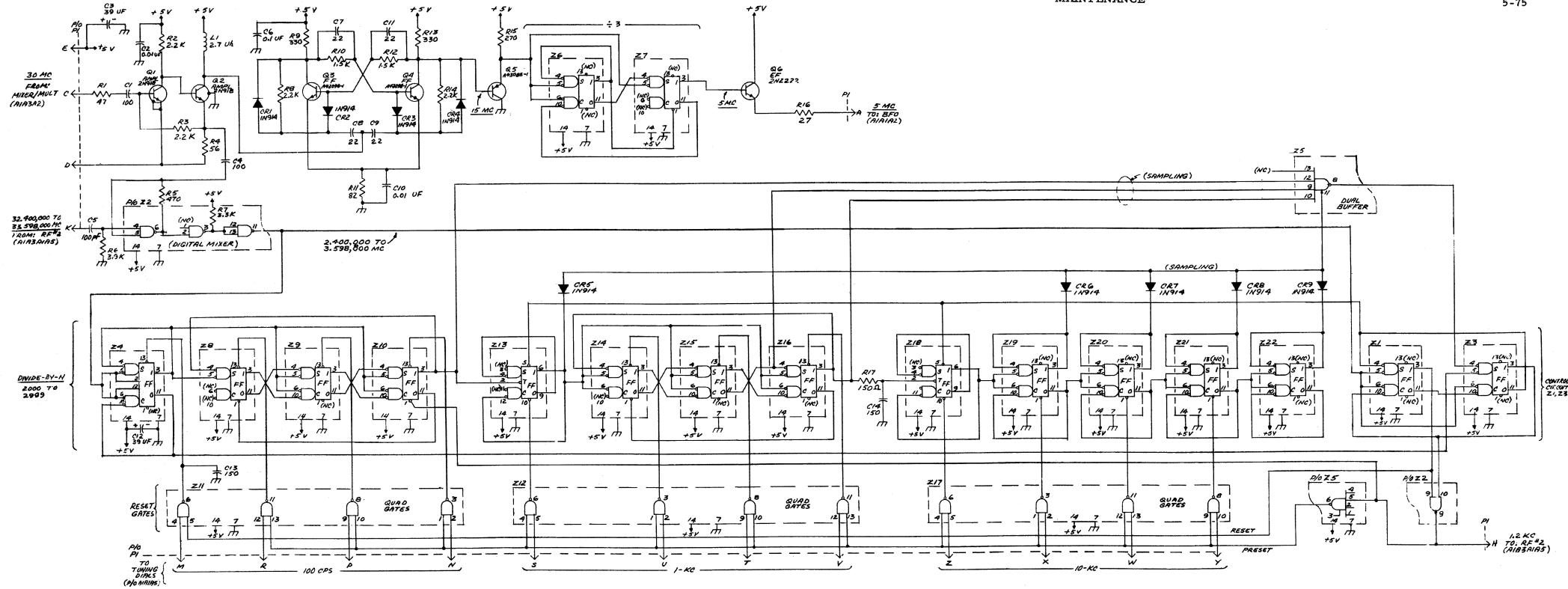

| 5-69   | Synthesizer A1A3A1, Interconnection Diagram                                              | 5-125 |

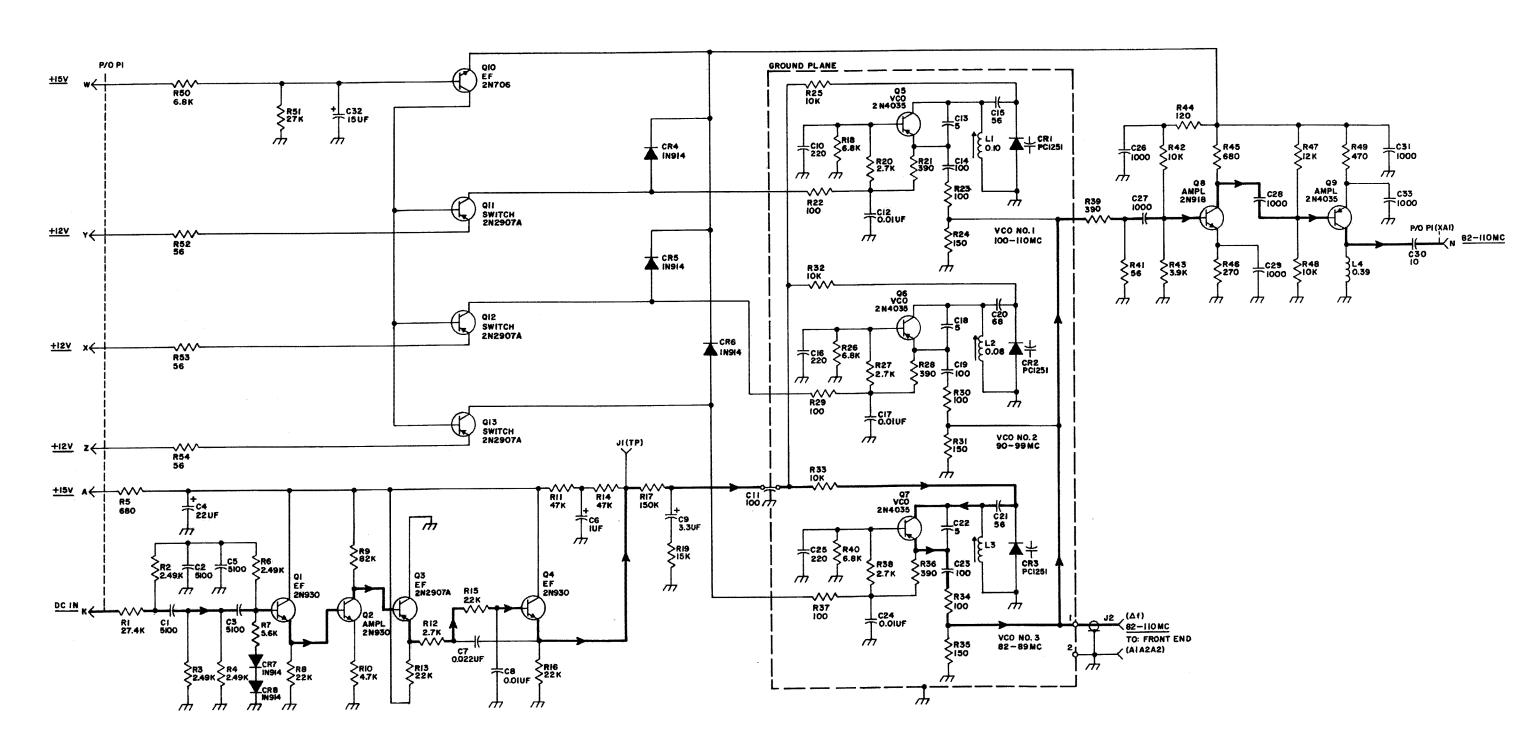

| 5-70   | RF #1(A) AlA3AlAl, Schematic Diagram                                                     | 5-127 |

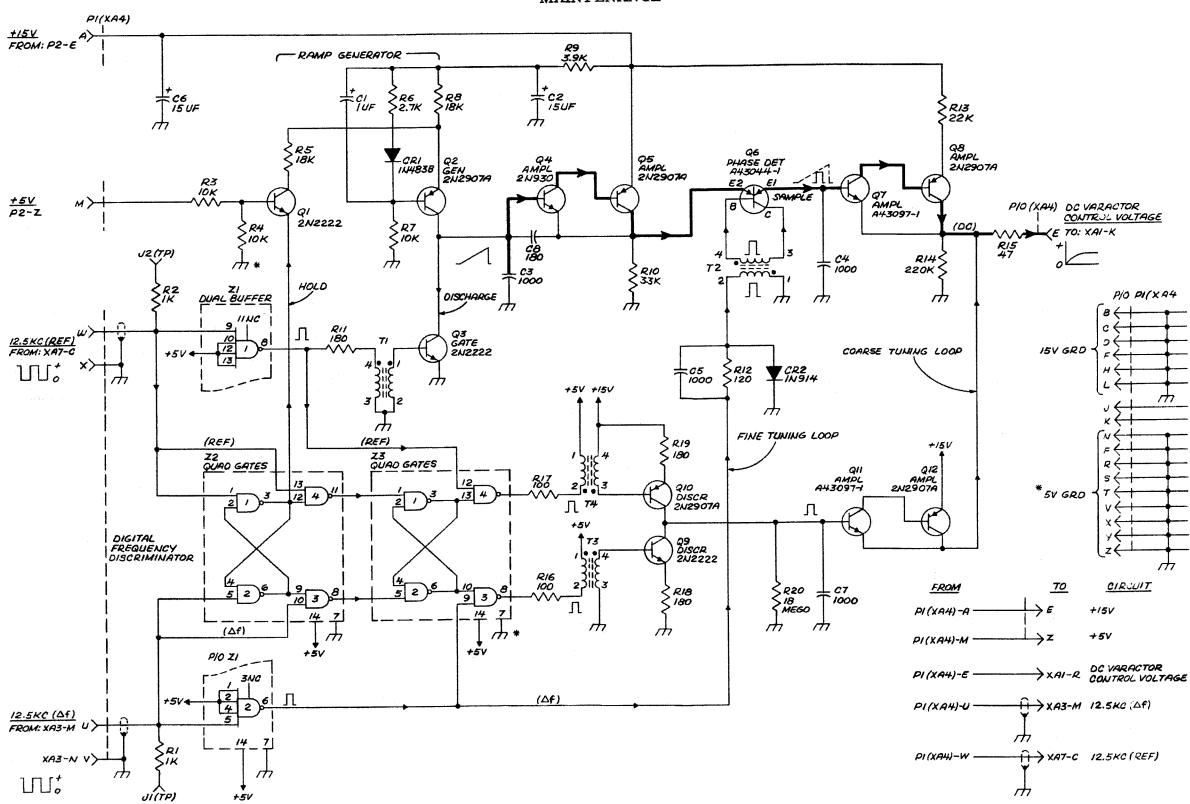

| 5-71   | RF #1(B) A1A3A1A4, Schematic Diagram                                                     | 5-129 |

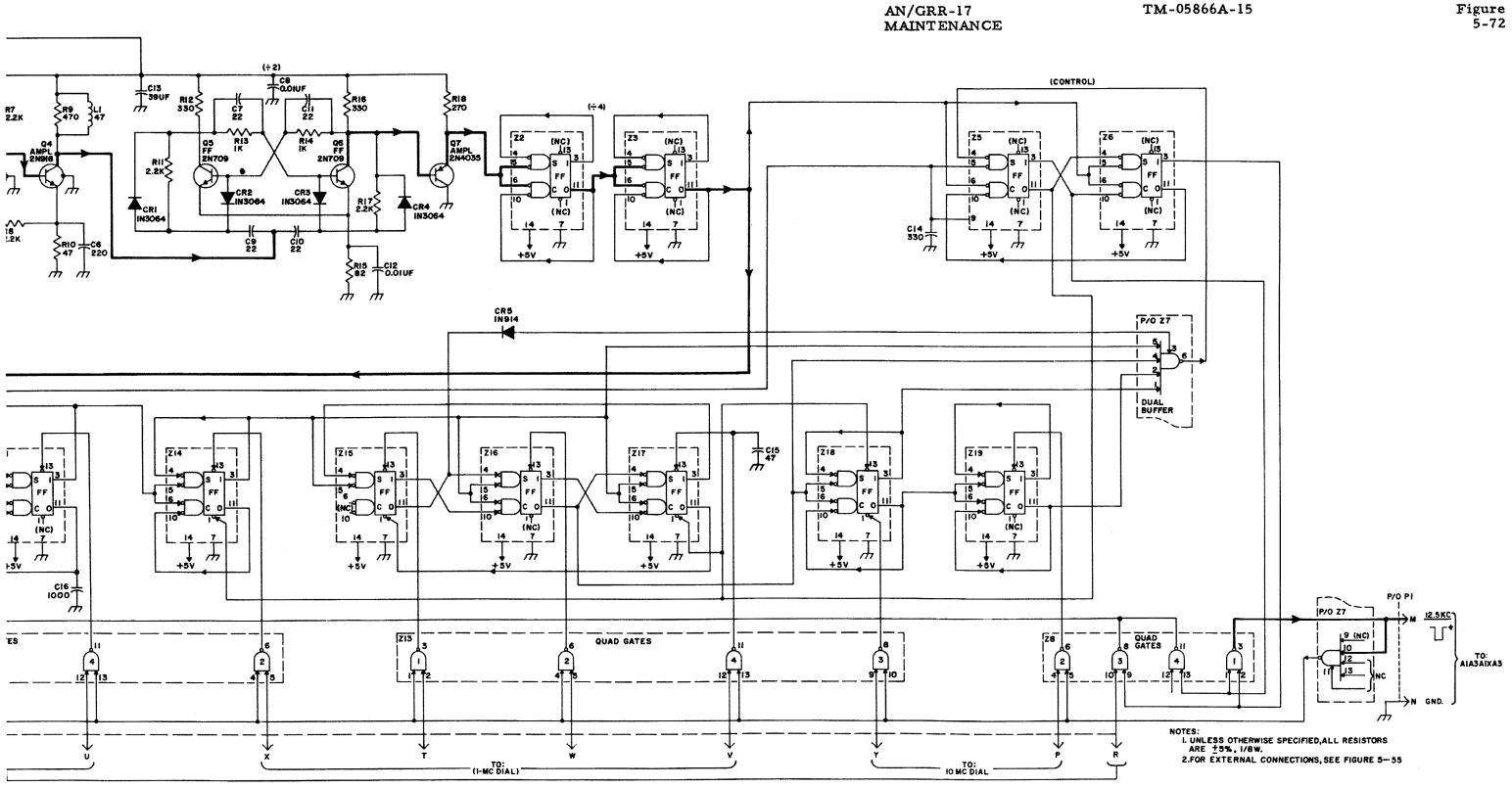

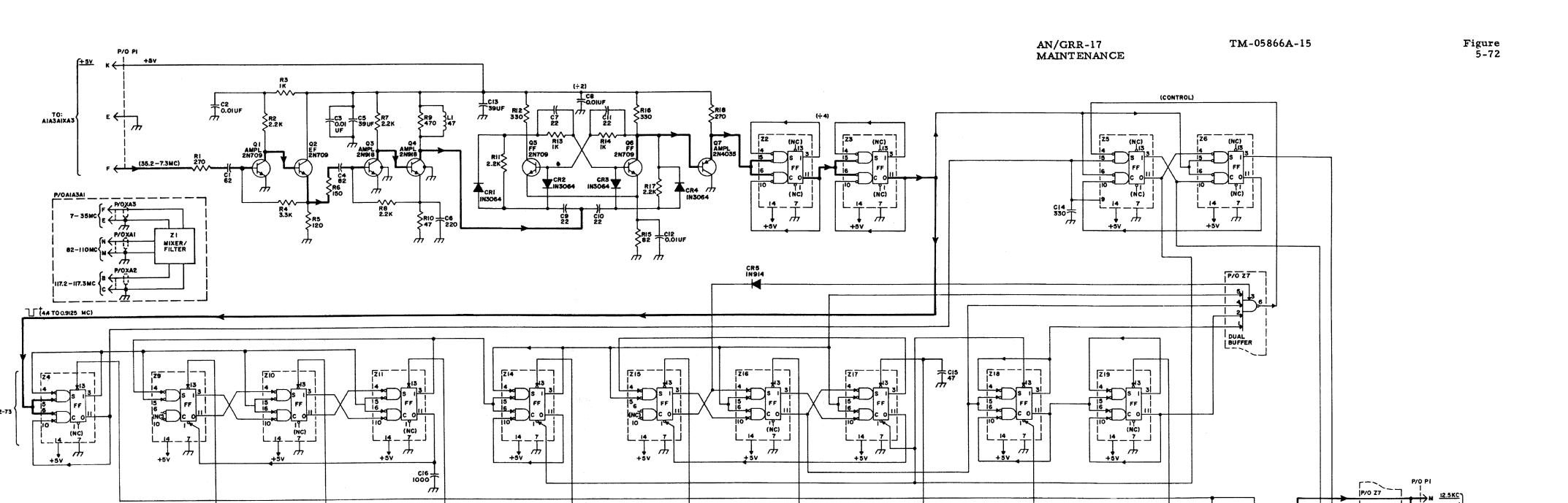

| 5-72   | Digital #2 AlA3AlA3, Schematic Diagram                                                   | 5-131 |

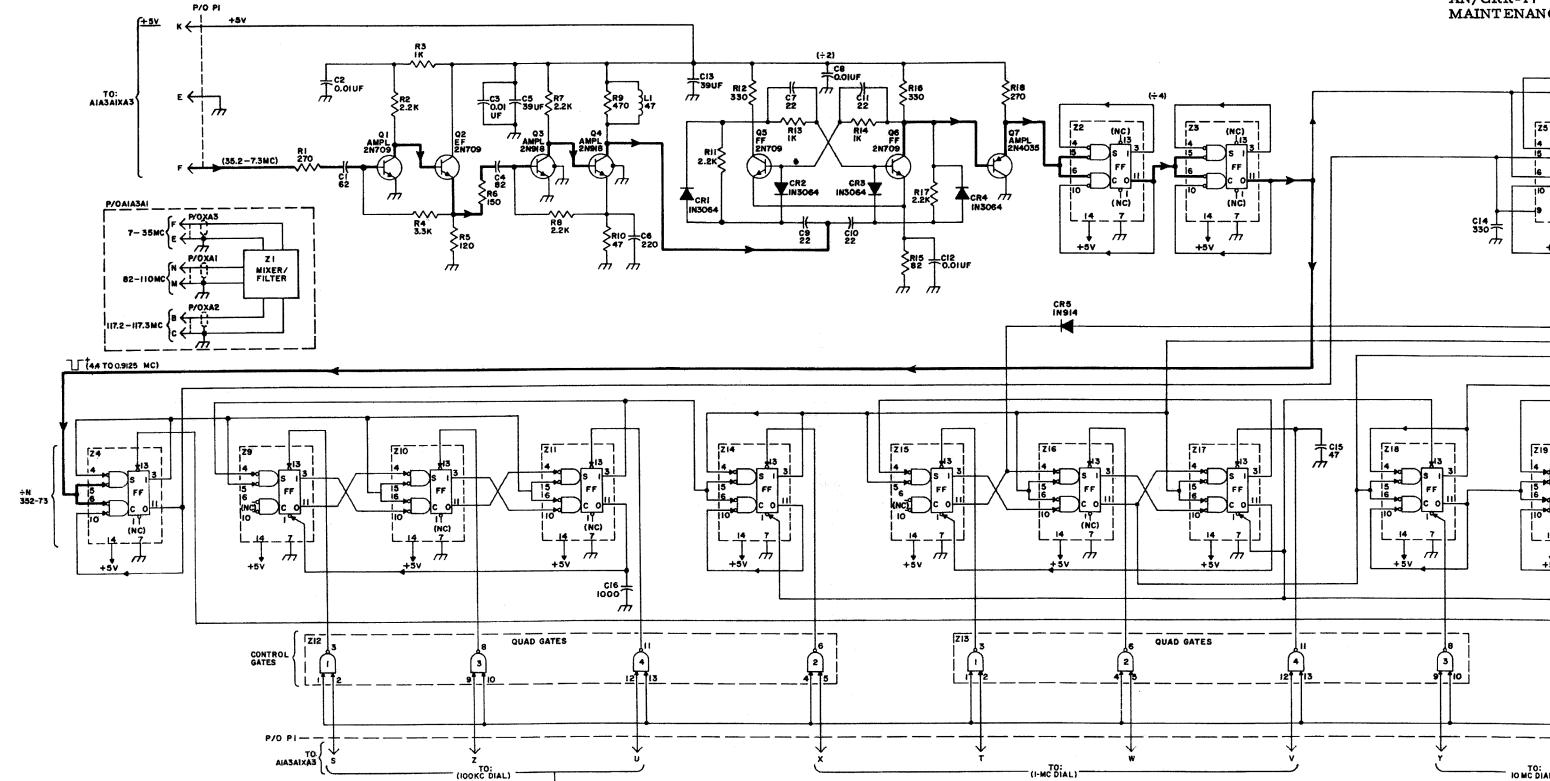

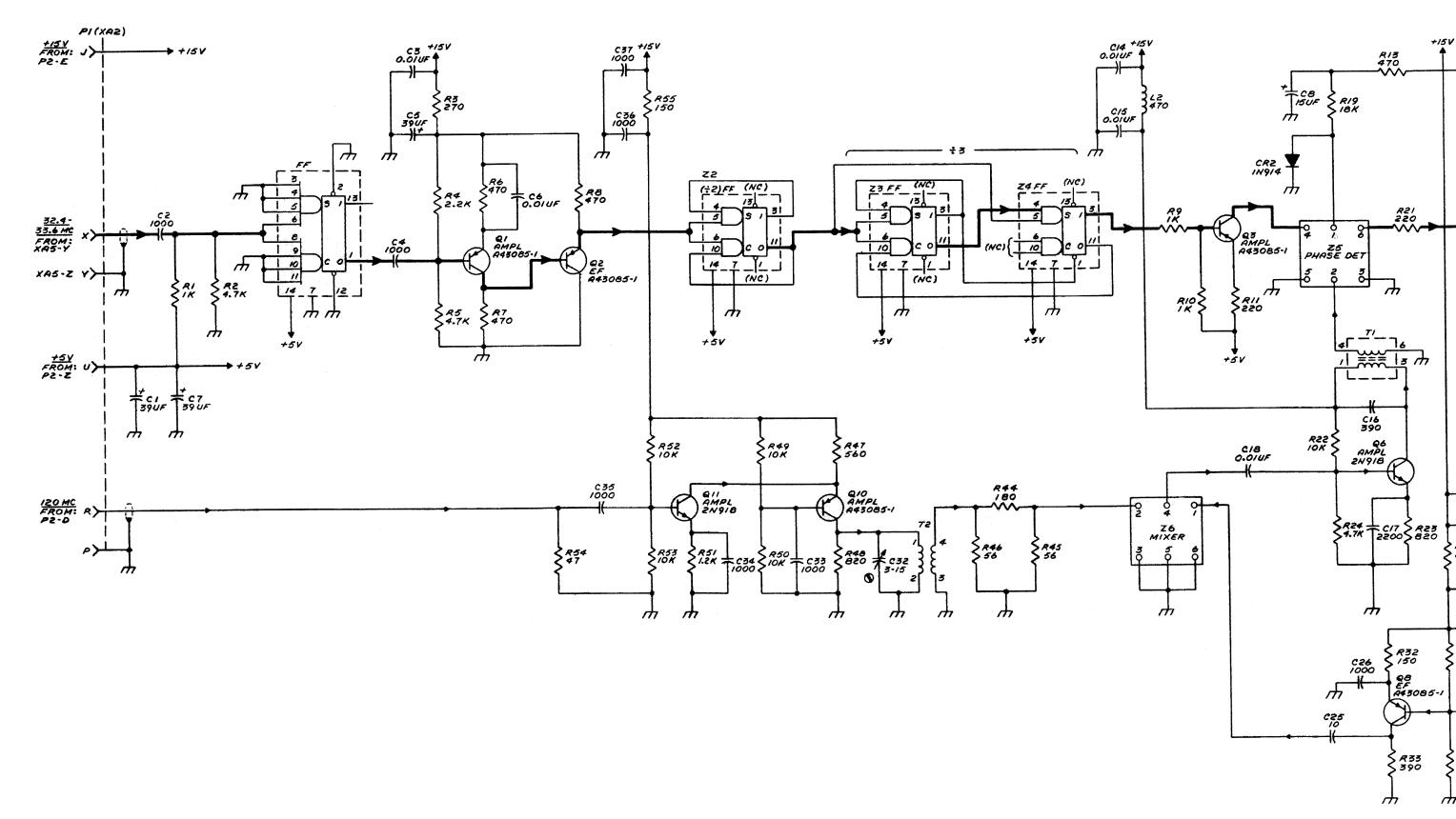

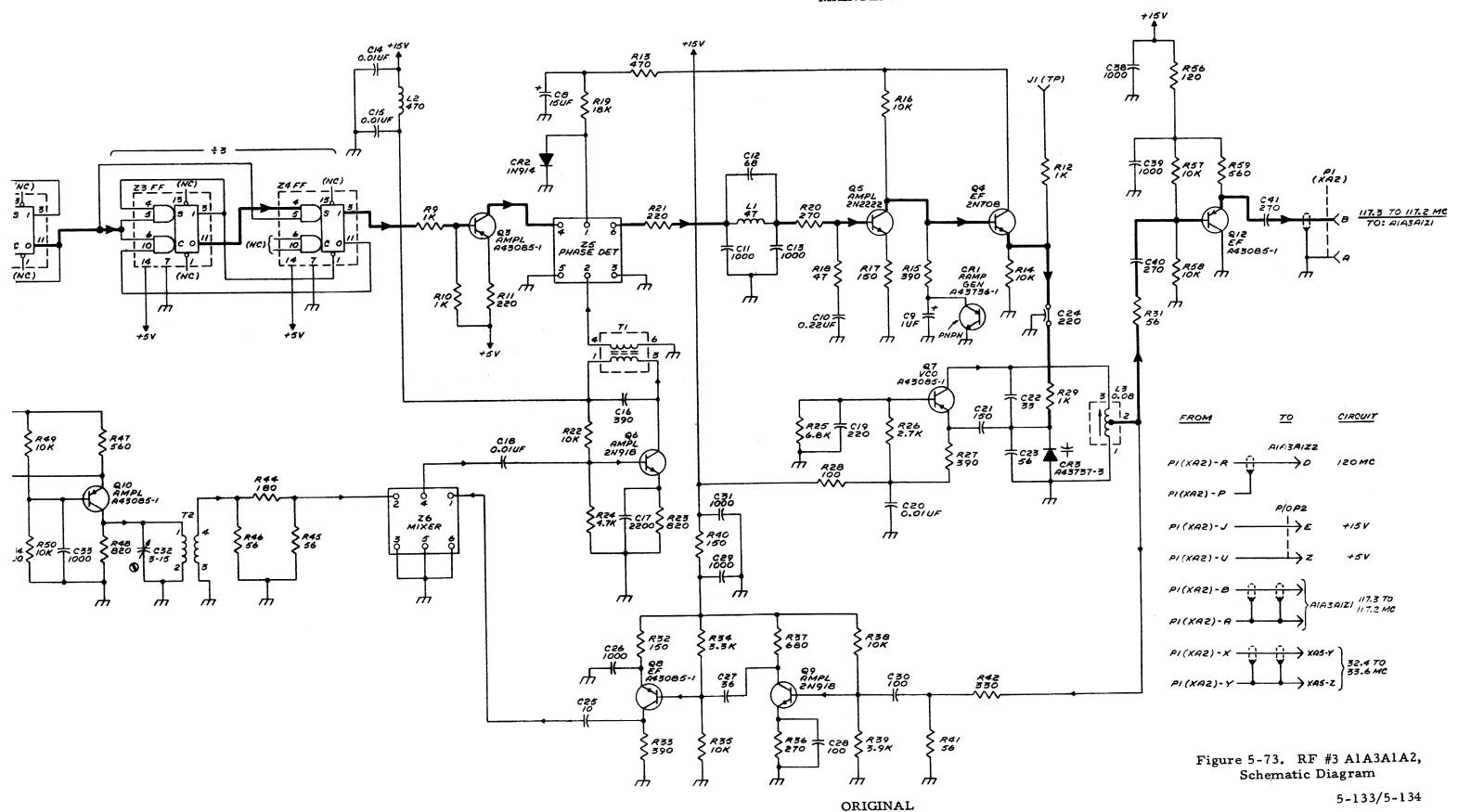

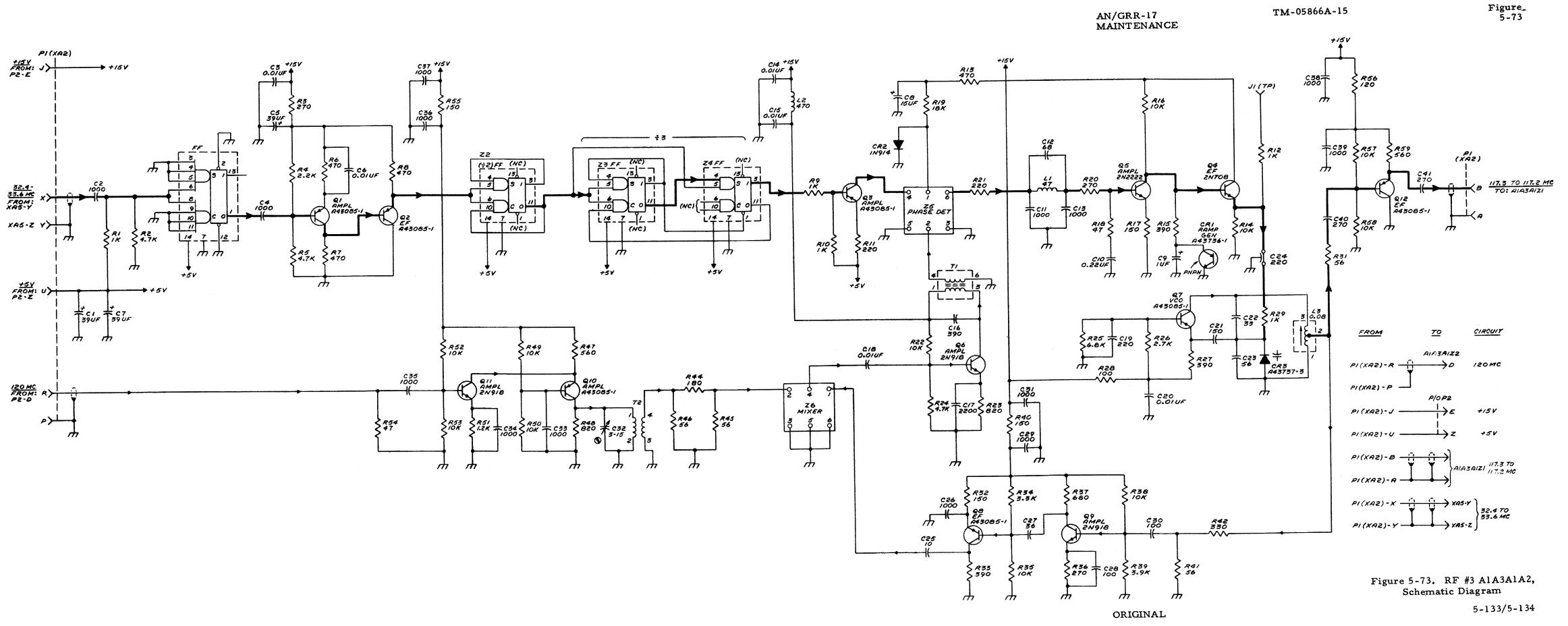

| 5-73   | RF #3 A1A3A1A2, Schematic Diagram                                                        | 5-133 |

| 5-74   | RF #2 A1A3A1A5, Schematic Diagram                                                        | 5-135 |

| 5-75   | Digital #3 AlA3AlA6, Schematic Diagram                                                   | 5-137 |

| 5-76   | Digital #1 AlA3AlA7, Schematic Diagram                                                   | 5-139 |

| 5-77   | Mixer/Multiplier A1A3A2, Schematic Diagram (Sheet 1 of 2)                                | 5-141 |

| 5-77   | Mixer/Multiplier AlA3A2, Schematic Diagram (Sheet 2 of 2)                                | 5-143 |

| 5-78   | Power Supply AlA3PS1, Schematic Diagram                                                  | 5-145 |

| 5-79   | Rear Deck Supply Decoupling Board AlA3A3, Schematic Diagram                              | 5-147 |

| 5-80   | Antenna Trimming Circuit AlAlA6, Schematic Diagram                                       | 5-149 |

ORIGINAL xi/xii

#### LIST OF TABLES

| TABLE | TITLE                                                | PAGE  |

|-------|------------------------------------------------------|-------|

| 1-1   | Equipment Supplied                                   | 1-4   |

| 1-2   | Equipment Required but Not Supplied                  | 1-4   |

| 1-3   | Shipping Data                                        | 1-5   |

| 2-1   | Connectors Supplied and External Cable Requirements  | 2-7   |

| 3-1   | Operating Modes and Bandwidth Selections             | 3-3   |

| 3-2   | Operating Controls and Devices                       | 3-3   |

| 3-3   | Radio Receiver R-1490/GRR-17, Summary of Operation   | 3-10  |

| 3-4   | Radio Receiver R-1490/GRR-17, Trouble Shooting Guide | 3-15  |

| 4-1   | Megacycles-Dials Binary Code                         | 4-79  |

| 4-2   | Megacycles-Dials Test Data                           | 4-81  |

| 4-3   | Variable (÷10) Counter, Programming                  | 4-100 |

| 5-1   | Test Equipment Required for Preventive Maintenance   | 5-2   |

| 5-2   | Reference Standards Tests                            | 5-3   |

| 5-3   | Preventive Maintenance Procedures                    | 5-4   |

| 5-4   | Recommended Periodic Maintenance Schedule            | 5-8   |

ORIGINAL

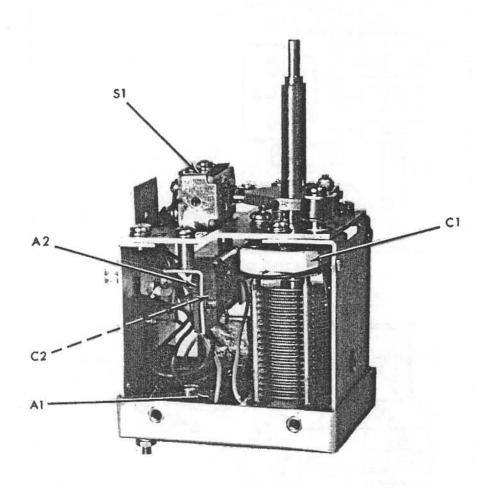

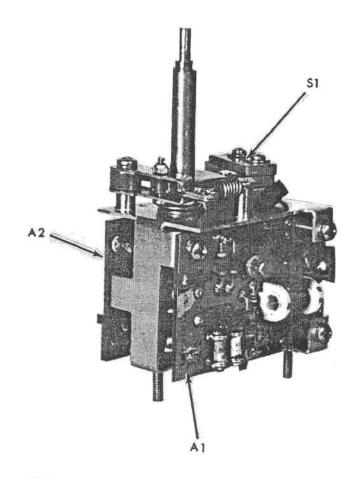

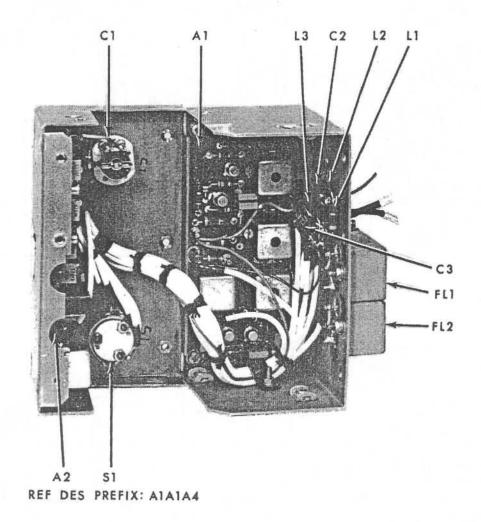

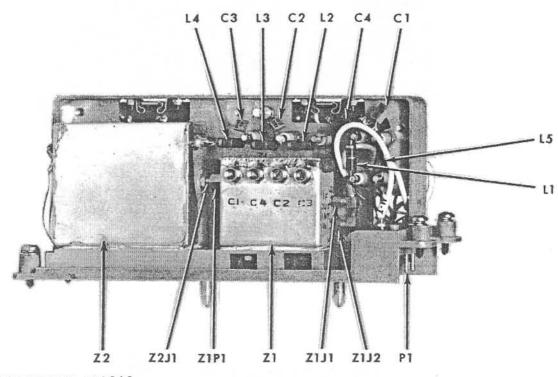

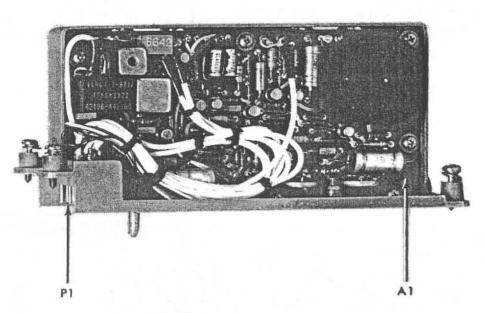

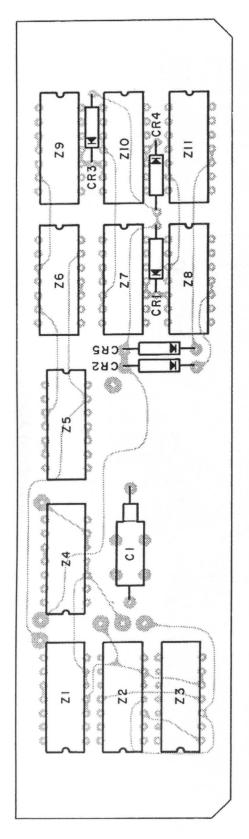

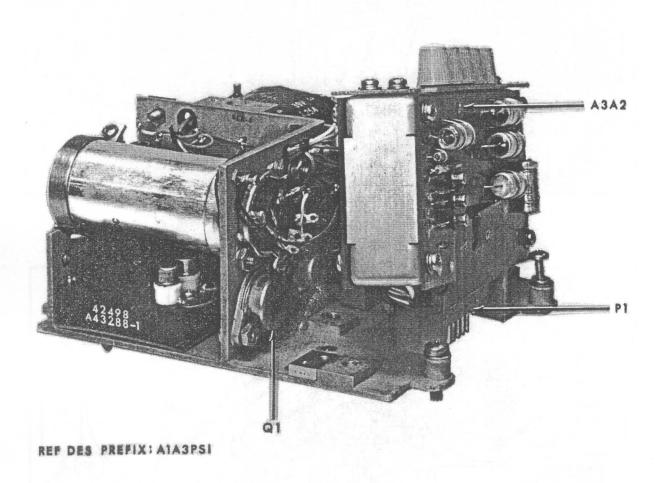

Figure 1-1. Radio Receiving Set AN/GRR-17

#### SECTION 1

#### GENERAL INFORMATION

#### 1-1. INTRODUCTION.

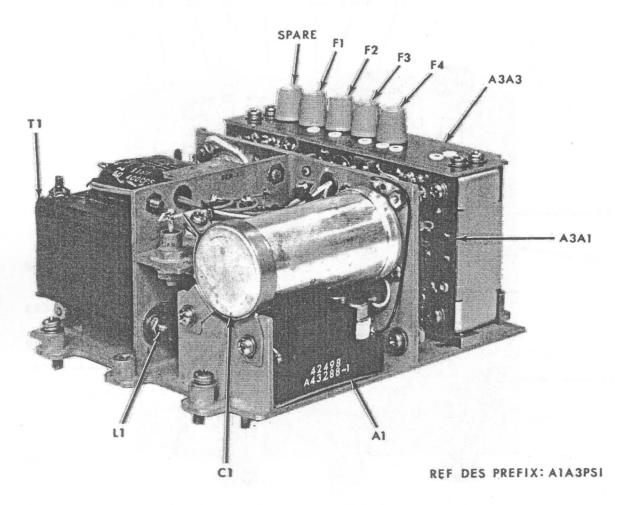

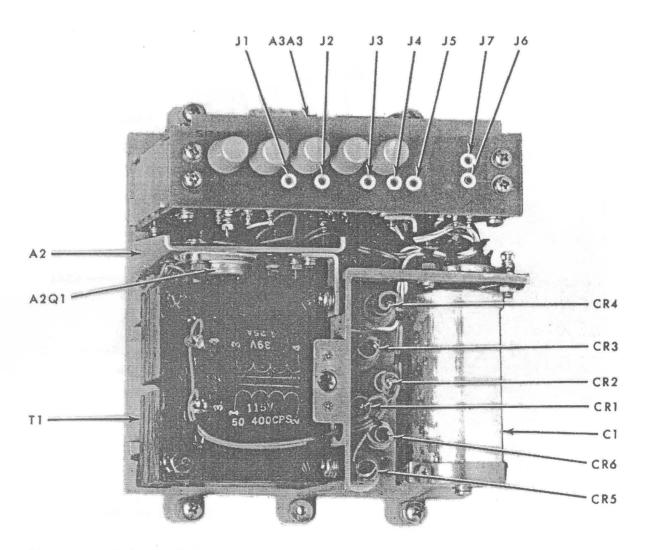

Radio Receiving Set AN/GRR-17 consists of Radio Receiver R-1490/GRR-17 and Transit Case D43611G1. A general view of the set appears in figure 1-1. The set is intended for ground installations and is operationally compatible with Radio Set AN/TRC-75, Radio Receiver-Transmitter RT-671/PRC-47, and Teletype-writer Set AN/TGC-14A(V). The set is operable with the transit case attached following removal of the case cover, or it can be installed in a standard relay rack when the transit case is removed. Radio Receiver R-1490/GRR-17 combines high performance and reliability characteristics with light weight, small size, solid state circuits, and low operating power requirements.

#### 1-2. FUNCTIONAL DESCRIPTION.

Radio Receiver R-1490/GRR-17 is a high dynamic range, dual-conversion superheterodyne receiver for the frequency range from 2.0 to 30.0 mc, employing a digital synthesizer for virtually instantaneous frequency selection. Tuning, in increments of 100 cycles, is performed by setting five tuning dials to the signal frequency in megacycles. Vernier tuning of each 100 cycles step is also provided. The operating modes are for reception of upper or lower single sideband (A3j), amplitude modulated (A3), continuous wave (A1), and frequency shift teletype (F1) broadcasts. A panel mounted speaker permits signal monitoring. Output terminations are provided for the connection of external teletype equipment, and a headset or other terminal equipment. The receiver frequency stability is one part in  $10^7$  per day allowing extended operating periods without operator attention.

The receiver is of modular construction with hinged front panel, front deck, and rear deck sections for easy access. Circuit modules are of the plug-in type to facilitate field maintenance.

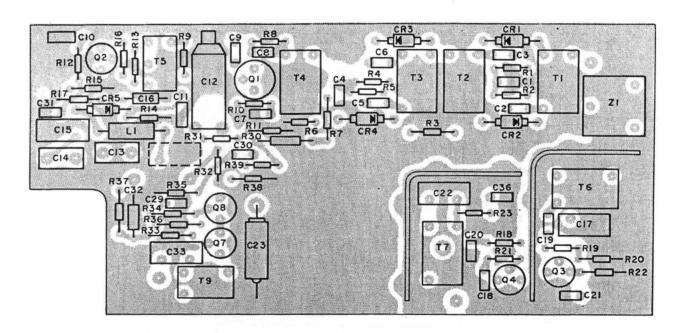

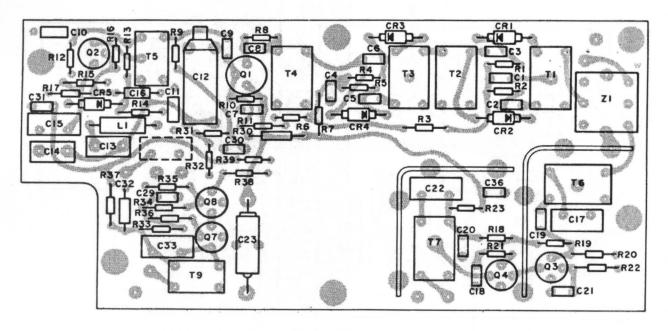

The front panel section contains all the controls, switches, meters, jacks, and terminal connections for the operation and calibration of the receiver in all reception modes. It also contains the frequency standard, bfo, notch filter, vfo, and antenna trimming circuit modules. The panel section is equipped with extension flaps for rack mounting which fold aside when the transit case is attached.

The front deck section contains the main signal path modules consisting of the vhf oscillator, i-f amplifiers, mixers, detectors, and audio amplifier circuits. The rear deck section contains the synthesizer circuit modules supplying all of the tuning injection frequencies required for signal path circuit operation. Power supply circuits are also located on the rear deck.

ORIGINAL 1-1

Receiver operation requires a primary power source of 105 to 125 volts ac, 50 to 400 cycles per second, single phase, or a nominal 24 volt dc power source. Primary power consumption, from the ac source, is a nominal 50 watts, and from a dc source is 24 watts, with the panel lamps "off" and the receiver delivering 15 milliwatts of audio output. (Speaker and noise blanker off.)

#### 1-3. QUICK REFERENCE DATA.

- a. GENERAL.

- (1) NOMENCLATURE: Radio Receiving Set AN/GRR-17

- (2) CONTRACT NUMBER: NObsr-95315

- (3) CONTRACTOR: National Radio Company, Inc., Melrose, Massachusetts, 02176, U.S.A.

- (4) DATE OF CONTRACT: 11 May, 1966

- (5) COGNIZANT INSPECTOR: DCASR, Boston, Massachusetts

- (6) NUMBER OF PACKAGES: 1

- b. FUNCTIONAL CHARACTERISTICS.

- (1) PRIMARY POWER REQUIREMENTS:

- (a) Voltage: 115 vac ( $\pm 10\%$ ); frequency: 50 to 400 cps ( $\pm 5\%$ ), 1-phase; or 24 vdc ( $\pm 15\%$ ).

- (b) Current: Nominal, 0.45 amps ac; 1.0 amps dc.

- (c) Power: Nominal, 50 watts ac, 24 watts dc (no panel lamp, speaker, noise blanker, or internal TTY supply in use).

- (2) FREQUENCY RANGE: 2.0 to 29.9999 mc.

- (3) TYPE OF FREQUENCY CONTROL:

- (a) Incremental tuning: Five digital-type selector switches for tuning in 100 cps increments. Controlled by 3 mc crystal oscillator frequency standard.

- (b) Continuous tuning: Local oscillator tuning of each 100-cps increment by vernier control with  $\pm 150$  cps range.

- (4) TYPES OF RECEPTION: Upper or lower sideband ssb, am, cw, mcw, fsk.

- (5) MAXIMUM RECEIVER OUTPUT:

- (a) Panel speaker: 1 watt (8-ohm load replacing speaker).

- (b) Phone jack: 15 mw, 600-ohm load.

- (6) FREQUENCY STANDARD:

- (a) National Radio Company identification: 42498/42384.

- (b) Frequency: 3 mc.

- (c) Output: 1 mw, 50 ohms (min.).

- (d) Input power: +18 vdc, ±2%, no oven.

- (e) Frequency accuracy: 1 part 106 for 60 days.

- (f) Drift stability: 1 part 10<sup>7</sup> per day or 5 parts 10<sup>7</sup> for 30 days (ambient temperature constant, ±5°C (±41°F)).

- (7) RECEIVER STABILITY AND ACCURACY:

- (a) Incremental tuning: 1 part in  $10^7$  per day or 5 parts in  $10^7$  for 30 days.

- (b) Continuous tuning: Adjustment of ±150 cps at any main tuning increment.

- (8) HETERODYNE FREQUENCY RANGE:

- (a) Vhf oscillator: 82 mc to 110 mc.

- (b) Vfo (vernier tuning) oscillator: 3 mc ±150 cps range.

- (9) I-F FREQUENCIES DEVELOPED:

- (a) First conversion: 112 mc.

- (b) Second conversion: 5 mc.

- (10) RECEIVER SENSITIVITY. Listed below are the minimum antenna input signal levels (open circuit voltage from a 50 ohm source) required to produce a receiver output level of 200 milliwatts measured at the speaker terminals, or 15 milliwatts measured at the PHONES terminals, for a signal plus noise-to-noise ratio of 10 db.

| Mode      | I-F Bandwidth | Input (uv)    |

|-----------|---------------|---------------|

| Al (cw)   | 0.350 kc      | 1.5           |

| Al (cw)   | 1.0 kc        | 2.5           |

| A3 (am)   | 8.0 kc        | 3.0           |

| A3j (ssb) | 3.0 kc        | 1.5 (Usb-lsb) |

| Fl(fsk)   | 3.0 kc        | 3.0           |

(11) ANTENNA CHARACTERISTICS. - For optimum performance, an antenna having a 50 ohm, unbalanced termination is required. For antennas other than 50 ohms, an antenna trimming circuit is provided.

ORIGINAL 1-3

#### 1-4. EQUIPMENT LISTS.

- a. EQUIPMENT SUPPLIED. Table 1-1 lists the names, quantities, dimensions, and weights of all equipment supplied with the receiver.

- b. EQUIPMENT REQUIRED BUT NOT SUPPLIED. Table 1-2 lists the equipment required for operation of the receiver but not supplied.

- c. SHIPPING DATA. Table 1-3 lists the contents, dimensions, volume, and weight of the receiver complement prepared for shipment. The complete equipment is packed for shipment in one box.

TABLE 1-1. EQUIPMENT SUPPLIED

| QTY           | NOMENCLATURE              |               | DIM     | ENSIONS (I | IN.)    | VOL     | WT     |

|---------------|---------------------------|---------------|---------|------------|---------|---------|--------|

| PER<br>EQUIP. | NAME                      | DESIG         | н       | w          | D       | (CU FT) | (LB)   |

| 1             | Radio Receiving<br>Set    | AN/GRR-17     | 11-3/32 | 19-3/32    | 13-7/16 | 1.628   | 53.600 |

|               | Radio Receiver            | R-1490/GRR-17 | 7-15/16 | 16-15/16   | 12-1/8  | 0.938   | 43.600 |

|               | Transit Case              | D43611-G1     | 11-3/32 | 19-3/32    | 12-7/16 | 1.628   | 10.000 |

| 1             | Antenna Adapter           | A43787-1      |         |            |         |         |        |

| 1             | Power Cable<br>(AC)       | C44486-G1     |         |            |         |         |        |

| 1             | Power Cable (DC)          | C44487-G1     |         |            |         |         |        |

| 1             | Connector,<br>Coaxial, RF | UG-21H/U      |         |            |         |         |        |

TABLE 1-2. EQUIPMENT REQUIRED BUT NOT SUPPLIED

| QTY           | NOMENCLATURE     |              |                   | REQUIRED             |  |

|---------------|------------------|--------------|-------------------|----------------------|--|

| PER<br>EQUIP. | NAME             | DESIG        | USE               | CHARACTER-<br>ISTICS |  |

| 2             | Technical Manual | TM-05866A-15 |                   |                      |  |

| 1             | Headset          | NT-49985-A   | Monitor output    | 600 ohms             |  |

| 1             | Antenna          | None         | Supply rf signals | 50 ohms              |  |

| 1             | Cable, Coaxial   | RG8A/U       | Antenna cable     | 50 ohms              |  |

| 1             | Card Puller      | C44941G1     | Remove p/c cards  |                      |  |

| 2             | Card Extender    | D43031G1, 2  | Extend p/c cards  |                      |  |

TABLE 1-2. EQUIPMENT REQUIRED BUT NOT SUPPLIED (Cont)

|            |                                             |          | <del></del>                     | <del></del>            |

|------------|---------------------------------------------|----------|---------------------------------|------------------------|

| QTY<br>PER | NOMENCLATURE                                |          | USE                             | REQUIRED<br>CHARACTER- |

| EQUIP.     | NAME                                        | DESIG    | ODE                             | ISTICS                 |

| 1          | Cable, Module<br>Extender                   | C44944G1 | Extend modules                  |                        |

| 1          | Cable, Power<br>Supply<br>Extender          | C44943G1 | Extend power supply             |                        |

| 1          | Cable, Intelli-<br>gence Filter<br>Extender | C44942G1 | Extend intelli-<br>gence filter |                        |

#### TABLE 1-3. SHIPPING DATA

| вох | COMMENIAC                                                     | DIMENSIONS (IN.) |    | VOL    | WT      |      |

|-----|---------------------------------------------------------------|------------------|----|--------|---------|------|

| NO. | CONTENTS                                                      | Н                | w  | D      | (CU FT) | (LB) |

| 1   | RADIO RECEIVING SET AN/GRR-17 with cables and antenna adapter | 16-7/8           | 24 | 17-7/8 | 4.2     | 64   |

#### WARNING

Transit Case C43611-G1 is equipped with a pressure relief valve to permit safe transportation by aircraft. Valve MUST be opened (turned fully counterclockwise) prior to shipment, whether set is packed or unpacked.

#### SECTION 2

#### INSTALLATION

#### 2-1. UNPACKING AND HANDLING.

- a. DESCRIPTION OF PACKAGING AND PACKING METHODS. Radio Receiver R-1490/GRR-17 and accessories are packed for shipment in a cardboard box packaged as follows:

- (1) The receiver and power cables assembled in the transit case are contained in a carton. End spacers in the carton contain bags of dessicant dehumidifier. A waterproof vaporproof barrier surrounds the receiver carton. This package is surrounded by an outer carton.

- b. UNPACKING INSTRUCTIONS.

- (1) Observe the markings on the cardboard box and place it on a flat surface with the top up.

- (2) Open the outer carton.

- (3) Cut open the waterproof liner.

- (4) Open the inner carton and remove contents.

- (5) Check the contents against the list in table 1-1.

- c. HANDLING. Normal precautions for lifting and transporting electronic equipment should be observed when handling the receiver. It may be lifted by the transit case carrying handles or the panel handles.

- d. TRANSIT CASE VALVE. The transit case is equipped with a pressure relief valve, located near the right-hand handle, to permit safe transportation by aircraft. After unpacking, for field service with case installed, close valve by turning fully clockwise to retain waterproof feature of the case.

- e. MECHANICAL INSPECTION. Directly following unpacking and before installation, inspect the receiver to detect any damage or disarrangement which may have occurred during shipment. A check of the following items may avoid much inconvenience during installation and initial equipment operation.

- (1) Check for nuts, washers, or other foreign particles which may be lodged where they could cause a short circuit.

- (2) Tighten any screws or nuts on mechanical assemblies which may have worked loose.

- (3) Look for broken wires or loose cable connections.

- (4) Operate all mechanical controls through their full range of travel to detect jammed controls, bent control shafts, or other evidence of mechanical damage.

- (5) See that all plug-in modules and cable connectors are well seated in their sockets. Check that fuses AlAlFl through AlAlF5 are in place in the fuse holders on the panel.

## 2-2. POWER REQUIREMENTS AND DISTRIBUTION. (See figure 2-1.)

- a. REQUIREMENTS. The receiver will operate normally from either an ac or a dc primary power source. Ac power requirements are 115 volts ac  $(\pm 10\%)$ , 50 to 400 cps  $(\pm 5\%)$ , single phase. Dc power requirements are 24 volts dc  $(\pm 15\%)$ . Voltage and frequencies should not exceed the tolerances established.

- b. PRIMARY POWER CONNECTIONS. Primary power connection to the receiver requires the attachment of a 6-foot cable which is supplied with the receiver. Table 2-1 lists the cables and connectors required for all external cables not supplied with the receiver.

- c. DISTRIBUTION. The primary power distribution diagram (see figure 5-52) illustrates the distribution of the ac or dc primary power within the receiver. AC primary power from the 115 V AC connector AlAlJ3 on the receiver panel passes through fuses AlAlF1 and AlAlF2, one section of POWER switch AlAlS1, and is applied to the power transformer in the power supply module AlA3PS1. DC primary power from the 24 V AC connector AlAlJ4 on the panel passes through fuses AlAlF4 and AlAlF5, through a diode polarity gate AlAlCR2 and one section

Figure 2-1. External Cable Connections

of POWER switch AlAlS1, and is applied to the output of the ac power supply circuit. The ac and dc power fuses as well as spare fuses are located on the receiver front panel.

## 2-3. INSTALLATION LAYOUT. (See figure 2-2.)

Radio Receiver R-1490/GRR-17 is designed for general field operation with the transit case cover only removed, or installation in a standard relay rack following removal of the entire transit case. When not installed in a relay rack, it is suggested that the transit case itself be left in place to provide maximum protection for the receiver assembly from physical damage. In selecting a suitable location for the receiver, the following factors should be considered:

- a. POWER SOURCE. The power source described in paragraph 2-2a must be available at the location.

- b. CABLE LENGTHS. Most external cable lengths to and from the receiver are not critical but the transmission line from the antenna should be as short as possible.

#### CAUTION

When operating from a 24 volt dc power source, note that the load current value is from 1 to 1.45 amperes. If a long power cable is required, make sure the voltage at the receiver terminals is not less than 20.4 volts dc; otherwise, receiver operation will be impaired.

- c. SERVICE ACCESS. The transit case and dust cover must be removed prior to servicing the receiver to expose the plug-in modules. Because all external cables terminate at the front panel, no special considerations are required when mounting the receiver to assure clearance for cable removal or replacement.

- d. TEMPERATURE AND VENTILATION. The receiver dissipates heat at a low rate of approximately 2.85 BTU per minute. The use of solid state circuit modules, combined with the heat conduction and dissipation ability of the chassis and panel structures, limit the receiver temperature rise to 15°C (59°F) above the ambient temperature at the receiver location. The receiver will operate normally at ambient temperatures ranging from -40°C (-40°F) to +65°C (+149°F).

- e. INTERACTION WITH OTHER EQUIPMENT. A principal feature of the receiver is its ability to operate in an environment close to transmitting facilities. Internal shielding and effective filtering reduce the possibility of interaction with other communication equipment.

- f. OPERATION WITH AUXILIARY EQUIPMENT. Installation planning should consider the relative locations of auxiliary equipment, such as teletype printers, with which the receiver will be used.

#### 2-4. INSTALLATION REQUIREMENTS.

Field installation of Radio Receiver R-1490/GRR-17 consists of removing the transit case cover, attaching it to the rear of the transit case for storage, and making the necessary external cable connections at the front panel. Relay rack installation requires removal of the transit case, mounting the receiver in the rack,

ORIGINAL 2-3

Figure 2-2. Radio Receiver R-1490/GRR-17, Outline Lrawing

and the completion of all external cable connections. Initial operating tests (see paragraph 2-5) are performed immediately following an installation to establish normal receiver operation and assure optimum performance, prior to releasing the receiver to operating personnel. Power cables are stored in the transit case cover.

- a. REMOVING AND REPLACING THE TRANSIT CASE. The following procedure is used to remove the transit case, preparatory to relay rack installation, and to replace the transit case when the receiver is removed from the rack.

- (1) REMOVING THE CASE. (See figure 2-2.)

- (a) Release the cover fasteners and remove the cover. Store the cover at the case rear using the elastic cords provided on the cover.

- (b) Release the two captive securing screws at the case rear and loosen the eight captive finger-type screws at the receiver panel.

- (c) Withdraw the receiver from the transit case.

- (2) REPLACING THE CASE.

- (a) Insert the receiver into the case along the shelf.

- (b) Tighten the panel and case retaining screws.

- b. RELAY RACK INSTALLATION. The receiver front-panel section is equipped with two hinged flanges, one at each side of the panel which when folded outward support the receiver in a standard relay rack. Preliminary to a relay rack installation, remove the transit case and its cover following the procedure described in paragraph 2-4a.

- (1) Swing out the hinged flanges parallel with the receiver panel. A detent mechanism will engage when the flanges are in line with the panel.

- (2) Position the receiver at the relay rack and secure the two flanges using four 1/2 inch, 10-32, fillister-head machine screws. Place a washer beneath the head of each screw.

- (3) Attach an earth ground connection to the binding post directly below the  $50\Omega$  ANT connector on the front panel.

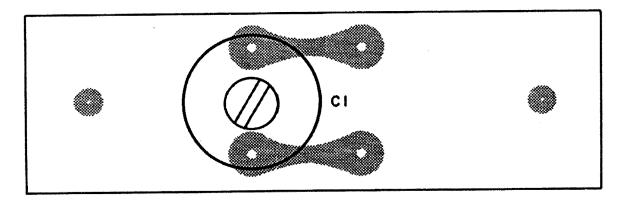

- c. EXTERNAL CABLES. External primary power cables six feet long are supplied with the receiver. Because of variations in installation requirements, the cable for the antenna connection is not supplied. However, a mating connector is supplied for this connection. Table 2-1 contains a summary of the cable types required and identifies each connector and its mating receptacle. Figure 2-3 shows the method of assembling a connector to form an external cable for the  $50\Omega$  ANT panel receptacle. Detailed instructions for the assembly of electrical connectors are contained in NAVSHIPS 900,171, Chapters 5 and 6.

- d. MAKING EXTERNAL CONNECTIONS. Figure 2-1 shows the location of all external connections at the receiver front panel. To complete the external connections, proceed as follows:

ORIGINAL 2-5

Figure 2-3. Antenna Cable, Connector Assembly

(1) For ac operation, connect one end of the ac power cable (supplied) to receptacle AlAlJ3, labelled 115 V AC. Connect the other cable end to the local primary power source. (See paragraph 2-2a for the power requirements.)

TABLE 2-1. CONNECTORS SUPPLIED AND EXTERNAL CABLE REQUIREMENTS

| CIRCUIT<br>WHERE USED                          | TYPE<br>CABLE | EQUIPMENT<br>RECEPTACLE | CABLE<br>CONNECTOR |

|------------------------------------------------|---------------|-------------------------|--------------------|

| Antenna transmission line, 50 ohm termination. | RG-8/U        | UG-556B/U               | UG-21H/U           |

| Teletype output signal line.                   | Not specified | FSN-5940-<br>351-6993   | None               |

(2) For dc operation, connect one end of the dc power cable (supplied) to receptacle AlAlJ4, labelled 24 V DC. Connect other cable end to the local dc primary power source. Observe polarity. (See paragraph 2-2a for power required.)

#### CAUTION

Inadvertent connection of the ac power cable to a dc primary power source, and vice versa, will cause the panel fuse to blow and may damage the equipment.

- (3) Connect the antenna transmission line at receptacle AlAlJl,  $50\Omega$  ANT. (An antenna post adapter is provided for long-wire antennas.)

- (4) Connect teletype equipment to the two terminals labelled TELETYPE. Observe terminal polarity. The positive lead <u>must</u> be attached to the upper terminal marked (+). Connect (-) lead to teletype equipment ground. If the teletype unit which is used supplies its own loop potential, place the MODE, INT BAT/EXT BAT switch at EXT BAT. In this position, the receiver teletype output provides contact closure for external loop potentials up to 120 volts, 60 ma. If the teletype unit used does not supply its own loop potential, place the MODE, INT BAT/EXT BAT switch at INT BAT. In this position, the receiver TTY power supply delivers 120 volts at 60 ma in series with the TELETYPE terminals. Refer to the applicable technical manual for the teletypewriter equipment used.

#### 2-5. INITIAL OPERATING TESTS.

- a. GENERAL. After the receiver is installed and before turning it over to operating personnel, observe the receiver performance in detail and make any necessary circuit adjustments. All operating aspects and features of the receiver should be checked during the initial operating checks with particular attention paid to any condition noted which could lead to abnormal performance.

- b. INITIALLY ENERGIZING RECEIVER. The location of each panel control is shown in figure 3-1, and table 3-2 gives a brief description of the control

ORIGINAL 2-7

functions and indicates their preset positions. To initially energize the receiver, perform the following steps in the order presented.

- (1) Make sure that all cable connections at the panel are secure.

- (2) Verify that the receiver is connected to the correct primary power source described in paragraph 2-2a.

- (3) Preset all panel controls according to table 3-2.

- (4) Place external primary switches on at the installation site.

- (5) Set the POWER switch to AC (for an ac power source) or to DC (for a dc power source).

- (6) Press the PUSH FOR DIAL LIGHTS panel switch and observe that the MEGACYCLES dial windows are illuminated. Release the switch.

- (7) During tests, use the SPEAKER LEVEL or the PHONE LEVEL controls to adjust the speaker or headset volume levels, respectively.

- c. TUNING PERFORMANCE. To test receiver performance, use a signal generator (Signal Generator AN/URM-25 or equivalent) or actual transmitted signals. Because the tuning accuracy of the receiver exceeds that of most signal generators, use the receiver or a primary frequency standard to calibrate the generator. The receiver tuning performance is evaluated by setting the generator frequency and the MEGACYCLES tuning dials for reception of six test frequencies, selected to verify operation of the six antenna input filters (A1A2A1) as well as the operating ranges of the synthesizer circuits. It is unnecessary to test the continuous tuning (frequency vernier) circuit at more than one frequency.

- (1) INCREMENTAL TUNING. A complete tuning procedure for the receiver is described in Section 3, Operation. Main points from this procedure have been selected for the following tuning performance tests, using the SSB reception mode.

- (a) Connect the signal generator to the  $50\Omega$  ANT connector (AlAlJ1). Adjust generator for a 2.5000 mc, 10 microvolt, unmodulated test signal.

- (b) Set the MODE switch at SSB, and the BANDWIDTH switch at LSB.

- (c) Tune the receiver to 2.5010 mc by setting the MEGACYCLES tuning dials to read 02.5010.

- (d) The signal level meter on the panel should indicate and a 1000 cycle tone should be heard in the speaker.

- (e) Repeat steps (b) and (c) with signal generator test frequencies 4.0000, 6.5000, 10.0000, 15.5000, and 24.5000 mc. Tune the receiver 1 kc above the generator frequency for each frequency test listed.

- (2) CONTINUOUS TUNING. To receive a signal whose frequency does not terminate in whole 100-cycle increments (for example, a frequency of 2.00005 mc), the continuous tuning method is employed using the FREQ VERNIER ±150

CPS panel control. The dual control, with the switch knob at VAR, will provide continuous receiver tuning of more than 150 cycles above and below the MEGA-CYCLES dials set frequency. Refer to Section 3, Operation, for a complete description of the continuous tuning procedure.

- (a) Adjust the generator for a 2.500050 mc, 10 microvolt, unmodulated test signal.

- (b) Set the MODE switch at SSB, and the BANDWIDTH switch at LSB.

- (c) Set the MEGACYCLES dials to read 2.5010 mc.

- (d) Set the large FREQ VERNIER ±150 CPS knob at VAR, and adjust the small knob to receive the test frequency.

- (e) The panel meter should indicate presence of a signal, and a 1000 cycle note should be heard in the speaker.

- d. AM MODE OPERATION. Receiver operation for the AM mode should be verified and the agc operation checked by performing the following:

- (1) Connect the signal generator to the  $50\Omega$  ANT connector (AlAlJ1). Adjust generator for a 2.0000 mc, 100 microvolts, test signal, modulated 30 per cent at 400 cycles.

- (2) Set the MODE switch at AM, and the BANDWIDTH switch at 8 KC.

- (3) Set the MEGACYCLES dials to 2.0000 mc.

- (4) The signal level meter on the panel should indicate and a 400 cycle tone should be heard at the speaker.

- (5) Set the METER FUNCTION switch at PHONES LEVEL. Adjust the PHONE LEVEL control for a reading of +5 db on the panel meter using the output level scale.

- (6) Gradually increase the generator output level to 2.0 volts, noting the panel meter reading. The meter reading should change 6 db or less.

- e. CW MODE OPERATION. To check receiver operation using the CW reception mode, perform the following steps:

- (1) Connect signal generator to the 50Ω ANT connector (AlAlJl). Adjust generator for a 2.0000 mc, 10 microvolt, unmodulated test signal.

- (2) Set the MODE switch at CW, and the BANDWIDTH switch at 8 KC.

- (3) Set the large BFO ±3 KC knob at VAR and adjust the small knob.

- (4) Note the beat-note heard in the speaker. A zero-beat should occur at a central position of the small control knob.

- f. FSK MODE OPERATION. To verify receiver operation using the FSK mode, connect a teletype unit to the TELETYPE terminals on the receiver panel.

If Teletypewriter Set AN/TGC-14A(V) or similar equipment which supplies its own loop potential is used, place the TELETYPE MODE switch in the EXT BAT position. If a teletype unit which does not supply its own loop potential is used, place the TELETYPE MODE switch in the INT BAT position. Select a known broadcast station employing two-tone fsk transmissions for the set.

#### Note

When using Teletypewriter Set AN/TGC-14A(V), connect terminal box ground lead to (-) TELETYPE terminal on receiver panel.

- (1) Set the MODE switch at FSK, and the BANDWIDTH to USB or LSB depending upon the received signal characteristics.

- (2) Energize the auxiliary teletypewriter equipment (refer to instructions for the equipment).

- (3) Set the MEGACYCLES dials to receive the transmitter fsk channel.

- (4) Note the teletypewriter copy as a function of receiver operation.

- g. MONITORING WITH HEADPHONES. To verify operation of the head-phone monitoring circuit, plug a headphone set into the PHONES jack and repeat the previous performance step of paragraph 2-5d. Note that the PHONE LEVEL control will adjust the level of volume at the headphones.

- h. OPERATION OF SPECIAL CIRCUITS. The noise blanking and notch filter circuits in the receiver are considered special circuits. While not essential for reception, they are provided as a supplement to enhance receiver performance. Tests of these circuits consist of operating the controls and observing the degree to which the circuit performs its intended function.

- (1) NOISE BLANKING. The noise blanking circuit (module A1A2A4) employs a gated amplifier stage in the main signal path to effectively open (blank) the signal circuit when a noise impulse is received. To test the noise blanking circuit, tune the receiver to a particularly noisy portion of the tuning range where impulse type noise exists, and monitor the noise using the loudspeaker. Rotate the NOISE BLANKING control in a clockwise direction and note an appreciable drop in the noise level. If an am or cw transmission is received, operation of the noise blanking circuit is evident by a distortion of the signal.